Fターム[5F083ZA15]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリと独立機能ブロック (1,941) | メモリ+(ゲートアレイ、マスタスライス) (127)

Fターム[5F083ZA15]に分類される特許

101 - 120 / 127

FNトンネル及び感知デバイスをもつ不揮発性の再プログラム可能な相互接続セル

【課題】FPGAセル及びアレー構造体の相互接続部を選択的にプログラムする方法を提供する。

【解決手段】各セルは、フローティングゲートが共通で且つ制御ゲートが共通であるスイッチ用フローティングゲート電界効果トランジスタ及び感知用フローティングゲート電界効果トランジスタを備えている。セルのプログラミングは、共通の制御ゲートラインと、感知トランジスタのソース/ドレインとをバイアスする電圧により行われる。

(もっと読む)

プログラマブル素子及びそのプログラマブル素子を有する半導体装置の製造方法。

【課題】 プログラム特性の良好なプログラマブル素子及びそのプログラマブル素子を有する半導体装置の製造方法を提供することを目的とする。

【解決手段】 半導体基板100と、半導体基板100表面に離間して形成されたソース/ドレイン層103と、ソース/ドレイン層103間の半導体基板100上に形成されたHfを含有する電荷トラップ膜を有するゲート絶縁膜105と、ゲート絶縁膜105上に形成されたプログラム電位が印加されるゲート電極106を備えることによって、FPGA等のプログラマブルロジックデバイスに使用されるプログラマブル素子のプログラム特性を向上する。

(もっと読む)

ゲート電極下に金属シリサイドのパイプを有する電気ヒューズ

【課題】 信頼性が向上しているとともに比較的低い電圧でプログラムされることが可能な電気ヒューズを提供する。

【解決手段】 電気ヒューズは、半導体基板と、導電性または一部導電性のポリシリコンを具備するゲートと、を具備する。半導体基板はゲートの近くにおいてアモルファス化されたパイプ領域を具備するとともにパイプ領域に隣接する第1、第2電極領域を具備する。電気ヒューズは、第1、第2電極領域内の半導体基板上の金属シリサイド層をさらに具備する。金属シリサイドは、ニッケル・シリサイド、コバルト・シリサイド、チタン・シリサイド、パラジウム・シリサイド、プラチナ・シリサイド、エルビウム・シリサイド、およびこれらの組合せからなる群から選択される。

(もっと読む)

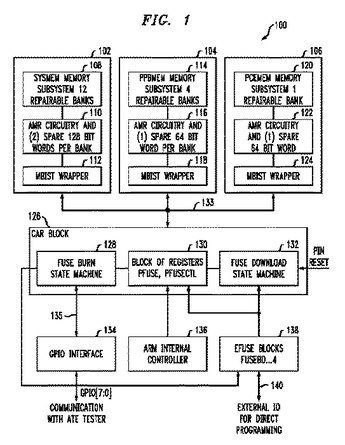

ヒューズ焼付け状態機械及びヒューズダウンロード状態機械に基づく内蔵メモリ修理方法

内蔵メモリ内の1以上の不良を修理するためのメモリ修理回路は少なくとも1つのヒューズレジスタ及び当該ヒューズレジスタに結合された状態機械回路を含む。状態機械回路は、(i)内蔵メモリ内の1以上の不良に関するステータス情報を受信し、(ii)ステータス情報に基づいてメモリが修理可能かを判断し、(iii)メモリが修理可能であるとみなされるときは、メモリの不良メモリセルに対応するアドレスを記憶し、(iv)メモリ修理回路に供給された電圧源を用いて、不良メモリセルに対応するアドレスをヒューズレジスタに焼き付け、及び(v)不良メモリセルに対応するアドレスがヒューズレジスタに焼き付けられたことを確認するように動作する第1の状態機械を実装する状態機械回路を備える。状態機械回路がさらに、(i)少なくとも1つのヒューズレジスタに記憶された情報を内蔵メモリに関連する少なくとも1つの修理レジスタにダウンロードし、及び(ii)アドレスが内蔵メモリ内の不良メモリ部分に対応する回路で受信されると、不良メモリ部分へのアクセスを少なくとも1つの修理レジスタに再ルーティングするように動作する第2の状態機械を実装する。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】書き込み時の消費電力が小さく、読み出し専用の記憶装置のメモリ素子に用いられるアンチヒューズを提供する。

【解決手段】アンチヒューズは、第1導電層11と、第1導電層11上に非晶質シリコン膜13と絶縁膜14とを交互に積層した2層以上の多層膜20と、多層膜20上に第2導電層12を有する。第1導電層11と第2導電層12の間に電圧を印加して、多層膜20の抵抗を低下させることで、メモリ素子にデータを書き込む。第1導電層11と第2導電層12の間に非晶質シリコン13よりも抵抗が高い絶縁膜14を形成することで、書き込み時にアンチヒューズに流れる電流が低減される。

(もっと読む)

情報処理方法

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

プロセスばらつき耐性メモリ設計

プロセスばらつき耐性メモリを設計するための方法及びシステムが開示される。メモリ回路が機能ブロックに分割される。前記機能ブロックの各々に関して統計的分布が計算される。次に、各ブロックの前記分布が結合されて前記回路の信頼性が検証される。前記信頼性は、前記回路が予め決められた歩留まりを満たす場合に検証される。 (もっと読む)

半導体装置

【課題】配線層のみの変更によって、1つのメモリセルアレイから任意のワード・ビット構成の複数のメモリを生成することが可能な半導体装置を提供する。

【解決手段】半導体基板10内には、少なくともワード線を除き、複数のメモリセルがロウ及びカラムに配置されたメモリセルアレイ11と、選択されたメモリセルのデータを読み込むセンスアンプ12と、選択された前記メモリセルにデータを書き込むライトバッファ13と、書き込みデータ又は読み出しデータを受ける入出力回路14と、メモリセルアレイのロウ方向の分割数と少なくとも同数個配置された複数のワード線ドライバ15−1〜15−4と、ワード線ドライバの数と同数個のアドレスデコーダ16−1〜16−4が配置されている。複数のワード線ドライバ15−1〜15−4のそれぞれと、メモリセルアレイのロウに配置された複数のメモリセルは複数のワード線により接続される。

(もっと読む)

垂直配向ナノロッドを持つ低リークDRAMメモリセルとその製造方法

半導体メモリストレージセルにおいてリーク電流を減らすための方法と構造が記載される。垂直配向ナノロッド(403)が、アクセストランジスタ(400)のチャネル領域で使用され得る。ナノロッドの直径は、アクセストランジスタのチャネル領域内の電子バンドギャップエネルギーの増加を引き起こすために十分小さくすることができ、これはオフ状態でのチャネルリーク電流を制限するように機能し得る。様々な実施形態では、アクセストランジスタは両面キャパシタ(425)に電気的に結合し得る。本発明の実施形態に従うメモリデバイス、およびそのようなデバイスを含むシステムもまた開示される。  (もっと読む)

(もっと読む)

スケーリング可能な組み込みDRAMアレイ

第1のプロセスから第2のプロセスに組み込みDRAMアレイをスケーリングするための方法及び装置であって、スケーリングは一定のスケールファクタでフィーチャの直線寸法を縮小することを含む。第1のプロセスから第2のプロセスへと、DRAMセルキャパシタの配置面積はスケールファクタの2乗で減少し、セル容量はスケールファクタで減少する。ロジックトランジスタに供給するために利用される電圧は、第1のプロセスから第2のプロセスにスケールダウンされる。しかしながら、センスアンプに供給するために利用される電圧はどちらのプロセスも変わらない。従って、第2のプロセスの組み込みDRAMアレイにおいては、センスアンプはロジックトランジスタより大きな電圧を供給される。これにより、一つのプロセス世代から次の世代にわたってDRAMセルの検出電圧を維持しながら、メモリサイズをプロセスのスケールファクタの2乗でスケーリングすることが可能になる。  (もっと読む)

(もっと読む)

マルチレベル受動素子メモリセルアレイを読出す方法および機器

4レベルの受動素子セルは低下する抵抗レベルに対応するメモリ状態を有し、それはデータ状態11、01、00および10に好ましくはそれぞれマップされる。LSBおよびMSBは異なるページの一部として好ましくはマップされる。メモリセル状態を区別するために、選択されたビット線電流は、基準電流レベルおよび読出バイアス電圧の少なくとも2つの異なる組合わせについて検知される。中間レベルの基準はLSBを読出すために用いられる。MSBを読出すとき、10から00データ状態の間の第1の基準および01から11データ状態の間の第2の基準が用いられてもよく、中間レベルの基準を用いる必要はない。一定の実施例では、ビット線電流は、ビット線電流を異なる値に安定させるための遅延を必要とすることなく、同時に第1および第2の基準に比較され、これにしたがってMSBが生成される。  (もっと読む)

(もっと読む)

半導体集積回路装置、デジタルカメラ、デジタルビデオカメラ、コンピュータシステム、携帯コンピュータシステム、論理可変LSI装置、ICカード、ナビゲーションシステム、ロボット、画像表示装置、光ディスク記憶装置

【課題】 ある程度の小さいメモリセルを実現しつつ、プレート線を共有化でき、且つメモリセルの直列接続による遅延を無くして高速動作が可能な半導体集積回路装置を提供する。

【解決手段】 半導体集積回路装置は、それぞれが、ゲート端子をワード線と接続されたセルトランジスタQ0〜Q3と、セルトランジスタのソース端子に一端を接続された強誘電体キャパシタC0〜C3と、を具備する複数の第1メモリセルを具備する。複数の第1メモリセルのそれぞれのセルトランジスタのドレイン端子を第1ローカルビット線LBLとし且つそれぞれの強誘電体キャパシタの他端を第1プレート線PLとして、第1リセットトランジスタは、ソース端子を第1プレート線と接続され、且つドレイン端子を第1ローカルビット線と接続される。第1ブロック選択トランジスタQSは、ソース端子を第1ローカルビット線と接続され、且つドレイン端子を第1ビット線と接続される。

(もっと読む)

半導体集積回路装置、デジタルカメラ、デジタルビデオカメラ、コンピュータシステム、携帯コンピュータシステム、論理可変LSI装置、ICカード、ナビゲーションシステム、ロボット、画像表示装置、光ディスク記憶装置

【課題】ある程度の小さいメモリセルを実現しつつ、プレート線を共有化でき、且つメモリセルの直列接続による遅延を無くして高速動作が可能な半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、それぞれが、ゲート端子をワード線と接続されたセルトランジスタQ0〜Q3と、セルトランジスタのソース端子に一端を接続された強誘電体キャパシタC0〜C3と、を具備する複数の第1メモリセルを具備する。複数の第1メモリセルのそれぞれのセルトランジスタのドレイン端子を第1ローカルビット線LBLとし且つそれぞれの強誘電体キャパシタの他端を第1プレート線PLとして、第1リセットトランジスタは、ソース端子を第1プレート線と接続され、且つドレイン端子を第1ローカルビット線と接続される。第1ブロック選択トランジスタQSは、ソース端子を第1ローカルビット線と接続され、且つドレイン端子を第1ビット線と接続される。

(もっと読む)

CMOS論理プロセス内の不揮発性メモリ及びその動作方法

【課題】 本発明は、如何なる処理ステップの変更もせずに従来の論理プロセスを用いて製作できる不揮発性メモリセルを提供する。

【解決手段】 半導体基板上に製作された不揮発性メモリ(NVM)セルであって、浮遊ゲート電極(少なくとも部分的にNVMセルの全ての活性領域の上に延在する)を含むNVMセルを提供する。NVMセルは、第1のn型領域に位置するPMOSアクセストランジスタと、(第1のn型領域から分離されている)第2のn型領域に位置するPMOS制御キャパシタと、p型領域に位置するNMOSプログラミングトランジスタとを含む。浮遊ゲート電極は、PMOSアクセストランジスタ、PMOS制御キャパシタ及びNMOSプログラミングトランジスタの活性領域の上に延在する連続的な電極である。このNVMセルを用いてアレイをインプリメントするための種々のアレイ接続が提供される。PMOSアクセストランジスタ及びNMOSプログラミングトランジスタは、代替的な実施形態において、NMOSアクセストランジスタ及びPMOS消去トランジスタにそれぞれ置き換えられる。

(もっと読む)

集積回路装置及び電子機器

【課題】 複数のビット線出力をその出力配列順に従って処理するという制約なしに、回路の配置を柔軟に行え、効率の良いレイアウトが可能な集積回路装置を提供すること。

【解決手段】 集積回路装置20は、複数のワード線WL、複数のビット線BL及び複数のメモリセルMCを有するメモリセルアレイ312と、メモリ出力回路320とを有するデータメモリを備えている。メモリセルアレイ312での複数のビット線BLの配列に従ったデータ読出し配列順序(2画素分R<1>,R<1>,G<1>,…,<R0>)と、メモリ出力回路320からのデータ出力配列順序(2画素分R<0>,B<0>,G<0>,R<1>,…R<0>)とが異なっている。メモリ出力回路320の領域に並べ替え配線領域410を有し、並べ替え配線領域410は、データ読み出し配列順序で入力されたデータを配線ALB,ALCにより並べ替えて、データ出力配列順序で出力する。

(もっと読む)

集積回路装置及び電子機器

【課題】回路面積の縮小や設計の効率化を実現できる集積回路装置、電子機器の提供。

【解決手段】集積回路装置は、集積回路装置の短辺である第1の辺から対向する第3の辺へと向かう方向を第1の方向D1とし、集積回路装置の長辺である第2の辺から対向する第4の辺へと向かう方向を第2の方向D2とした場合に、D1方向に沿って配置される第1〜第Nの回路ブロックCB1〜CBNを含む。回路ブロックCB1〜CBNは、階調特性の調整データの設定を行うロジック回路ブロックLBと、設定された調整データに基づいて階調電圧を生成する階調電圧生成回路ブロックGBを含む。階調電圧生成回路ブロックGBとロジック回路ブロックLBは、D1方向に沿って隣接して配置される。

(もっと読む)

半導体装置

【課題】半導体装置の小型化、信号伝播速度のロスを防止すると共に、オーバーヘッドの増大防止を図った半導体装置を提供すること。

【解決手段】一つの配線チップ10上に配設される記憶装置チップ20を点在させることなく、メモリ22として独立した記憶領域を持つ同一な大きさの複数の小メモリ23を集合させ、それぞれに独立したメモリ機能を持たせたので、半導体装置の小型化、信号伝播速度をロス防止が効率よく図れる。そして、メモリ22(メモリ集合体)の各々の小メモリ23を独立した記憶領域で同一な大きさとしているため、共通して制御することができる制御回路(BIST回路24やリタンダシー回路25)を共通回路として配設することができ、SOC(シリコン・オン・チップ)のように個々の記憶容量の異なる小メモリに対して制御回路を設ける場合に比べ、メモリセルアレイに対するオーバーヘッドを少なくすることができる。

(もっと読む)

ゲート降伏現象を用いた3.5トランジスタ不揮発性メモリセル

【課題】CMOSロジックプロセスを用いる不揮発性プログラム可能メモリセルを提供する。

【解決手段】 カラムビット線およびロウワード線を有するメモリアレイ中で用いられるように形成されたプログラム可能メモリセルが開示される。このメモリセルは、ゲートをプログラムワード線WPと接続された降伏トランジスタM0と、降伏トランジスタとセンスノードで直列に接続された書き込みトランジスタM1と、を具備する。書き込みトランジスタのゲートは、書き込みワード線WWと接続される。さらに、第1センストランジスタM2は、ゲートをセンスノードと接続される。第2センストランジスタM3は、第1センストランジスタと直列に接続され、ゲートを読み出しワード線Wrと接続される。第2センストランジスタはソースをカラムビット線BLと接続される。

(もっと読む)

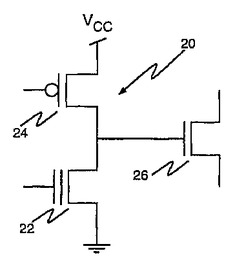

プログラマブルロジックアレイ用不揮発性プログラマブルメモリセル

プログラマブルロジックアレイに用いるために適した不揮発性プログラマブルメモリセルは、第2導電型の揮発性MOSトランジスタ24と直列に、第1導電型の不揮発性MOSトランジスタ22を具備する。不揮発性MOSトランジスタ22は、フラッシュトランジスタのようなフローティングゲートトランジスタであるか、又はフローティング電荷トラッピングSONOS、MONOSトランジスタ、若しくはナノ結晶トランジスタのような別のタイプの不揮発性トランジスタであってもよい。揮発性MOSトランジスタ、インバータ、又はバッファ26は、そのゲート又は入力を、不揮発性MOSトランジスタ22と揮発性MOSトランジスタ24との間のコモン接続点に接続することによって駆動される。  (もっと読む)

(もっと読む)

埋め込みFeRAM基盤のRFIDを有する集積回路

集積回路(IC)100は、予め定められた動作を行うように構成された高静電容量固体回路領域、データを格納するFeRAMブロック104、及びICを無線で識別する外部的に提供された固有IDをRFIDブロックに伝達するように構成されたインタフェースユニットを備え、固有IDは、FeRAMブロックに格納される。ICは、ICの予め定められた領域を通して延長される導電性トレースを更に備え、導電性トレースは、RFIDブロックに対するアンテナとして構成され、ここで、RFIDブロックは、情報を受信し、アンテナを介して外部ソースに情報を伝達するように構成される。  (もっと読む)

(もっと読む)

101 - 120 / 127

[ Back to top ]