Fターム[5F083ZA15]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリと独立機能ブロック (1,941) | メモリ+(ゲートアレイ、マスタスライス) (127)

Fターム[5F083ZA15]に分類される特許

121 - 127 / 127

半導体集積回路装置

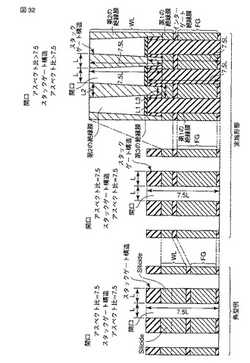

【課題】ワード線の抵抗値の増大を抑制しつつ、メモリセルトランジスタの集積度を高めることができ、かつ、微細加工性に優れた不揮発性半導体記憶装置を提供すること。

【解決手段】制御ゲート(WL)は、インターゲート絶縁膜に接する第1の導電膜と、この第1の導電膜に電気的に接続される第2の導電膜と、を含む。第1スタックゲート構造と第2スタックゲート構造との間を絶縁する層間絶縁膜は、浮遊ゲート(FG)間、及び制御ゲート(WL)の一部分間を絶縁する第1の絶縁膜と、制御ゲート(WL)の他部分間を絶縁する第2の絶縁膜と、第1の絶縁膜と第2の絶縁膜との間に設けられ、第1、第2の絶縁膜に対してエッチング選択比をとれる第3の絶縁膜と、を含む。

(もっと読む)

異なるゲート酸化膜の厚さに関する方法および装置

パスゲートトランジスタのための向上されたオン−オフ変化を有する集積回路が、提供される。該集積回路は、コアトランジスタとパスゲートトランジスタとを含むコア領域を含む。コアトランジスタは、第1の厚さと関連付けられたゲート酸化膜を有し、パストランジスタは、第1の厚さよりも小さな厚さと関連付けられたゲート酸化膜を有する。一実施形態において、パスゲートトランジスタのゲート酸化膜のために用いられる材料は、4より大きな誘電率を有し、一方で、コアトランジスタのゲート酸化膜のために用いられる材料は、4以下の誘電率を有する。集積回路を製造するための方法も、提供される。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】メモリセルアレイの微細化、及び高集積化を進展させ易い半導体メモリを含む半導体集積回路装置を提供すること

【解決手段】セルウェル35と、セルウェル35上に形成され、メモリセルエリア11、及びセルウェルコンタクトエリア13を有するメモリセルアレイ3と、メモリセルエリア11に配置された第1配線体(BL、WL、SGD、SGS)と、セルウェルコンタクトエリア13に配置された第2配線体(CPWELL、WL、SGD、SGS)と、を備える。そして、第1配線体のレイアウトパターンと、第2配線体のレイアウトパターンとを同じとする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】0.3μm未満の幅を有する素子分離領域によって電気的に分離された電界効果トランジスタの信頼性を向上させることのできる技術を提供する。

【解決手段】マスクROM領域のゲート長方向に隣接する電界効果トランジスタを電気的に分離する素子分離領域を、その電界効果トランジスタのゲート電極と同時に形成されるフィールドプレート分離によって構成する。これにより、素子分離領域の分離幅を0.3μm未満と相対的に狭くした場合でも、素子分離領域に挟まれた活性領域ACTに発生する応力を相対的に小さくすることができるので、応力を起因とする結晶欠陥の発生が緩和または抑制できて、電界効果トランジスタのソースとドレインとの間に所望しないリーク電流が具合を低減することができる。

(もっと読む)

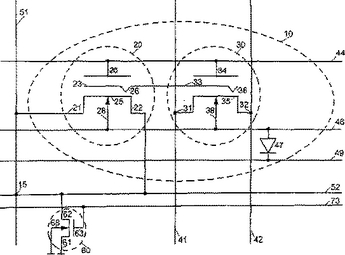

フィールドプログラマブルゲートアレイを構成するためのプログラム可能な相互接続セル

本発明は、制御ゲート電位のノードと、ドレイン、ソース、フローティングゲート、前記制御ゲート電位のノードに接続された制御ゲートを有する第1のフローティングゲートフラッシュメモリトランジスタと、第1のプログラム可能なノードに接続されると共に、第2のプログラム可能なノードに接続されたドレイン、第1のフローティングゲートフラッシュメモリトランジスタのフローティングゲートに接続されたフローティングゲート、制御ゲート電位のノードに接続された制御ゲートを有する第2のフローティングゲートフラッシュメモリトランジスタとを有するプログラム可能な相互接続セル切り替え回路構造を備え、それによって、第1のフローティングゲートフラッシュメモリトランジスタのソースまたはドレインが、プログラム動作の間、セルの外でアースに接続されることを必要とする。  (もっと読む)

(もっと読む)

半導体メモリ装置とそのプログラミング方法

【課題】一つの選択トランジスタ及び8の倍数から構成された相変化可変抵抗素子から形成されたメモリセルを備える半導体メモリ装置の構造と、そのプログラミング方法とを提供する。

【解決手段】相変化メモリセルは、それぞれ、一端が対応するビットラインに連結され、他端が共通で選択トランジスタのドレインに連結され、8の倍数から構成された複数の相変化可変抵抗素子と、ゲートが対応するワードラインに連結され、ソースが基準電圧に連結された選択トランジスタと、を備える複数の相変化メモリセルを備える半導体メモリ装置である。これにより、半導体メモリ装置は、一つのメモリセルが8の倍数個の相変化可変抵抗素子を備えることにより、半導体装置の集積度を高めうる。

(もっと読む)

シングルイベントアップセットに対する抵抗力を増加する集積回路構造

フィールドプログラマブルゲートアレイ(「FPGA」)の集積回路(「IC」)デバイスのコンフィギュレーション・メモリセル(「CRAM」)は、シングルイベントアップセット(「SEU」)に対する増加された抵抗力を与えられる。CRAMの入力ノードのゲート構造の一部分は、そのゲート構造の残りの部分の名目上のサイズに対して、サイズが増加される。拡大されたゲート構造の部位はICのNウェル領域に容量的に近くに配置され、別の部位はICのPウェル領域に容量的に近くに配置される。この配置は、その入力ノードのロジックレベルに関係なく、その入力ノードに、SEUに抵抗するための増加された静電容量を与える。本発明はまた、SEUへの抵抗力を増加させることが所望される任意のタイプのメモリセルの任意のノードに対しても応用可能である。  (もっと読む)

(もっと読む)

121 - 127 / 127

[ Back to top ]