Fターム[5F083ZA15]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリと独立機能ブロック (1,941) | メモリ+(ゲートアレイ、マスタスライス) (127)

Fターム[5F083ZA15]に分類される特許

81 - 100 / 127

メモリ回路におけるリーケージ電流を制限する回路および方法

【課題】スタンバイモードにおける集積回路のリーケージ電流を制限する小型かつ容易に集積できる電流制限回路を実現する。

【解決手段】電流制限回路70はスタンバイモードで動作する間に携帯用無線装置10のメモリ回路24のリーケージ電流を制御する。第1の半導体ウエル64が第2の半導体ウエル66に配置されたメモリ回路24を隔離する。スタンバイモードにおいて、電流制限回路は非導通モードに切り替えられ第2の半導体ウエル64と第1の半導体ウエル66で形成されるダイオードおよび基板62と第2の半導体ウエル64で形成されるダイオードのリーケージ電流を制限する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】不揮発性メモリを備える半導体装置の歩留まりを向上させることの可能な半導体装置の製造方法および方法により得られた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、不揮発性メモリ形成領域のドレイン形成領域側において、ダミーゲート16に対向しない第2ゲート電極14の側壁に形成された第2サイドウォール43のゲート長方向の幅が、ソース形成領域側において、第2ゲート電極14の側壁に形成された第2サイドウォール43のゲート長方向の幅Xよりも長い第2サイドウォール43を得る工程を含む。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】不揮発性記憶素子と、容量素子若しくは抵抗素子とを有するシステムICの製造方法を提供する。

【解決手段】半導体基板の主面の素子分離領域5上に下部電極10cが設けられ、かつ下部電極10c上にONO膜11,12,13からなる誘電体膜を介在して上部電極19cが設けられた容量素子Cを有する半導体集積回路装置であって、半導体基板の主面の素子分離領域5と下部電極10cとの間に耐酸化性膜8、及び下部電極10cと上部電極19cとの間に耐酸化性膜12を有する。

(もっと読む)

半導体記憶装置

【課題】配線層を多層化することなく、第3配線層がユニットセルや基本セルの配線に使用できない領域にゲートアレイを配置して、該領域を有効利用することできる半導体記憶装置を提供する。

【解決手段】積層された3つの配線層を有する半導体記憶装置であって、メモリアレイ領域を第1配線層、第2配線層、及び第3配線層を複数のメモリセルの配線に用いることが可能な領域に形成し、第1配線層、第2配線層、及び第3配線層を複数の基本セルの配線に用いることが可能な領域に第1のゲートアレイ領域を形成し、第1及び第2配線層の2つの配線層を複数のユニットセルの配線に用いることが可能な領域に第2のゲートアレイ領域を形成すると共に、第2のゲートアレイ領域の複数の基本セルを、第3配線層を用いて配設すべき配線を第1配線層を用いて配設するために必要な間隔を隔てて配列する。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】標準ロジックのCMOSプロセスで不揮発性メモリを実現し、キャパシタをコンパクトに配置して面積を最小限にする、不揮発性半導体メモリ素子を提供する。

【解決手段】第1トランジスタT1および第2トランジスタT2を形成するトランジスタ形成部30を上下方向(縦方向)に配置し、このトランジスタ形成部の左側に、メタル配線(ビット線)12を配置し、また、第1トランジスタのゲートのポリシリコン層8と、第2トランジスタのソースに接続されるメタル配線13とを左右方向(横方向)に配置する。またトランジスタ形成部30の左側にn型ウェル2を配置し、このn型ウェル2の表面と第2トランジスタの第2のゲート領域部(符号4で示す領域)とに対向するようにフローティングゲート9を左右方向に配置し、このフローティングゲート9に電位を付与するコントロールゲート配線19も左右方向に配置する。

(もっと読む)

不揮発性メモリならびにその読み出し方法およびその書き込み方法

【課題】高セル密度化と、ビットラインの低抵抗化による高速化が両立し、読み出し、書き込み時の記憶内容への擾乱を受けにくい不揮発性メモリアレイを提供する。

【解決手段】複数のメモリセルは、接続領域411、第1の方向に延びる導電ビット線4010、第2の方向に延びる導電ワード線6030、および導電制御線6010,6020と共に2つの方向に2次元で配置されている。接続領域411は、1つのビット線に接続される4つのセルを含むメモリアレイを通って形成される。接続領域411は、処理を経済的にするために逆導電型領域401と同じ処理ステップで形成する。

(もっと読む)

半導体集積回路

【課題】パッド数の増加によるチップ面積の拡大を抑え、更にプローブカードの共用化により、安価なメモリマクロ混載型半導体集積回路を提供する。

【解決手段】メモリマクロ(DRAM、SRAM、ROM、フラッシュメモリなど)混載型半導体集積回路において、メモリマクロ2上にメモリマクロ検査専用パッド5を配置することによって、通常パッド4の増加を抑え、チップ面積の拡大を抑える。更に、メモリマクロ2上に配置したパッド5の配置位置を同一メモリマクロで固定することにより、メモリマクロを搭載した複数のメモリマクロ混載型半導体集積回路のプローブ検査で用いる1個測定用プローブカードを共用し、安価な検査コストを実現する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】新たなレイアウトパターンを作成せずにNMOSの駆動力を向上することができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置1は、半導体基板100と、第1の導電型の第1の半導体素子が設けられる半導体基板100に形成される第1の半導体素子領域と、第2の導電型の第2の半導体素子が設けられる半導体基板100に形成される第2の半導体素子領域と、第1の半導体素子領域と第2の半導体素子領域とを分離する素子分離領域120とを備え、第1の半導体素子領域は、第1の半導体素子領域に隣接する素子分離領域120より高い位置に形成され、素子分離領域120の表面からの第1の半導体素子領域の表面までの距離が、第1の半導体素子領域の上面視における幅以下である。

(もっと読む)

メモリセル構造、該メモリセル構造を用いたメモリデバイス、及び該メモリデバイスを具備した集積回路

【課題】従来のメモリセルよりも小型かつ長寿命なメモリセルのデザインを提供する。

【解決手段】メモリデバイス用メモリセル構造は、フローティングゲートノードFGを有したリードトランジスタ120と、第1プログラミング端子160を有したトンネリングコンデンサ130と、第2プログラミング端子150を有したカップリングコンデンサスタック200とを具備する。トンネリングコンデンサ130及びカップリングコンデンサスタック200は、FGに接続されている。カップリングコンデンサスタック200は、FGと第2プログラミング端子150との間に直列に接続された少なくとも2つのカップリングコンデンサから成り、トンネリングコンデンサ130よりも大きい静電容量を有する。

(もっと読む)

プログラマブルアンチヒューズトランジスタ及びそのプログラム方法

ゲート端子(12)を備える少なくとも1個のゲート(G)と、ソース端子(14)を備える少なくとも1個のソース(S)と、ドレイン端子(16)を備える少なくとも1個のドレイン(D)と、基板端子(18)を備える少なくとも1個の基板(10)とを備える、プログラマブルアンチヒューズトランジスタ(100)、特に、NチャネルMOSトランジスタ、及び少なくとも1個のそのようなアンチヒューズトランジスタ(100)をプログラムする方法を、能動回路/回路素子をアンチヒューズから著しく離れた場所に位置させる必要がなく、従って、処理ステップを全く追加せずに必要とする面積を最小化するように、更に改良するために、前記ソース端子(14)と前記基板端子(18)との間の電位差レベルが約0.5ボルト以下、特に、約0.3ボルト以下であり、ドレイン端子(16)とソース端子(14)とが異なる電位に置かれ、そしてドレイン−ソース電圧及び/又はゲート−ソース電圧を調節することによって、ソース(S)とドレイン(D)との間に荷電キャリアのフローを生じさせ、ソース(S)とドレイン(D)との間で半導体材料(20)を加熱して局所的に融解し、ソース(S)とドレイン(D)との間に少なくとも1個の固定伝導チャネルを形成することが提案される。  (もっと読む)

(もっと読む)

半導体装置

【課題】メモリ・ロジック混載型の半導体装置の高性能化を可能にする技術を提供する。

【解決手段】半導体基板1と、半導体基板1上の絶縁層19と、絶縁層19内の複数のコンタクトプラグ16,66と、絶縁層30と、絶縁層30内に設けられた、キャパシタ82、複数のコンタクトプラグ25,75、バリアメタル層27,87及び銅配線29,88とを備えている。半導体基板1の上面内のソース・ドレイン領域9は銅配線29に電気的に接続されている。また、半導体基板1の上面内のソース・ドレイン領域59の一方は銅配線88に電気的に接続されている。そして、ソース・ドレイン領域59の他方はキャパシタ82に電気的に接続されている。

(もっと読む)

MOSFETフューズ素子を有する集積回路

MOSフューズ(200)の少なくとも1つのMOSパラメータが、少なくとも1つのMOSパラメータ基準値を与えるために特徴付けられる。そして、MOSフューズ(200)は、フューズ端子(204,206)にプログラミング信号が印加されることによってプログラミング電流がフューズリンク(202)を流れることにより、プログラムされる。フューズ抵抗は、第1の論理値と関連する測定されたフューズ抵抗を与えるために測定される。プログラムされたMOSフューズのMOSパラメータは、測定されたMOSパラメータ値を与えるために測定される。測定されたMOSパラメータ値は、MOSフューズの第2の論理値を決定するために基準MOSパラメータ値と比較され、その比較に基づいてビット値が出力される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】embedded DRAMに対して、ロジック回路に用いるCMOSトランジスタのゲート電極上およびソース/ドレイン領域をコバルトシリサイド化することができる半導体装置の製造方法を提供する。

【解決手段】少なくともメモリセル領域を除く領域のソース/ドレイン領域7a、7b上に形成されたUSG9と、ゲート電極4上に形成されたUSG9及びシリコン酸化膜5を除去する。USG9は、耐コバルトシリサイド化反応膜として作用する。コバルトをスパッタ法によりウエハ全面に成膜してランプアニール等の熱処理を行うことにより、USGに覆われていない領域のロジック回路領域のトランジスタのソース/ドレイン領域7a、7bとゲート電極4上にコバルトシリサイド膜11を形成することにより、ロジック回路の高性能化及び高集積化が可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】不揮発性メモリを混載したロジック半導体装置に関し、周辺トランジスタのゲート絶縁膜の絶縁耐圧低下を防止しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板に活性領域を画定する素子分離領域を形成する工程と、第1の絶縁膜を形成する工程と、第1の絶縁膜とはエッチング特性の異なる第2の絶縁膜を形成する工程と、少なくとも活性領域と素子分離領域との境界を含む領域に形成された第2の絶縁膜を、フルオロカーボン系のエッチングガスを用いたドライエッチングにより除去する工程と、酸素を含む雰囲気に曝すことにより、ドライエッチングの際に第1の絶縁膜上に付着したフルオロカーボン膜を除去する工程と、第1の絶縁膜をウェットエッチングにより除去する工程とを有する。

(もっと読む)

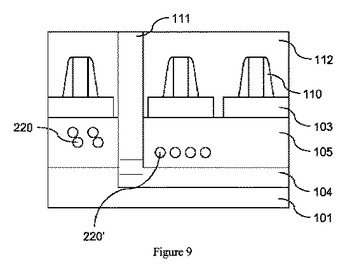

埋め込み型トラッピング層によるトランジスタの閾値電圧の調整方法

方法は、電子サブアセンブリの形成について、調整可能な閾値電圧を有する少なくとも1つの第1のトランジスタ(110)を担持する半導体層(103)が絶縁層(102、105)に接合される組み立てステップと、半導体層および第1のトラッピングゾーンが容量結合されるように、第1のトラッピングゾーン(220)が所定の第1の深さで絶縁層に形成される形成ステップであって、前記第1のトラッピングゾーンが、前記第1のトランジスタのチャネルの少なくとも下に延び、かつ前記第1のトラッピングゾーンの外側のトラップの密度より高い密度のトラップを有する形成ステップとを含み、前記第1のトランジスタからの有用な情報はこのトランジスタ内の電荷移動である。具体的な実施形態において、第2のトランジスタのチャネルの少なくとも下に延びる第2のトラッピングゾーンが、第1のトラッピングゾーンに使用されるのとは異なるエネルギーおよび/または用量および/または原子の第2の注入によって形成される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】スタック構造のゲート電極をドライエッチングによりパターニングする際に、エッチングの終点を確実に検出し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板16上のメモリセルアレイ領域12に形成された複数のフラッシュメモリセル34であって、半導体基板16上にトンネル絶縁膜20を介して形成されたフローティングゲート22Rと、フローティングゲート22R上にONO膜24を介して形成されたコントロールゲート26Rとをそれぞれ有する複数のフラッシュメモリセル34と、半導体基板16上のパッド領域14に形成された複数のダミーセル38であって、半導体基板16上にトンネル絶縁膜20を介して形成され、フローティングゲート22Dと、フローティングゲート22D上にONO膜24を介して形成されたコントロールゲート26Dとをそれぞれ有する複数のダミーセル38とを有している。

(もっと読む)

半導体装置

【課題】集積回路を構成するMISFETの処理速度の向上とリーク電流の低減を両立させ、かつ、半導体装置の小型化を達成することができる技術を提供する。

【解決手段】単体のMISFETから構成される回路素子に代えて、しきい値電圧の異なる複数のMISFETからなる同一ノードトランジスタから回路素子を構成する。例えば、図2に示すように、nチャネル型MISFET1aとnチャネル型MISFET1bを並列接続しかつ、それぞれのゲート電極Gを電気的に接続する。このとき、例えば、nチャネル型MISFET1aを高VthMISFETから構成し、nチャネル型MISFET1bを低VthMISFETから構成する。

(もっと読む)

電気光学装置、電子機器、電気光学装置の製造方法

【課題】不揮発性メモリと画素TFTが同一基板上に併設されており、かつ高信頼性とされた液晶装置を提供する。

【解決手段】本発明の電気光学装置は、画素部と、これを駆動させる駆動回路と、不揮発性メモリと、を備えた電気光学装置である。画素部及び前記駆動回路の少なくとも一方におけるスイッチング素子は、不揮発性メモリとともに基板10A上に形成されている。スイッチング素子のゲート絶縁膜は、第1絶縁膜35と第2絶縁膜36と第3絶縁膜38との積層構造からなっており、不揮発性メモリは、第2絶縁膜36を介して半導体層33上に設けられたフローティングゲート電極37と、第3絶縁膜38を介してフローティングゲート電極37上に設けられたコントロールゲート電極39Aと、を有するメモリセル110aを備えている。

(もっと読む)

半導体装置

【課題】配線層にスイッチ素子を有するプログラム可能な半導体装置の提供。

【解決手段】第1の配線層101の配線と第2の配線層102の配線を接続するビア103の内部、ビアの第1の配線との接触部、第2の配線との接触部のうちの少なくとも1つに、電解質材料104等導電率が可変の部材が配設され、ビア103は、第1の配線との接触部を第1の端子、第2の配線との接触部を第2の端子とする導電率が可変型のスイッチ素子又は可変抵抗素子として用いられ、スイッチ素子の導電率を変えることで、第1の

端子と第2の端子との接触部との接続状態を、短絡、開放、又はその中間状態に可変に設定自在とされる。金属イオンの酸化還元反応によって、第1の電極と第2の電極間の導電率が変化する2端子スイッチ素子を備え、第1の電極に接続された逆極性の第1、第2のトランジスタと、第2の電極に接続された逆極性の第3、第4のトランジスタを備えている。

(もっと読む)

コンパイラブルメモリマクロ、半導体記憶回路、及びそれらを用いた半導体集積回路、並びに半導体記憶回路の構成方法

【課題】回路規模を増大させることなく付加的な機能を追加するコンパイラブルメモリマクロを提供すること。

【解決手段】コンパイラブルメモリマクロ1は、最低限必要な複数の基本的機能を提供する一般ブロックA〜Eと、一般ブロックA〜Eの少なくとも一つに対して、基本的機能とは異なる機能を提供する特殊ブロックであるVSSレベル昇圧回路14とを備える。一般ブロックA〜Eは、予め決められた配置規則に従って配置されている。VSSレベル昇圧回路14は、配置規則に従って一般ブロックA〜Eが配置された際に生じるデッドスペースDSに、配置されている。

(もっと読む)

81 - 100 / 127

[ Back to top ]