Fターム[5F083ZA15]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリと独立機能ブロック (1,941) | メモリ+(ゲートアレイ、マスタスライス) (127)

Fターム[5F083ZA15]に分類される特許

41 - 60 / 127

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、水素または希ガスのいずれかの元素が添加されている。

(もっと読む)

半導体装置

【課題】半導体装置を高集積化する。

【解決手段】本実施形態の半導体装置は、絶縁体内に設けられ、半導体集積回路を含んでいる半導体基板70と、絶縁体の開口部POPを介してその上面が露出するパッド90と、パッド90下方において半導体基板70のキャパシタ領域91内に設けられる複数のキャパシタ1と、を具備し、キャパシタ1は、所定の被覆率を満たすように、パッド90下方のキャパシタ領域91内に設けられ、キャパシタ1の2つの電極にそれぞれ接続されるコンタクト18A,18Gは、開口部POPと上下に重ならない位置に設けられている。

(もっと読む)

半導体記憶装置

【課題】 省スペースによって従来よりも多くの論理回路及びヒューズブロックを設けることができる半導体記憶装置を提供する。

【解決手段】 ヒューズ露出窓を介して外部に露出して互いに並置された複数のヒューズ片を各々が含む複数のヒューズブロックがゲートアレイの近傍において縦列に配置され、電源配線と接地配線とが当該ヒューズ片の並置方向に沿って延在しており、ヒューズブロックの配置のために当該ゲートアレイの近傍のスペースを活用した半導体記憶装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極GE2の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極GE2側に位置する側壁部において、第1の斜面と、第1の斜面と交差する第2の斜面と、を有する。このように、溝g2の形状をΣ形状とすることで、pチャネル型電界効果トランジスタのチャネル領域に加わる圧縮歪みを大きくすることができる。

(もっと読む)

半導体記憶装置

【課題】本発明の実施形態は、書き込み、消去に対する耐性を向上させた半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、第1導電形の半導体基板の主面上において、前記主面に対して平行な第1の方向に沿って設けられた複数の多値記憶セルと、前記多値記憶セルの間の前記半導体基板の表面に選択的に設けられた第2導電形の第1半導体領域と、前記主面に対して前記第1半導体領域よりも深く設けられた第1導電形不純物を含む第2半導体領域と、を備えている。さらに、前記半導体基板の前記主面上に設けられ、前記主面に対して平行な第2の方向に沿って設けられた複数の2値記憶セルと、前記2値記憶セルの間の前記半導体基板の表面に選択的に設けられた第2導電形の第3半導体領域と、を備える。そして、前記第1半導体領域の第2導電形不純物を補償する第1導電形不純物の量は、前記第3半導体領域の第2導電形不純物を補償する第1導電形不純物の量よりも多いことを特徴とする。

(もっと読む)

半導体集積回路

【課題】トランジスタの性能の劣化の防止に有利な半導体集積回路を提供する。

【解決手段】実施形態によれば、半導体集積回路は、ワード線とビット線との交差位置にそれぞれ配置されデータを保持するデータ記憶部(SRAMセル)と前記データ記憶部に記憶された保持データを論理的に反転させる反転回路22と、前記データ記憶部が記憶するデータの論理反転の有無を識別するフラグをロウ単位で記憶するフラグビットカラム11−1とを備える、メモリセルアレイ11を具備する。

(もっと読む)

不揮発性プログラマブルロジックスイッチおよび半導体集積回路

【課題】回路サイズを減少させることを可能にする。

【解決手段】素子分離領域102によって分離された、隣接する第1導電型の第1半導体領域101aおよび第2導電型の第2半導体領域101cと、第1半導体領域101a上に設けられた不揮発性メモリセルトランジスタ10と、第2半導体領域101c上に設けられ、第1半導体領域101aに設けられた第1ドレイン領域10bと電気的に接続されたゲート電極20C2とを有するパストランジスタ20と、第1半導体領域101aに設けられ第1半導体領域に基板バイアスを印加する第1電極8と、第2半導体領域101cに設けられ第2半導体領域に基板バイアスを印加する第2電極9と、を備えている。

(もっと読む)

不揮発性メモリのゲートのパターニング方法

【課題】不揮発性メモリ(NVM)領域及び前記NVM領域と重ならないよう非NVM領域を有する半導体基板の上にNVMのゲートスタックを形成する。

【解決手段】

上記の製造方法は、半導体基板上のNVM領域及び非NVM領域に選択ゲート層を形成する工程と、NVM領域及び非NVM領域における選択ゲート層を同時にエッチングする工程と、NVM領域及び非NVM領域における半導体基板上に電荷蓄積層を形成する工程と、NVM領域及び非NVM領域における電荷蓄積層上に制御ゲート層を形成する工程と、NVM領域及び非NVM領域における電荷蓄積層を同時にエッチングする工程とを備える。NVM領域における選択ゲート層をエッチングする工程は、電荷蓄積層の部分が選択ゲート層の第1部分上にあり、かつ選択ゲート層の第1部分の側壁と重なるように行い、かつ、制御ゲート層の部分を電荷蓄積層の部分上にあるように行う。

(もっと読む)

抵抗変化素子及びその製造方法、並びに半導体装置及びその製造方法

【課題】低動作電圧を実現すると共に、スイッチング電圧のばらつきを低減した抵抗変化素子及びその製造方法、並びに半導体装置及びその製造方法を提供すること。

【解決手段】抵抗変化素子は、第1電極と、第1電極に接し、電圧の印加により抵抗が変化する抵抗変化層と、抵抗変化層に接する第2電極と、を備える。抵抗変化層は、高密度層と、高密度層より低密度の低密度層を有する。

(もっと読む)

限られたチャージ拡散を有するチャージトラップメモリ

【課題】隣接メモリセルへの漏洩電流を減らすフラッシュメモリ、特にチャージトラップメモリおよびそれを形成するプロセスフローの提供。

【解決手段】セルチャンネル620を含む半導体線が、STI領域120上に形成される。セルチャンネルは、トンネル酸化物層621、トラッピング誘電体層623、およびブロッキング誘電体層628を含む活性誘電体スタックで覆われる。結果として得られるセルチャンネルを分離するトレンチ625は、伝導層460で少なくとも部分的に充填され得る。活性誘電体層および/または伝導層の部分は、セルチャンネルの下、たとえば、セルチャンネルおよびSTI領域の間の界面695の下に位置し得る。そのような構成は、活性誘電体スタックおよび/または半導体層がセルチャンネルの下に位置しない構成に比べて、あるセルチャンネルから隣接セルチャンネルに拡散する荷電粒子670に対して経路長の増大をもたらす。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】筒状形状の容量を高容量にするとともに、下部電極に高抵抗領域が形成されるのを防ぐ半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体装置100は、筒状形状に形成された容量130を含む。半導体装置100は、基板102上に形成された絶縁膜104,106,108,110と、絶縁膜104,106,108,110に設けられた凹部内の底部には形成されず側壁に選択的に形成された第1の金属膜132、および凹部内の底部上および側壁の第1の金属膜132上に形成された第2の金属膜134を含み、筒状形状に形成された下部電極131と、下部電極131上に形成された容量膜136と、容量膜136上に形成された上部電極138とを含む。

(もっと読む)

半導体装置の製造方法

【課題】検査コストや解析コスト、製品コストを低減可能な半導体装置の製造方法を提供する。

【解決手段】例えば、ウエハ検査工程(S1003)で、半導体ウエハ上のロジック回路を対象とした電気的検査(ロジック部テスト)(S1003a)と、メモリ回路を対象とした電気的検査(メモリ部テスト)(S1003b)を行い、それぞれの検査結果から得られた故障箇所を複合マップ24上に重ねて表示する。この複合マップ24を用いると、例えば、ロジック故障22とメモリ故障23が併存して分布する領域を判別でき、この領域に対してメモリ故障23に対する詳細解析を優先的に行うことで、特にロジック故障22とメモリ故障23の故障原因が共通であった場合に効率的な詳細解析を行うことが可能となる。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去特性の変動が小さく、特性の安定した不揮発性半導体記憶装置を実現する。

【解決手段】不揮発性半導体記憶装置50は、第1導電型の半導体基板1上にゲート電極6bを有し第2導電型のMISFET5と、半導体基板1上の第2導電型第1ウェル3に設けられ、第1容量電極6cを有する第1MISキャパシタ15と、半導体基板1上の第2導電型第2ウェル4に設けられ、第2容量電極6aを有する第2MISキャパシタ21とを備える。ゲート電極6b、第1容量電極6c、第2容量電極6aが電気的に接続されてフローティングゲート6を構成する。第2MISキャパシタ21にて、第2ウェル4と、第2ウェル4上の部分の第2容量電極6aとがキャパシタ領域を構成する。第2容量電極6aは、キャパシタ領域が複数の分割キャパシタ領域に分割され、各分割キャパシタ領域の面積が変動してもその総面積は略一定となる平面形状及び配置を有する。

(もっと読む)

集積回路およびその形成方法

【課題】製造コストを良好に減少できる集積回路およびその形成方法を提供する。

【解決手段】集積回路は、第1のメモリアレイ、および第1のメモリアレイに接続された論理回路を含み、第1のメモリアレイの全てのメモリセルの全ての活性トランジスタおよび論理回路の全ての活性トランジスタは、フィン電界効果トランジスタ(FinFET)であり、第1の縦方向に沿って配置されたゲート電極を有する。FinFETs300a〜300cは、基板301上に配置され得る。基板301は、複数の活性領域305a〜305cを含み得る。活性領域305a〜305cは、基板301の表面301a上の非平面活性領域であり得る。

(もっと読む)

半導体装置およびその製造方法

【課題】複数の強誘電体キャパシタによる凹凸形状の影響を受けてキャパシタを被覆する水素バリア膜の水素拡散阻止能力が劣化すること、および強誘電体キャパシタの分極特性がばらつくことを防止する半導体記憶装置とその製造方法を提供する。

【解決手段】半導体基板1上に形成された強誘電体キャパシタ19を被覆する層間絶縁膜20として、ペロブスカイト型金属酸化物絶縁体、ビスマス層状ペロブスカイト型酸化物強誘電体などのような金属酸化物を含む絶縁体からなる膜を用いる。このような膜はスピンコート法で形成できるので容易にその表面が平坦な膜が得られ、従ってその上に形成される水素バリア膜22の膜厚も一様となって水素拡散阻止能力が維持できる。また膜20は酸素が透過しやすい性質を有するので、酸素熱処理により強誘電体キャパシタ19における分極特性のばらつきも十分防止できる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】共通ゲートを有する複数のトランジスタセルをアレー状に配置する構成を持つ不揮発性半導体集積回路装置において、STI領域のパターニング工程でのパターンの変形を防ぐ製造方法を提供する。

【解決手段】半導体メモリ等のメモリセルアレー等の露光において、矩形形状のSTI溝領域エッチング用単位開口を行列状に配置したSTI溝領域エッチング用単位開口群をネガ型レジスト膜28上に露光するに際して、列方向に延びる第1の線状開口群を有する第1の光学マスクを用いた第1の露光ステップと、行方向に延びる第2の線状開口群を有する第2の光学マスクを用いた第2の露光ステップとを含む多重露光を適用する。直行する2方向において、それぞれの方向に対してマスクを用いて露光を行うことで、矩形形状48の端部における近接効果を回避することができ、矩形形状48の端部が丸みを帯びるのを回避することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタの下部電極材料の選択自由度が高く、ビア工程の少ない半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板101上に形成されたスイッチングトランジスタ301A,301Bと、拡散層121と、トランジスタ301上に形成された層間絶縁膜131と、下部電極211、強誘電体膜212、及び上部電極213を含む強誘電体キャパシタ201A,201Bと、上部電極213の上方に形成された配線層141と、上部電極213と配線層141とを電気的に導通させる第1のプラグTWと、拡散層121と配線層141とを電気的に導通させる第2のプラグV1A,V1Bと、下部電極211の側方に配置されており、下部電極211と拡散層121とを電気的に導通させる第3のプラグCSFとを備える。

(もっと読む)

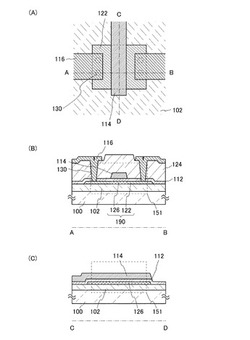

不揮発性半導体記憶装置及びその製造方法

【課題】高速なアクセスが可能で、かつ、高集積化が可能なスプリットゲート型不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体基板101の主表面の溝に第1、第2のスプリット型不揮発性メモリセルを形成した不揮発性半導体記憶装置100であって、溝内部の対向する第1、第2の側壁102a,102bの表面にそれぞれ第1、第2のスプリット型不揮発性メモリセルの選択ゲート121とコントロールゲート122とが形成され、第1、第2のスプリット型不揮発性メモリセルの選択ゲート121とコントロールゲート122とには、それぞれ異なる電圧を印加することが可能である。

(もっと読む)

集積回路構造、及び集積回路の製造方法

【課題】異なるフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、第1装置領域の第1部分と、第2装置領域の第2部分と、を有する半導体基板からなる。第1半導体フィンは半導体基板上にあり、第1フィン高さを有する。第2半導体フィンは半導体基板上にあり、第2フィン高さを有する。第1フィン高さは第2フィン高さより高い。

(もっと読む)

不揮発性半導体記憶装置

【課題】動作の信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置にメモリセルアレイ及び制御回路を設け、メモリセルアレイには、それぞれ複数の絶縁膜及び電極膜が交互に積層された積層体を設け、この積層体に積層方向に延びる貫通ホールを形成し、その内部にシリコンピラーを埋設し、電極膜とシリコンピラーとの間に電荷蓄積膜を設ける。これにより、電極膜とシリコンピラーとの交差部分毎にメモリセルが形成される。そして、制御回路は、フォーマット時に、全てのメモリセルに値「0」を書き込み、全てのメモリセルに対して値「0」を消去する動作を行い、積層体の最上段に形成されたメモリセルに記憶された値を読み出し、値「0」が読み出されたメモリセルについては、消去動作が不良であったと判定し、以後不使用とする。

(もっと読む)

41 - 60 / 127

[ Back to top ]