Fターム[5F089AB09]の内容

フォトカプラ、インタラプタ (4,081) | フォトカプラの種類 (286) | モノリシック型 (51) | 受光素子と信号処理回路が一体 (20)

Fターム[5F089AB09]に分類される特許

1 - 20 / 20

集積型半導体装置

【課題】 従来に比べて小型で、素子機能部間で、高い周波数の信号を高精度に伝送することができる集積型半導体装置を提供する。

【解決手段】 サファイア単結晶基板10と、サファイア単結晶基板10の一方主面10Aに第1素子機能部22を備え、他方主面10Bに第2素子機能部32を備え、第1素子機能部22が光を発光し、第2素子機能部32がサファイア単結晶基板10を透過した光を受光することで、高い周波数の信号を精度良く伝送する。

(もっと読む)

光結合装置

【課題】耐電源ノイズ特性を維持しながら光結合装置に使用される半導体チップを縮小化する。

【解決手段】一つの実施形態によれば、光結合装置は、第一のフォトダイオード、第一の反転増幅器、第二のフォトダイオード、第二の反転増幅器、及びコンパレータが設けられる。第一のフォトダイオードの第一の接合容量及び第一の反転増幅器の第一の帰還抵抗の積と、第二のフォトダイオードの第二の接合容量及び第二の反転増幅器の第二の帰還抵抗の積とが同一の値に設定され、第一の接合容量が第二の接合容量よりも大きく設定される。

(もっと読む)

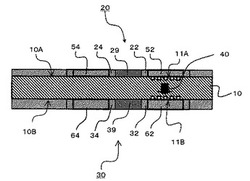

電気的相互連結及び光学的相互連結を具備した多層光電子基板並びにその製造方法

【課題】 本発明は、ドライバ回路及び増幅器回路を用いることなく、電気相互連結及び光相互連結を実現する光電子基板の提供を目的とする。

【解決手段】 本発明による基板は、ポリマー導波路が中に形成されている第1の層と、ポリマー導波路が中に形成されている第2の層と、第1の層内に形成され、第1の層内の第1の導波路と光学的に結合された第1の縦型光カップラーと、第2の層内に形成され、第2の層内の第2の導波路と光学的に結合された第2の縦型光カップラーとを含み、第1の導波路と第2の導波路の間で光が結合されるように、第1の縦型光カップラーは第2の縦型光カップラーの隣に配置されている。

(もっと読む)

半導体装置及びCPU

【課題】 安価なガラス基板を用い、情報量の増加に対応でき、なおかつ高性能

で高速動作が可能な集積回路を有する半導体装置の提供を課題とする。

【解決手段】 集積回路を構成する種々の回路を複数のガラス基板上に形成し、

各ガラス基板間の信号の伝送は、光信号を用いる所謂光インターコネクションで

行なう。具体的には、あるガラス基板に形成された上段の回路の出力側に発光素

子を設け、別のガラス基板に形成された後段の回路の入力側に、該発光素子と対

向するように受光素子を形成する。そして上段の回路から出力された電気信号か

ら変換された光信号が発光素子から出力され、該光信号を受光素子が電気信号に

変換し、後段の回路に入力される。

(もっと読む)

高速光配線素子

【課題】多重チャネルを含む高速光配線素子を提供する。

【解決手段】高速光配線素子が提供される。高速光配線素子は、SOI基板上の第1半導体チップと、SOI基板上の前記第1半導体チップから電気信号を受信して光信号を出力する光放出器と、SOI基板上の前記光信号を感知して電気信号に変換する光検出器と、SOI基板上の前記光検出器によって変換された電気信号を受信する第2半導体チップとを含む。

(もっと読む)

光電子集積回路装置

【課題】 信号の伝送歪み及び伝送ロスを減少することができる光電子集積回路装置を提供することを第一の目的とする。また、信号の伝送遅延時間を短縮することができる光電子集積回路装置を提供することを第二の目的とする。

【解決手段】 電気回路部11と、光学的出力端子部12と、光学的入力端子部10とを含む第一光電子集積回路(1−1)及び第二光電子集積回路(1−2)で構成されており、該第一光電子集積回路(1−1)及び第二光電子集積回路(1−2)が夫々の光学的出力端子部12と光学的入力端子部10とが向き合うように配置されることにより、複数の光電子集積回路装置1間の信号伝送を光信号で行うことが可能となり、信号の伝送歪み及び伝送ロスを減少できると共に、信号の伝送遅延時間を短縮することができる。

(もっと読む)

光電子デバイス

【課題】光電子デバイスを提供する。

【解決手段】光電子デバイスは半導体材料からなる基板(6,7)と基板上または内に配置されたスマートピクセルのアレイとを含む。各スマートピクセルは有機発光材料の少なくとも一層(12)を含み、さらに基板から隔てた側の上で有機層と接触する光透過電極(13)を含んでいる。スマートピクセルは画像の感知、処理、通信およびディスプレイを含む機能の範囲の一つ以上を可能とする。

(もっと読む)

集積回路パッケージ

【課題】有形の光伝送路をなくすことで、低損失接続を実現するとともに、コストアップを大幅に抑えかつ低電力で複数の半導体集積回路を最小の実装面積で接続可能にする。

【解決手段】半導体集積回路とともに光集積回路を実装する実装体及び/又は蓋体よりなる集積回路パッケージであって、シリコンチップ101を内蔵したパッケージの一部若しくは外周の一部に発光部103と受光部102を有し、パッケージの基本形状は外周に凸部の出っ張り部分と凹部の切り欠き部分とを有し、凸部と凹部に発光部103と受光部102が実装される。凸部と凹部は物理的に接合することができ、このとき2つの集積回路パッケージの発光部103と受光部102が相対するように接合される。

(もっと読む)

半導体リレー

【課題】寄生インダクタンスを最小化し、20Gbps程度まで使用可能な半導体リレーを実現する。

【解決手段】接地金属板上に配置された半導体基板と、この半導体基板上に積層された絶縁層及び単結晶層と、この単結晶層上に形成された配線に接続された発光ダイオードと、前記単結晶層に形成された光起電力素子、サイリスタ、ダイオード及び2個一組の出力用FETと、前記接地金属板と隔離して形成された4個の信号パッドからなり、前記発光ダイオードのアノードとカソードのそれぞれが前記信号パッドの2個にボンディングワイヤを介して接続され、前記出力用FETのそれぞれのドレイン電極と信号パッドの他の2個が前記ボンディングワイヤを介して接続され、前記接地金属及び信号パッドの底面を除く前記半導体基板上の電子部品を樹脂封止型パッケージで封止した。

(もっと読む)

有機発光素子および無機光検出器を備える集積光結合器

【課題】モノリシックに集積された光結合器を提供する。

【解決手段】光結合器は、有機発光素子100と検出器領域を備える無機光検出器104とを有し、この検出器領域は有機発光素子に光学的に結合される。有機発光素子は、電気入力信号を光信号に変換し、かつ無機光検出器は、光信号を電気出力信号に変換し、有機発光素子および無機光検出器は、CMOS構造のILD層150、IMD層160によって集積され、かつガルバニック分離がなされている。

(もっと読む)

半導体装置及びこの半導体装置を用いた半導体リレー

【課題】 耐圧の確保及び信頼性の高い半導体リレー用の半導体装置を提供する。

【解決手段】 絶縁膜13分離の活性層14、15を有するSOI基板11と、活性層15表面に形成され、絶縁膜18分離された複数の受光素子のアノードとカソードとが、配線層31により接続された受光素子アレイ6と、活性層14表面に形成され、絶縁膜18分離され、ソース領域24、ドレイン領域20、及び両領域20、24間にゲート電極26を有し、絶縁膜18を跨ぐ配線層32を介して、受光素子アレイ6のアノード及びカソードが、それぞれ、ゲート電極26及びソース領域24に、ソース領域24が互いに、ドレイン領域20が外部接続端子8に接続されたMOS素子5と、MOS素子5のソース領域24とドレイン領域20との間の絶縁膜29の中に抵抗体27とを備えている。

(もっと読む)

光モジュール

【課題】表示用LEDによる情報表示の視認性を高めると共に、放射電磁雑音の外部への漏れを抑制することができる光モジュールを提供する。

【解決手段】光トランシーバ1は、TOSA7及びROSA9と、送信回路及び受信回路と、LDドライバ及びポストアンプを収容し、金属材料からなる筐体3と、透明又は半透明の材料からなり、筐体3に固定されたレセプタクル部11と、発光によって情報を表示する表示用LED29と、を備え、TOSA7及びROSA9は、レセプタクル部11に係合することで光信号の光軸方向に直交する面内において位置決めされると共に、レセプタクル部11と筐体3とにより光軸方向に挟み込まれることで光軸方向において位置決めされ、表示用LED29の光は、レセプタクル部11に導かれる

(もっと読む)

光通信モジュールおよびその製造方法

【課題】データ通信の確実化を図りつつ、製造効率を向上させることが可能な光通信モジュールおよびその製造方法を提供すること。

【解決手段】基板1と、発光素子3と、受光素子4と、集積回路素子5と、を備える赤外線データ通信モジュールA1であって、基板1には、開口11aを有する貫通孔11が形成されており、配線パターン2は、開口11を囲うリング状部21を含んでおり、発光素子3がボンディングされた底部71と、末広がり状とされたコーン状部72と、を有するボンディングカップ7をさらに備えており、ボンディングカップ7のうち少なくとも底部71を含む部分が貫通孔11に進入しており、かつ、コーン状部72のうち開口11aから突出する部分とリング状部21とがハンダ82により接合されている。

(もっと読む)

光半導体装置およびその製造方法

【課題】高受光感度のモニター用フォトダイオードと、高速・高性能のトランジスタを同一の半導体基板上に混載することができるようにする。

【解決手段】低濃度のp型のシリコン基板1と、シリコン基板1上に選択的に形成された高濃度のn型カソード層19のPN接合により構成されたモニター用フォトダイオードと、マイクロミラー部3に、シリコン基板1をエッチングすることにより形成された第一の斜面10と第二の斜面11およびミラー底面12で構成された第一の斜面10からの入射光に対する受光素子であり、第一の斜面10と第二の斜面11はシリコン基板1の主面に対して所定の角度を持ち、ミラー底面12はシリコン基板1の主面に対して平行であることと、シリコン基板1とn型カソード層19のPN接合で形成される空乏層20aと、第一の斜面10で形成される空乏層20bが接続したことを特徴とする。

(もっと読む)

携帯電子機器

【課題】表示部と操作部との間で、信号線数を増加させることなくかつ可動による機械的磨耗を起こさずに信号伝送可能な携帯電子機器を提供する。

【解決手段】発光素子を含む操作部と、受光素子を含み、前記操作部から送られた情報に基づく表示を実行する表示部と、を備え、前記操作部と前記表示部との重ね合わせ状態を変化させることにより開状態と閉状態とがそれぞれ可能とされ、前記開状態において前記発光素子と前記受光素子とを結ぶ光路と、前記閉状態において前記発光素子と前記受光素子とを結ぶ光路と、が異なることを特徴とする携帯電子機器を提供する。

(もっと読む)

制御装置の入力回路

【課題】フォトカプラのオン電流のバラツキが大きくても制御装置に対してオン信号を安定的に与えることができるようにする。

【解決手段】トランジスタTr1が、フォトカプラ4への入力電流Iaがフォトカプラ4のオン電流の上限値を上回る所定の第4電流を超えることが想定されることを条件としてフォトカプラ4の入力に対して通電するようにスイッチングする。

(もっと読む)

半導体装置

【課題】 小さな電流能力しか持たない信号源によるスイッチ制御と保護機能を備えたパワーMOSFETを備えた半導体装置を提供する。

【解決手段】 第1端子にドレインを接続し、第2端子に上記パワーMOSFETのソースを接続し、上記第3端子と上記パワーMOSFETのゲートの間に高抵抗手段を接続する。上記パワーMOSFETに流れる電流を検出する電流検出手段の出力信号を受けて上記パワーMOSFETに流れる電流を制限する電流制限回路を上記パワーMOSFETのゲートと上記第2端子との間に設ける。

(もっと読む)

光伝送路一体型オス型コネクタとメス型コネクタおよびそれらを嵌合した光電気混載コネクタとそれを搭載した電子機器

【課題】本発明は、実装面積が小さく、着脱が容易で小型化、薄型化ができる光電気混載コネクタを提供することを目的とする。

【解決手段】光路変換部材で直交方向に光路が曲げられて内蔵された接続配線パターン114を備えた光伝送部材110を有する光伝送路一体型オス型コネクタ100と光素子と制御回路とを凹部に備えたメス型コネクタ300を互いに嵌め合わせることにより、積層して光電気混載コネクタ400を構成する。これにより、実装面積が小さく、着脱が容易で小型化、薄型化ができる光電気混載コネクタ400を実現できる。

(もっと読む)

半導体装置とそれを用いた装置及び半導体リレー

【課題】半導体装置とそれを用いた装置及び半導体リレーにおいて、半導体リレーのBBM動作と高速スイッチング動作を実現する信号出力を可能とする。

【解決手段】半導体リレー1は、発光ダイオード2と、半導体装置3と、a接点用のスイッチング素子5aと、b接点用のスイッチング素子5bとを備えている。半導体装置3は、フォトダイオードアレイ10,11、駆動用素子Qa2、及び抵抗Raを直列接続し、抵抗Raにバイパス用素子Qa1を並列接続し、駆動用素子Qa2の両端に出力端子を設けて構成した第1の出力回路と、フォトダイオードアレイ10,12、駆動用素子Qb2、及び抵抗Rbを直列接続し、抵抗Rbにバイパス用素子Qb1を並列接続し、駆動用素子Qb2の両端に出力端子を設けて構成した第2の出力回路とを備えている。出力調整されたフォトダイオードアレイ11,12により、BBM動作可能な信号が出力端子に出力される。

(もっと読む)

半導体装置およびそれを用いた電子機器

【課題】クロックスキューを容易に低減し、また消費電力の増大を招くことなくクロック信号の周波数を上げて半導体装置の動作速度の高速化を図る。

【解決手段】SOIウェーハ101上に複数の機能ブロックが形成されている。複数の機能ブロックは夫々フォトダイオード(PD)102を有している。複数の機能ブロックの全てが導光板107で覆われる。光信号発生部108からはクロック信号に対応した光信号が発生され、この光信号が導光板107に入射される。この光信号は導光板107を介して、複数の機能ブロックのPD102に入射される。複数の機能ブロックでは、夫々、PD102により光信号が電気信号に変換され、クロック信号を取得できる。PD102に対応して波長分波フィルタ105を配設することで、各機能ブロックのPD102には、所定の波長の光信号のみを選択的に入射できる。

(もっと読む)

1 - 20 / 20

[ Back to top ]