Fターム[5F092AA11]の内容

Fターム[5F092AA11]に分類される特許

141 - 160 / 299

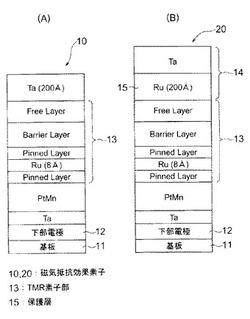

磁気抵抗効果素子の製造方法

【課題】真空中で行われるドライエッチングの微細加工の製造工程に特別な変更を加えることなく微細加工時に使用されるマスク材を二重に重ねて積層することで、製造工程中必然的に含まれる酸化過程により保護層の最表層に酸化層が形成されたとしても、MR比の低下を防止し、磁気抵抗効果素子としての性能を高く保持することができる磁気抵抗効果素子の製造方法を提供する。

【解決手段】少なくとも2層の磁性層を含む磁性多層膜からなる磁気抵抗効果素子のドライエッチング方法であって、Taからなる第1のマスクの下層にRu、Rh、Os、Nb、Ir、及びReのいずれか1つである第2のマスクを二重に積層する方法である。

(もっと読む)

磁気ヘッドの製造方法

【課題】磁気ヘッドのリードヘッド等の製造工程において、研磨加工時に基板の表面に研磨くず等が残留することを抑え、的確にシールド層等を形成可能とする。

【解決手段】基板11上に形成した磁気抵抗効果膜層13aをエッチングしてリード素子13を形成するとともに、ハードバイアス膜を形成するための凹部を形成する工程と、ハードバイアス膜となる磁性層15aを成膜する工程と、前記磁性層が被着した前記リード素子の表面と前記凹部とにわたり、外縁が前記凹部の内縁よりも内側位置となるようにレジスト20を形成する工程と、該レジスト20をマスクとして前記磁性層15aを除去する工程と、前記リード素子13の上面位置まで基板の表面を平坦状に研磨加工する工程とを備える。

(もっと読む)

磁気ヘッドの製造方法

【課題】研磨加工時に基板の表面に研磨くず等の残渣が残留することを抑え、シールド層を的確に形成する。

【解決手段】磁気抵抗効果膜層13aをエッチングし、リード素子13を形成するとともにハードバイアス膜15を形成するための凹部を形成する工程と、基板の表面に磁性層15aを成膜する工程と、該磁性層のリード素子13の表面と前記凹部に被着した領域をレジスト20により被覆する工程と、該レジスト20をマスクとして不要な磁性層15aを除去した後、研磨加工を施してリード素子13およびハードバイアス膜15を形成する工程とを備え、前記磁性層15aをレジスト20により被覆する工程においては、該レジスト20をマスクとして前記磁性層15aを除去することにより、前記凹部の内縁に沿って溝22を形成し、前記研磨加工の際に研磨くず等の残渣Eを該溝22内に堆積させて研磨加工する。

(もっと読む)

ソリッドステート材料

ホスト材料と量子スピン欠陥とを含むソリッドステートシステムであって、量子スピン欠陥が室温で約300μs以上のT2を有し、ホスト材料が、約20ppb以下の全窒素濃度を有する単結晶CVDダイヤモンドの層を含み、量子スピン欠陥が形成されている所に最も近い表面上の点に中心がある約5μmの半径の円によって定義される領域内の単結晶ダイヤモンドの表面粗さRqが約10nm以下であるソリッドステートシステム、ソリッドステートシステムの調製方法及び約20ppb以下の全窒素濃度を有する単結晶ダイヤモンドのスピントロニクス用途での使用を開示する。 (もっと読む)

半導体記憶装置の製造方法

【課題】エッチングにより離脱する窒化膜またはCap層の材質を、確実に検出可能な半導体記憶装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体記憶装置は、(a)下地層1,2,3,4上にTMR膜5、キャップ層6を順に積層する工程と、(b)TMR膜5、キャップ層6をパターニングして、それらの正規積層構造パターン13およびダミー積層構造パターン16を形成する工程とを備える。そして、(c)正規およびダミー積層構造パターン13,16を覆う窒化膜7を形成する工程と、窒化膜7上に酸化膜8を形成する工程と、(e)酸化膜8および窒化膜7をエッチングして、キャップ層6の上部を露出させる工程とを備える。工程(e)は、エッチングを行いながら、当該エッチングにより離脱した窒化膜7またはキャップ層6の材質を検出する。

(もっと読む)

磁気トンネル接合装置、これを備えるメモリセル、およびその製造方法

【課題】隣接した磁気トンネル接合装置間の干渉現象および電気的な短絡を防止することのできる磁気トンネル接合装置およびその製造方法を提供することである。

【解決手段】所定の間隔を有する複数の開口部を備える絶縁膜を形成するステップと、前記開口部の底面および側壁に第1電極を形成するステップと、前記第1電極上に磁気トンネル接合層を形成するステップと、前記磁気トンネル接合層上に残りの前記開口部を埋め込む第2電極を形成するステップと、を含む。

(もっと読む)

磁気ランダムアクセスメモリを製造するためのシステム及び方法

磁気ランダムアクセスメモリを製造するためのシステム及び方法が、開示される。特に、堆積の間に磁性膜のアライニング方法が、開示される。上記方法は、基板上への第1の磁性材料の堆積の間に存在する基板の領域の第1の方向に沿って第1の磁場を印加することを含む。上記方法は、基板上への前記第1の磁性材料の堆積の間に、領域に第2の方向に沿って第2の磁場を印加することをさらに含む。  (もっと読む)

(もっと読む)

磁気センサの製造方法

【課題】 特に磁化方向が異なる固定磁性層を備える素子部を同一基板上に簡単且つ適切に形成できる磁気センサの製造方法を提供することを目的としている。

【解決手段】 基板1に、巨大磁気抵抗効果を発揮する多層構造を異なる複数方向に素子部7,8が延在するように形成する工程、前記の延在方向に向けて電流を流し、電流磁界により、異なる方向に延在する各素子部7,8の固定磁性層の磁化方向を異なる方向に固定する工程、異なる方向に延在する各素子部7,8間を切断する工程、を備える。

(もっと読む)

半導体装置

【課題】多層配線に挟まれたある層の層間絶縁膜が厚薄各部分を有し、容易に製造することができる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、第1領域と第2領域を有する半導体基板と、第1領域の半導体基板上方に配置されたMTJと、MTJを覆うように配置され、第2領域上方よりも第1領域上方の膜厚が薄い絶縁膜と、絶縁膜中に配置され、MTJと電気的に接続された導電膜と、第1領域上方の絶縁膜上方に形成され、導電膜と電気的に接続されたビット線と、第2領域上方の絶縁膜上方に形成された配線と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】動作特性の良いMTJ素子を有する半導体装置及びその製造方法を得る。

【解決手段】MTJ素子MD1は、下部磁性膜6、トンネル絶縁膜7及び上部磁性膜8の順に積層される積層構造により形成される。下部磁性膜6及び上部磁性膜8は構成材料として非晶質あるいは微結晶状態のコバルト鉄ボロン(CoFeB)を含んでいる。トンネル絶縁膜7は構成材料として酸化アルミニウム(AlOx)を含んでいる。MTJ素子MD1の上部磁性膜8上にCAP層CP1が形成され、CAP層CP1上にハードマスクHM1が形成される。CAP層CP1は結晶質のルテニウム(Ru)単体構造を構成材料としており、ハードマスクHM1は結晶質のタンタル(Ta)単体構造を構成材料としている。ハードマスクHM1の膜厚はCAP層CP1の膜厚より厚く形成される。

(もっと読む)

低抵抗グラニュラ膜及びその製造方法

【課題】高い磁気抵抗効果(MR効果)を維持しつつ、より低抵抗であるグラニュラ膜を提供すること。

【解決手段】MgOターゲット3及び強磁性体ターゲット4を備え、基板8に対してMgO及び強磁性体をスパッタリングするスパッタリング装置において、プラズマ干渉状態を最適化した状態で、前記基板8上に(111)配向を有するMgOバリア層と、前記MgOバリア層中に分散された強磁性体微粒子と、を含む低抵抗グラニュラ膜を形成する。

(もっと読む)

磁気抵抗素子の製造方法

【課題】 TMR値が高く、RAが低いMTJデバイスを得ること。

【解決手段】 磁気抵抗素子の製造方法は、金属層を第1の厚さに形成する金属層形成ステップと、金属層を不活性ガスのプラズマに晒し、前記第1の厚さよりも小さい第2の厚さにエッチングするプラズマトリートメントを実行するプラズマ処理ステップと、前記プラズマトリートメントを施した金属層を酸化し、トンネルバリアを構成する金属酸化物を形成する酸化ステップと、を有するトンネルバリア形成ステップを有する。

(もっと読む)

半導体装置の製造方法

【課題】MTJ素子の特性を劣化させることなく、良好な絶縁性を有するシリコン窒化膜をMTJ素子の保護膜として形成することができる半導体装置の製造方法を得る。

【解決手段】MTJ素子部(MTJ素子MD1及び上部電極ET1)を含む全面にシリコン窒化膜33を形成する。シリコン窒化膜33の成膜装置として、平行平板型プラズマCVD装置を用いる。そして、成膜ガスとして、NH3を含むことなく、SiH4/N2/ヘリウムガス(He)を用いる。成膜温度は200〜350℃に設定される。さらに、理想的には、Heの流量がSiH4の流量に対し、100〜125倍を呈するようにHeとSiH4の流量比が設定される。

(もっと読む)

複数のピニング方向を有する2軸磁場センサおよび該センサの製造方法

製造工程および装置は、種々の配向で設定された長軸を有する高アスペクト比形状(62、63)にエッチングされる単一の参照層(60)から形成される2つの異なるピニング軸(206、216)のみを必要とする2つの差動センサ構成(201、211)の高性能磁場センサ(200)を提供し、したがって、参照層を適切に整列した飽和磁場(90)で処理してから飽和磁場を除去すると、高アスペクト比パターンは各パターン化形状(62、63)の磁化を参照層のそれぞれの所望の軸に沿って緩和させる形状異方性を示す。加熱および冷却を行うと、強磁性薄膜は種々の所望方向にピン止めされる。  (もっと読む)

(もっと読む)

単一のマスクを使用して磁気トンネル接合を形成する方法

磁気トンネル接合(MTJ)デバイスを集積回路に集積化するための方法は、半導体BEOL(back-end-of-line)プロセスフローにおいて、第1の中間誘電体層および少なくとも第1の金属配線を有する基板を提供することを含む。第1の中間誘電体層および第1の金属配線上に、磁気トンネル接合材料層が堆積される。材料層から、第1の金属配線に結合される磁気トンネル接合スタックは単一のマスクプロセスを使用して定義される。磁気トンネル接合スタックは集積回路に集積化される。 (もっと読む)

TMR素子製造方法

【課題】 本発明は、TMR素子の製造方法に関し、より詳細にはTMR素子の形成過程において2回のイオンミリングを行いTMR素子のバリア層に付着した導電物質を除去して品質の高いTMR素子を製造する方法に関するものである。

【解決手段】 本発明のTMR素子製造方法は、生成したTMR膜上にレジストパターンを形成するレジストパターン形成工程と、レジストパターンをマスクとしてTMR膜をイオンミリングする第1イオンミリング工程と、レジストパターンのスリミングを行うスリミング工程と、スリミングされたレジストパターンをマスクとしてTMR膜を再びイオンミリングする第2イオンミリング工程と、を備えるよう構成する。

(もっと読む)

STTMRAM磁気トンネル接合アーキテクチャおよび集積化

半導体BEOL(back-end-of-line)プロセスフローにおける磁気ランダムアクセスメモリ(MRAM)のための磁気トンネル結合(MTJ)デバイスは、少なくとも1つの制御デバイスと接続するための第1の金属配線、および、第1のマスクを用いて誘電体保護バリア内に形成されるビアを通して第1の金属配線に結合するための第1の電極を含む。デバイスは、また、第1の電極に結合される、データを記憶するためのMTJスタックを含み、MTJスタックの一部は、第2のマスクに基づく横寸法を有する。第2のマスクによって定義される部分はコンタクトビアの上に存在する。第2の電極はMTJスタックに結合され、また、第2のマスクによって定義されるものと同一の横寸法を有する。第1の電極およびMTJスタックの一部は、第3のマスクによって定義される。第2の金属配線は、第2の電極および少なくとも1つの別の制御デバイスに結合される。 (もっと読む)

2つのマスクを用いる磁気トンネル接合素子の製造方法

2つのマスクを用いて磁気ランダムアクセスメモリのための磁気トンネル接合を形成するための方法は、露出された第1の相互接続メタライゼーション37を含むインターレベル誘電性層36の上に第1の電極30、固定磁化層32、トンネルバリア層12、自由層11及び第2の電極6を堆積することを含む。トンネルバリア層、自由層及び第2の電極を含むMTJ構成は、第1のマスクによって第1の相互接続メタライゼーションの上に定められる。第1の不動態化層40は、MTJ構成を包み、露出した第2の電極をそのままにする。第3の電極15は、第2の電極を備える接触物に堆積される。第2のマスクは、第3の電極、第1の不動態化層、固定磁化層及び第1の電極を含む、より大きい構成をパターニングするために用いられる。第2の誘電性不動態化層8は、エッチングされた複数の層、第1のインターレベル誘電性層及び第1の相互接続メタライゼーションを覆う。  (もっと読む)

(もっと読む)

窒化アルミニウム薄膜およびその製造方法

【課題】平坦で薄いAlN薄膜およびその製造方法を提供する。

【解決手段】AlN薄膜2は、III族元素、IV族元素およびV族元素から選ばれた1種以上の添加元素を0.001wt%以上10wt%以下含む。該AlN薄膜2は、III族元素、IV族元素およびV族元素から選ばれた1種以上の添加元素を0.001wt以上10wt%以下含むAlN焼結体を真空チャンバ内にセットし、基材1を真空チャンバ内にセットした状態で、AlN焼結体にレーザを照射することで発生したプラズマを用いて基材1上に形成可能である。

(もっと読む)

磁気検出素子および磁気センサ用コアならびにこれらの製造方法

【課題】高価な設備、装置を必要とせず、製造効率に優れた高品質の磁気検出素子および磁気センサ用コアならびにこれらの製造方法を提供すること。

【解決手段】磁気検出素子1は、非磁性材料からなる素子基板10上にアモルファス金属からなる薄板状の磁性材料箔20が貼着され、該磁性材料箔20がフォトリソグラフィにより所定のパターンに形成されてなる。磁気センサ用コア2は、非磁性材料で形成された対からなる素子基板60a,60b間にアモルファス金属からなる薄板状の磁性材料箔70が貼着され、前記対からなる素子基板60a,60b間に前記磁性材料箔70が貼着された部分には、検出コイル81の巻回部およびバイアス磁界発生用コイル82の巻回部が形成されている。

(もっと読む)

141 - 160 / 299

[ Back to top ]