Fターム[5F092AD08]の内容

ホール/MR素子 (37,442) | 素子の動作 (2,918) | 印加電流又は電圧 (1,470) | 検出電流方向 (1,342) | 基板主面膜面に平行(CIP含む) (269) | 基板に水平に磁場をかけるもの (25)

Fターム[5F092AD08]に分類される特許

1 - 20 / 25

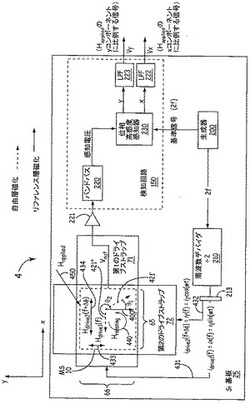

単一の磁気抵抗センサを使用して磁場の平面方向の磁場コンポーネントを決定するのための装置および方法

【課題】平面に適用された磁場を測定する方法を提供する。

【解決手段】第1の交流ドライブ電流を第1のストラップに適用し、第1のストラップの少なくとも一部が、磁気抵抗センサの上に横たわり、第1のストラップが、第1の方向Xに延びる大きさを有することを特徴とし、第2の交流ドライブ電流を第2のストラップに同時に適用し、第2のストラップの少なくとも一部が第1のストラップの少なくとも一部の上に横たわり、第2のストラップが第2の方向Yに延びる大きさを有し、第2の方向が、第1の方向と並行ではなく、第2の交流ドライブ電流が、第1の交流ドライブ電流と位相が異なり、磁気抵抗センサが、磁気抵抗センサの平面で回転する周期的回転磁気ドライブ磁場に影響を受けることを特徴とする。

(もっと読む)

薄膜磁気センサ及びその製造方法

【課題】水分透過量が小さいSi系絶縁膜が回路表面に形成されており、Si系絶縁膜の密着性及び耐クラック性に優れた薄膜磁気センサ及びその製造方法を提供すること。

【解決手段】以下の工程を備えた薄膜磁気センサの製造方法及びこの方法により得られる薄膜磁気センサ。(1)基板表面に薄膜ヨーク、GMR膜、電極及び配線を備えた素子部を形成する素子部形成工程。(2)少なくとも電極の表面の全部又は一部を含む領域(薄膜ヨーク、GMR膜及び配線の表面を除く)にフォトレジスト膜を形成するフォトレジスト膜形成工程。(3)基板の表面にAl2O3膜を形成するAl2O3膜形成工程。(4)Al2O3膜の表面に、Cat−CVD法を用いてSi系絶縁膜を形成するSi系絶縁膜形成工程。(5)フォトレジスト膜、並びに、フォトレジスト膜の上に形成された余分なAl2O3膜及びSi系絶縁膜を除去する除去工程。

(もっと読む)

磁気センサ

【課題】 動作点の変動と抵抗値比のばらつきを抑制することができると共に、温度特性を改善した磁気センサを提供する。

【解決手段】 磁気センサ1は、センサ回路部2を備える。このセンサ回路部2は、第1および第3の磁気抵抗素子R1,R3を直列接続した第1の直列回路6と、第2および第4の磁気抵抗素子R2,R4を直列接続した第2の直列回路7とを備え、第1の直列回路6と第2の直列回路7とを並列接続したブリッジ回路5によって構成される。第1ないし第4の磁気抵抗素子R1〜R4の表面は絶縁膜12によって覆われる。また、第3の磁気抵抗素子R3および第4の磁気抵抗素子R4の表面には、絶縁膜12を挟んで磁性材料からなる磁束集磁膜13が形成される。

(もっと読む)

磁気検出装置とその製造方法

【課題】本発明は、小型化に優れると共に高精度な電気抵抗の調整が可能である磁気検出装置とその製造方法を提供することを目的とする。

【解決手段】第一の短絡層41と第二の短絡層42とを、それぞれ第一の磁気抵抗効果素子層11と第一の抵抗素子層21とにのみ導通させ且つ一体に積層させて短絡することで、第一の磁気抵抗効果素子層11と第一の抵抗素子層21との電気抵抗を調整する。

(もっと読む)

磁気センサ

【課題】 特に、軟磁性体と磁気抵抗効果素子間でオフセットが生じても、外乱感度を小さくすることができる磁気センサを提供することを目的とする。

【解決手段】 軟磁性体3のY1側部側に位置し、感度軸方向P1がY2、Y1からの水平磁界成分を受ける第1磁気抵抗効果素子S1と、軟磁性体のY2側部側に位置し、感度軸方向P2はY1、Y2からの水平磁界成分を受ける第2の磁気抵抗効果素子S2と、軟磁性体のY2側部側に位置し、感度軸方向がY2、Y2からの水平磁界成分を受ける第3磁気抵抗効果素子S3、軟磁性体のY1側部側に位置し、感度軸方向がY1、Y1からの水平磁界成分を受ける第4磁気抵抗効果素子S4と備える。S1とS2とが直列接続されたA素子群と、S3とS4とが直列接続されたB素子群が構成される。A素子群とB素子群とが直列接続されるとともに、A素子群とB素子群の間に出力端子が設けられる。

(もっと読む)

磁気抵抗効果素子及びこれを用いた磁気センサ

【課題】MR素子の消費電力を低減する。

【解決手段】MR素子10は、基板11と、基板11上に設けられたMR膜12とを備えている。MR膜12は、ジグザグ状に折れ曲がる直線12aが更に多重にジグザグ状に折れ曲がる形状12bを有する。直線12aは、複数の形状部121,122,123を形成している。それぞれの形状部121,122,123は、互いに平行な複数の長方形12cがジグザグ状に直列に接続された形状を有し、かつジグザグ状に互いに直列に接続されている。

(もっと読む)

磁気センサ

【課題】 強磁場耐性を向上させた磁気センサを提供することを目的とする。

【解決手段】 素子連設体17,18,52,53を備える。各素子連設体では、素子部へ供給されるバイアス磁界B1,B2の方向が、隣り合う素子部で逆向きとなるように各バイアス層が配置されるとともに、平面視にて前記軟磁性体と重なり面積の大きい前記バイアス層を両側に配置した前記素子部と、前記重なり面積がゼロの前記バイアス層を両側に配置した前記素子部とが並んでいる。P1,P2は感度軸方向である。第1の素子連設体17と第2の素子連設体18とが直列に接続された磁気抵抗効果素子と、第3の素子連設体52と第4の素子連設体53とが直列に接続された第2の磁気抵抗効果素子とを備える。

(もっと読む)

3次元センサに関するシステムと方法

【課題】マルチ軸センサを製造する方法を提供する。

【解決手段】第1のアプリケーション・エレクトロニクスを備えた第1の活性化表面114を有する第1のダイ102を製作するステップと、第2のアプリケーション・エレクトロニクスを有する第2の活性化表面115、および、第2のアプリケーション・エレクトロニクスから第2の活性化表面と隣接している第2のダイ104の側面インタフェースまで伸びる少なくとも一つの電気的接続を有する第2のダイを製造するステップと、第1の活性化表面と同一平面上の側面インタフェースを整列配置するステップと、複数の電気的接続119と第1の活性化表面との間に少なくとも一つの電気的接続を形成するステップとを有する。

(もっと読む)

垂直ホールセンサおよび垂直ホールセンサを製造するための方法

【課題】 本発明は、半導体チップ(1)内に集積化される垂直ホールセンサおよびそれの製造のための方法に関する。

【解決手段】 垂直ホールセンサは、第2の導電型の導電性領域(3)内に埋め込まれる、第1の導電型の導電性ウェル(2)を有する。電気的接点(4)が、導電性ウェル(2)の平坦面(5)上で直線(6)に沿って配置される。導電性ウェル(2)は、それが導電性ウェル(2)の平坦面(5)から深さT1に位置する最大値を有するか、または深さT2まで本質的に一定であるかのどちらかのドーピング分布を有するように、高エネルギーイオン注入法およびその後の加熱によって生成される。

(もっと読む)

磁性体部材

【課題】外部磁界に対する電子スピンの変化量を大きくして、外部磁界の検出感度を高めることができる磁性体部材を提供する。

【解決手段】所定の形状に形成された磁性体5の表面に、その磁性体5に固有の最小磁区よりも小さい多数の領域7に分割する多数の溝6が形成されており、前記磁性体5は、ワイヤ状に形成され、前記領域7は、ハニカム状に形成され、前記溝6には、反磁性体材料が埋められている。磁性体部材5の表面は磁壁が存在しない単磁区構造になり、外部磁界にする検出感度を高めることができる。

(もっと読む)

磁気センサ及びその製造方法

【課題】 特に、同一チップ上に感度軸方向が異なり、ブリッジ回路を構成する複数の磁気抵抗効果素子を形成でき、測定精度に優れた磁気センサを提供することを目的とする。

【解決手段】 同一チップ29上に磁気抵抗効果素子13a〜13dが複数個、備えられてブリッジ回路を構成している。各磁気抵抗効果素子の固定磁性層21はセルフピン止め型であり、直列回路を構成する磁気抵抗効果素子13a,13d(13b,13c)同士は、感度軸方向P1〜P4が反平行となっている。各磁気抵抗効果素子のフリー磁性層23の上面には、フリー磁性層23との間で磁場中でのアニール処理を行うことなく交換結合バイアスを生じさせ各フリー磁性層23の磁化方向を磁化変動可能な状態で感度軸方向に対して直交方向に揃えることができる反強磁性層24が設けられている。

(もっと読む)

スピン注入電極構造、スピン伝導素子及びスピン伝導デバイス

【課題】室温でのシリコンチャンネル層におけるスピンの注入を可能とするスピン注入電極構造、スピン伝導素子又はスピン伝導デバイスの提供。

【解決手段】スピン注入電極構造IEは、シリコンチャンネル層12と、シリコンチャンネル層12の第一部分上に設けられた第一酸化マグネシウム膜13Aと、第一酸化マグネシウム膜13A上に設けられた第一強磁性層14Aと、を備える。第一酸化マグネシウム膜13Aには、シリコンチャンネル層12及び第一強磁性層14Aの両方と格子整合している第一格子整合部分Pが部分的に存在している。

(もっと読む)

スピン偏極装置

【課題】スピン偏極装置と他の素子の電気的な接続が、より容易に行えるようにする。

【解決手段】第1オーミック電極107の側の電界印加電極106の側面106aと同一平面上で第2半導体層104に形成された第1側面104aと、第2オーミック電極108の側の電界印加電極106の側面106bと同一平面上で第2半導体層104に形成された第2側面104bと、第1オーミック電極107の側の電界印加電極106の側面106aと同一平面上で第3半導体層105に形成された第3側面105aと、第2オーミック電極108の側の電界印加電極106の側面106bと同一平面上で第3半導体層105に形成された第4側面105bとを備える。

(もっと読む)

集積磁力計およびその製造プロセス

略平坦な基板の上面と称される一表面上に蒸着される複数の多層磁気抵抗センサを備える集積磁力計であって、基板の前記上面は複数の傾斜面を備えた少なくとも1つの空洞または隆起を有することと、4つの前記傾斜面上には異なる、かつ対で互いに反対の方向性を有する少なくとも4つの前記磁気抵抗センサが配置され、各センサはそのセンサが配置される面に対して平行な外部磁場の一成分に感応することを特徴とする集積磁力計。このような磁力計の製造プロセス。 (もっと読む)

磁気抵抗デバイス

【課題】大きな出力信号強度を得られるEMRデバイスに、既存のスライダ形成技術を利用して磁気ヘッドスライダが形成できるような、デバイス構造とデバイス製造方法を提供すること

【解決手段】磁気抵抗デバイスは、基板(4;64)と、第一方向(14)に伸びた細長半導体チャネル(11)素子と、チャネルへの接点の組(27)を提供する少なくとも2つの導電性リード(26)とを含んでいる。デバイスは、チャネルと接続したオプションの半導体シャント(8)を含んでいる。オプションのシャント、チャネル及び接点の組は、第一方向及び基板の表面に対して垂直な第二方向(15)に向かって、基板に対して積重ねられる。デバイスは、チャネルに沿って伸びる側面(30)を有している。デバイスは、側面に対して一般的に垂直な方向の磁場(31)に対して反応する。

(もっと読む)

スピントロニクス装置及び論理演算素子

【課題】 電流−スピン流変換効率が高く、高強度のスピン流が得られるスピントロニクス装置を提供する。

【解決手段】 対向する第1端面及び第2端面を有し、正孔と電子とが同程度のキャリア密度と移動度を有し、ホール係数がゼロである非磁性の両極性伝導金属からなるスピン流生成領域30と、第1端面に設けられ、スピン偏極された正孔をスピン流生成領域30に注入する強磁性体からなる第1主電極20と、第2端面に設けられ、電子をスピン流生成領域30に注入する第2主電極40とを備える。ローレンツ力により、正孔と電子とを同一方向に輸送されるようにして、正孔と電子の電荷を互いに相殺してスピン流を得る。

(もっと読む)

半導体装置

【課題】 従来、外付け抵抗の電圧降下から検出していたパワーN型MOSFETに流れる電流を、高感度のホール素子に発生するホール電圧VHにより検出する。

【解決手段】 アースラインに向かって配線されたソース配線層8の一部をN型層1に形成したトレンチ20内に配設する。これによりトレンチ20内に配設されたソース配線層8a近傍のN型層1に発生する磁束密度Bを高める。この高い磁束密度Bが発生しているトレンチ20内のソース配線層8a近傍のN型層1を横切るホール電流IH成分を増やし、ホール素子Hに発生するホール電圧VHを高くする。このように、高い磁束密度Bの発生領域にホール素子Hを配置することにより、パワーN型MOSFETのソース電流Iが数A程度でも大きなホール電圧VHを発生する。

(もっと読む)

半導体装置

【課題】従来、外付け抵抗の電圧降下から検出していたパワーN型MOSFETに流れる電流を、ホール素子に発生するホール電圧VHにより検出する。

【解決手段】アースラインに向かって配線されたソース配線層8の直下の絶縁膜7aを数10nm程度の厚さとする。これにより、ソース電流Iにより、ソース配線層8の直下領域または該ソース配線層8の両側面部のN型層1に発生する磁束密度Bを高くする。この高い磁束密度Bの発生領域にホール素子Hを配置することにより、パワーN型MOSFETのソース電流Iが数A程度でも大きなホール電圧VHを発生する。

(もっと読む)

回転状態検出装置

【課題】重金属汚染の影響による、検出精度の低下が抑止された回転状態検出装置を提供する。

【解決手段】半導体基板の厚さ方向に電流を流す少なくとも2つの電流端子と、厚さ方向に流れる電流と鎖交する磁束によって生じたホール電圧を検出する2つの電圧端子と、を有する縦型ホール素子と、該縦型ホール素子の出力信号に基づいて、回転体の回転状態を検出する検出部と、を備え、縦型ホール素子は、半導体基板に少なくとも3つ形成され、その内の2つの縦型ホール素子は、それぞれの縦型ホール素子における電圧端子間を結ぶ線分のなす角度θが0°より大きく180°より小さくなるように形成されており、検出部は、角度θを形成する2つの縦型ホール素子の出力信号を用いてアークタンジェント演算を行う演算部と、残りの縦型ホール素子の出力信号をパルス信号に変換する変換部と、を有する

(もっと読む)

垂直ホールセンサ

【課題】オフセットが可能な限り小さい垂直ホールセンサを提供する。

【解決手段】半導体チップ内に集積化される垂直ホールセンサが、半導体チップの表面上の直線に沿って配置される少なくとも6個の電気接点9を有する。電気接点9は、所定のルールに従って、接点9が2個の最外側の接点のうち1個9.1から始まる参照番号1、2、3および4によって連続的にかつ繰り返し番号をつけられるときに、同じ参照番号が割り当てられる接点9が、互いに電気的に接続されるように、配線される。

(もっと読む)

1 - 20 / 25

[ Back to top ]