Fターム[5F092BA12]の内容

Fターム[5F092BA12]の下位に属するFターム

SOI (9)

Fターム[5F092BA12]に分類される特許

1 - 20 / 46

半導体装置、および、その製造方法

【課題】電流により発生する磁場を化合物半導体回路で集約して検出することができる小型で、高感度かつ高精度な電流センサを実現すること。

【解決手段】半導体回路(LSI回路)と化合物半導体回路(ホール素子を有する化合物半導体素子)とが形成された基板に、さらに、化合物半導体素子の直上に、該直下の化合物半導回路に対して磁束密度を増加させるための所定の形状からなる電気配線(コ字型または馬蹄型の形状を呈した金属配線)を形成し、この電気配線に被検出電流を流すようにした。

(もっと読む)

磁気センサ

【課題】ホール素子を有する磁気センサにおいて、簡易な回路構成である信号処理回路で、ホール素子の出力電圧に含まれるオフセット電圧及びフリッカノイズを除去することのできる磁気センサを提供する。

【解決手段】ホールプレートHは、ホールプレートHを流れる電流のキャリアの種類を、ゲート電極Gの電位Vgにより、電子または正孔のいずれか一方にすることが可能な両極性材料から形成される。さらに、入出力端子TA,TA’,TB,TB’が、ホールプレートHの面内で対向する電流入力端子対と電圧出力端子対とになり、その際に電流入出力端子対と電圧出力端子対とが互いに直交するような位置に形成される。

(もっと読む)

ホール素子及びその製造方法、半導体装置

【課題】コストの増大を抑えつつ、ホール素子のオフセット電圧Voを低減することができるようにしたホール素子及びその製造方法と、半導体装置を提供する。

【解決手段】半導体基板1に設けられた第1のN型拡散領域10と、半導体基板1に設けられ、第1のN型拡散領域10に電気的に接合された複数の第2のN型拡散領域20と、半導体基板1に設けられ、複数の第2のN型拡散領域20の各々の間を電気的に分離するSTI領域30と、を有する。第1のN型拡散領域10は感磁部であり、複数の第2のN型拡散領域20の各々は感磁部に対する入出力端子部である。複数の第2のN型拡散領域20の各々におけるN型の不純物濃度は、STI領域30の底部30bを基点に深さ方向で0μm以上、0.2μm以下の範囲内で、5×1017個/cm3以上、3×1019個/cm3以下である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】モールド成型によりパッケージ化されてなる半導体装置において、パッケージからのストレスに起因する半導体デバイスの特性変化のさらなる抑制を図る。

【解決手段】Si−LSI202a、202b全体をSiO2膜205とSiN膜206とで覆い、2つのSi−LSI202a、202b間のSi基板201表面に、化合物半導体デバイスからなるホール素子208の感磁部を形成する。ホール素子208とSi−LSI202a、202bとを金属配線210で接続した後、SiN膜211、SiO2膜212を形成して平坦化し、その上にAl配線213を形成する。基板上面からみて、Al配線213の、ホール素子208と重なる領域にエッチング溶液注入穴214を形成しここからエッチング溶液を注入してAl配線213の下部のSiO2膜212を除去し中空部215を形成する。

(もっと読む)

半導体基板、半導体装置および半導体基板の製造方法

【課題】十分な感度を有したp型キャリアのホール素子の製造に適した半導体基板を提供する。

【解決手段】表面の全部または一部がシリコン結晶面であるベース基板と、前記ベース基板の上に位置し、前記シリコン結晶面に達する開口を有し、結晶の成長を阻害する阻害体と、前記開口の底部の前記シリコン結晶面の上に位置する第1結晶層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第1金属層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第2金属層と、を有し、前記一対の第1金属層のそれぞれを結ぶ第1最短線と、前記一対の第2金属層のそれぞれを結ぶ第2最短線とが、交わる関係、または、ねじれの位置関係にある半導体基板を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】低保磁力をもつ軟磁性薄膜を備え、この軟磁性薄膜で磁気収束する半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板1に設けられたホール素子2と、ホール素子1上に設けられた軟磁性薄膜6が、少なくともホウ素を含有している。また、半導体基板1上で、かつホール素子2上に設けられた有機絶縁膜4と、有機絶縁膜4と軟磁性薄膜6との間に設けられた金属導電層5とを備え、軟磁性薄膜6が、金属導電層5上で少なくとも1個以上のホール素子2の感磁部を覆うように配置されている。形成された軟磁性薄膜6の総重量を100重量%としたときの鉄含有量が15〜30重量%、ホウ素含有量が0.15〜0.35量%、電解めっき液を安定化するpH緩衝剤に起因する炭素を0.4〜0.8重量%、残部がニッケルである。

(もっと読む)

集積化センサの配列

【課題】減少された大きさ、改善された精度、および/または改善されたダイナミックレンジを有する外部磁界センサ等を提供することを目的とする。

【解決手段】 集積回路(10)は、磁界感知素子(30)を支持する第1の基板(14)および他の磁界感知素子(20)を支持する第2の基板(26)を備えることができる。第1および第2の基板は、様々な構成で配列されてもよい。他の集積回路は、その表面に配置された第1の磁界感知素子および第2の異なる磁界感知素子を備えることができる。

(もっと読む)

ホールセンサ

【課題】チップサイズの増加がなく、高感度でオフセット電圧の除去が可能なホール素子を提供する。

【解決手段】正方形のホール素子感受部の4つの頂点にホール電圧出力端子と制御電流入力端子をそれぞれ独立に配置する。ホール電圧出力端子はすべて同一形状であり、制御電流入力端子はホール電圧出力端子のそれぞれの両側に、前記ホール電圧出力端子とは導通しないように間隔を置いて配置され、前記4つの頂点において同一形状を有する。

(もっと読む)

ホールセンサ

【課題】チップサイズの増加がなく、高感度でオフセット電圧の除去が可能なホール素子を提供する。

【解決手段】ホール素子は十字形状のホール素子感受部を有し、4つの凸部先端中央部にホール電圧出力端子を配置し、各凸部側面にはホール電圧出力端子とは独立に制御電流入力端子を配置する。このときホール電圧出力端子幅を小さくし、制御電流入力端子幅を大きくする。

(もっと読む)

磁気センサー素子および回転検出装置

【課題】高い空間分解能で検出できる磁気センサー素子を提供する。

【解決手段】本発明に係る磁気センサー素子1000では、電界効果トランジスター100は、ゲート電極14と、ゲート電極14の一方側に、ゲート幅方向に並んで形成された、第1不純物領域22および第2不純物領域24と、ゲート電極14の他方側に、ゲート幅方向に並んで形成された、第3不純物領域32および第4不純物領域34と、を有し、制御部200は、第1制御および第2制御を行い、第1制御では、第1不純物領域22および第2不純物領域24を第1端子(VDD端子)に接続し、第3不純物領域32を第2端子(VSS端子)に接続し、第2制御では、第3不純物領域32および第4不純物領域34を第1端子(VDD端子)に接続し、第2不純物領域24を第2端子(VSS端子)に接続し、第1端子(VDD端子)の電位は、第2端子(VSS端子)の電位より大きい。

(もっと読む)

複合半導体素子、その製造方法、磁気センサ及び画像形成装置

【課題】化合物半導体ウェハー素材を用いてホール素子などを作成するに当たり、無駄となる部分が多くコストの増加を招いていた。

【解決手段】 複合半導体素子が、基板(11)と、基板上(11)に備えられ有機材料を主材料とする平坦化層(14)と、例えばホール素子を構成する化合物半導体素子を含み平坦化層(14)上にボンディングされた半導体薄膜(12)を有する。化合物半導体薄膜(12)との電気的接続のための金属配線膜(23)をさらに備え、化合物半導体薄膜(12)と金属配線膜(23)との間に、より高い不純物濃度の化合物半導体層(17)を介在させても良い。

(もっと読む)

磁気センサー素子および回転検出装置

【課題】磁束密度のZ軸方向成分の位置分布を高い空間分解能で検出できる磁気センサー素子を提供する。

【解決手段】本発明に係る磁気センサー素子1000は、電界効果トランジスター100と、電界効果トランジスター100を制御する制御部200と、を含み、電界効果トランジスター100は、ゲート電極14と、ゲート電極14の一方側に、ゲート幅方向に並んで形成された、第1ソース領域32および第2ソース領域34と、ゲート電極14の他方側に、ゲート幅方向に並んで形成された、第1ドレイン領域22、第2ドレイン領域24、および第3ドレイン領域26と、を有し、制御部200は、第1制御および第2制御を行い、第1制御では、第1ソース領域32と、第1ドレイン領域22および第2ドレイン領域24と、の間に電圧を印加し、第2制御では、第2ソース領域34と、第2ドレイン領域24および第3ドレイン領域26と、の間に電圧を印加する。

(もっと読む)

磁気センサ

【課題】ホールセンサ出力の、磁束密度に対する直線性を向上させる。

【解決手段】絶縁性基板または半絶縁性基板10上に形成された膜厚方向に電子移動度の分布を有する化合物半導体薄膜を用いた磁気センサにおいて、導電層20となる化合物半導体薄膜を、第一の半導体層21と第二の半導体層22と第三の半導体層23とをこの順に積層して構成し、前記第一の半導体層21が前記絶縁性基板または半絶縁性基板10に接するように配置し、前記第二の半導体層のキャリア移動度を、前記第一の半導体層及び前記第三の半導体層のキャリア移動度よりも高く、且つ前記第二の半導体層22の不純物濃度を、前記第一の半導体層21及び前記第三の半導体層23の不純物濃度よりも大きくする。

(もっと読む)

回転センサ

【課題】 回転角度の検出精度を高めながら小型化することができる回転センサを実現する。

【解決手段】 磁気抵抗素子R1〜R8が各磁気抵抗素子の出力信号間に位相差が出るように配置された磁気抵抗素子領域E1と、ホール素子H1,H2が各ホール素子の出力信号間に位相差が出るように配置されたホール素子領域E2とを有し、かつ、磁気抵抗素子領域およびホール素子領域の少なくとも一部同士が重ねられたセンサチップ5と、各ホール素子の各出力レベルと閾値レベルとの比較結果を出す比較部53と、各磁気抵抗素子の各出力信号を用いて相対回転角度θに対応する演算角度φを演算する角度演算部60と、その演算された角度と閾値角度とを比較し、その比較結果と比較部53の比較結果とを用い、相対回転角度に対応する信号を出力する出力部70とを備える。

(もっと読む)

回転センサ

【課題】 磁気発生部の相対回転角度の演算時間を短縮することができる回転センサを実現する。

【解決手段】角度演算部60はAMRセンサM1,M2から出力される信号を用い永久磁石2に対する相対回転角度θと演算により求めた演算角度φとの偏差が所定値に収束するようにフィードバック制御を行って相対回転角度θを演算する。初期値決定部53はホール素子H1,H2から出力された各検出信号の各信号レベルと閾値との各比較結果を用い相対回転角度θの初期値θ0が含まれる角度範囲を判定し、その判定した角度範囲の中で発生し得る相対回転角度の初期値と前記演算角度の初期値との差の絶対値が90°未満となるように演算角度の初期値を決定する。初期値決定部は永久磁石2が相対回転を開始する前にのみ演算角度φの初期値φ0を決定し角度演算部60はその決定された演算角度φの初期値φ0を用いてフィードバック制御を開始し、相対回転角度θを演算する。

(もっと読む)

ゲルマニウム・ホール・プレートを有する集積ホール効果素子

集積回路及びその集積回路を製造する方法は、ゲルマニウム・ホール・プレートを有するホール効果素子を提供する。このゲルマニウム・ホール・プレートは、シリコンと比較して増大した電子移動度を提供し、それ故、より高感度なホール効果素子を提供する。 (もっと読む)

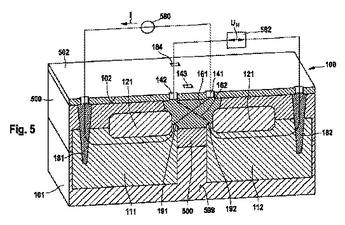

情報伝送のための集積回路

本発明は、情報伝送のための集積回路に関するものであり、基板(1)と、該基板(1)に集積された、または該基板(1)上に配置された少なくとも1つのホール素子(2)と、該ホール素子(2)に実質的に同心に、かつ該ホール素子(2)に対して垂直方向に間隔を置いて配置され、該ホール素子(2)から導電分離された第1のコイル(4)と、該ホール素子(2)に実質的に同心に、かつ該ホール素子(2)および前記第1のコイル(4)に対して垂直方向に間隔を置いて配置され、該ホール素子(2)から導電分離された第2のコイル(6)とを有し、第1のコイル(4)と第2のコイル(6)は、当該コイル(4、6)内に同じ方向で電流が流れるように電気的に直列に接続されている。  (もっと読む)

(もっと読む)

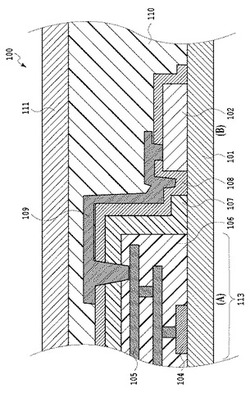

ホールセンサ素子および磁界を測定する方法

本発明は、ホールセンサ素子に関する。当該基板は、主要表面を備えた基板と、前記主要表面から前記基板内まで延在している、導電性のアクティブ領域と、前記アクティブ領域と、第1の下方のコンタクト面で接触している、基板内の導電性の第1埋設層とを有している。別の観点では、本発明は、上記のホールセンサ素子を用いた磁界の測定方法を実現する。ここでは、電気的な測定電流は主要表面での第1の上方コンタクト電極と第1の下方コンタクト面との間で、アクティブ領域を通って導かれる。第1の下方コンタクト面と第1の上方コンタクト電極との間の接続線に対して傾斜して延在する区間に沿って、アクティブ領域でホール電圧が検出される。択一的に、測定電流が上記の区間に亘って、アクティブ領域を通って導かれ、ホール電圧が第1の上方コンタクト電極と第1の下方コンタクト面との間で検出される。  (もっと読む)

(もっと読む)

半導体装置

【課題】 従来、外付け抵抗の電圧降下から検出していたパワーN型MOSFETに流れる電流を、高感度のホール素子に発生するホール電圧VHにより検出する。

【解決手段】 アースラインに向かって配線されたソース配線層8の一部をN型層1に形成したトレンチ20内に配設する。これによりトレンチ20内に配設されたソース配線層8a近傍のN型層1に発生する磁束密度Bを高める。この高い磁束密度Bが発生しているトレンチ20内のソース配線層8a近傍のN型層1を横切るホール電流IH成分を増やし、ホール素子Hに発生するホール電圧VHを高くする。このように、高い磁束密度Bの発生領域にホール素子Hを配置することにより、パワーN型MOSFETのソース電流Iが数A程度でも大きなホール電圧VHを発生する。

(もっと読む)

半導体装置

【課題】従来、外付け抵抗の電圧降下から検出していたパワーN型MOSFETに流れる電流を、ホール素子に発生するホール電圧VHにより検出する。

【解決手段】アースラインに向かって配線されたソース配線層8の直下の絶縁膜7aを数10nm程度の厚さとする。これにより、ソース電流Iにより、ソース配線層8の直下領域または該ソース配線層8の両側面部のN型層1に発生する磁束密度Bを高くする。この高い磁束密度Bの発生領域にホール素子Hを配置することにより、パワーN型MOSFETのソース電流Iが数A程度でも大きなホール電圧VHを発生する。

(もっと読む)

1 - 20 / 46

[ Back to top ]