Fターム[5F092BA32]の内容

Fターム[5F092BA32]の下位に属するFターム

積層構造 (19)

Fターム[5F092BA32]に分類される特許

1 - 20 / 30

磁気デバイスの製造方法

【課題】ダイシングストリートにGaAsが露出している場合、結果ダイシング時に素子のチッピング、電極や磁性体の剥離、溶解したGaAsによる電極接合部の汚染が発生し、さらにGaAs基板裏面もエッチングされるためGaAsの溶解による電極接合部の汚染の課題がある。

【解決手段】本発明は、ホール素子が設けられたGaAs基板と、GaAs基板上に設けられた磁気増幅機能を有する磁性体とを備える磁気デバイスにおいて、上記ホール素子上に絶縁層と、上記絶縁層上にTi系金属層と、上記Ti系金属層の上にCu系金属層とを有し、ダイシングストリート上を少なくとも無機絶縁材料乃至有機絶縁材料もしくはその両方でカバーさせGaAsを露出させず、またさらにGaAs基板裏面にも有機絶縁膜でカバーすることにより本課題を解決した。

(もっと読む)

電圧駆動型電磁石

【課題】室温付近で電圧によりキュリー温度を変化させることができ、かつ大きな磁化、即ち大きな磁界を発生させることが可能な電圧駆動型電磁石を提供する。

【解決手段】鉄、コバルト、ニッケルのうちのいずれか、もしくはこれらのうち少なくとも一つを含む合金からなる強磁性金属薄膜層12と、前記強磁性金属薄膜層12の片側に積層された絶縁層20と、前記絶縁層20の、前記強磁性金属薄膜層12とは反対側に設けられたゲート電極30と、前記強磁性金属薄膜層12と前記ゲート電極30の間に電圧を印加する電圧印加部40とを備える電圧駆動型電磁石を提供する。また、強磁性金属薄膜層12内の磁化を特定の方向に配向させる下地層13と、配向させた強磁性金属薄膜層12内の磁化の方向を維持させるキャップ層11を備える。

(もっと読む)

磁気センサ

【課題】ホール素子を有する磁気センサにおいて、簡易な回路構成である信号処理回路で、ホール素子の出力電圧に含まれるオフセット電圧及びフリッカノイズを除去することのできる磁気センサを提供する。

【解決手段】ホールプレートHは、ホールプレートHを流れる電流のキャリアの種類を、ゲート電極Gの電位Vgにより、電子または正孔のいずれか一方にすることが可能な両極性材料から形成される。さらに、入出力端子TA,TA’,TB,TB’が、ホールプレートHの面内で対向する電流入力端子対と電圧出力端子対とになり、その際に電流入出力端子対と電圧出力端子対とが互いに直交するような位置に形成される。

(もっと読む)

複合半導体素子、その製造方法、磁気センサ及び画像形成装置

【課題】化合物半導体ウェハー素材を用いてホール素子などを作成するに当たり、無駄となる部分が多くコストの増加を招いていた。

【解決手段】 複合半導体素子が、基板(11)と、基板上(11)に備えられ有機材料を主材料とする平坦化層(14)と、例えばホール素子を構成する化合物半導体素子を含み平坦化層(14)上にボンディングされた半導体薄膜(12)を有する。化合物半導体薄膜(12)との電気的接続のための金属配線膜(23)をさらに備え、化合物半導体薄膜(12)と金属配線膜(23)との間に、より高い不純物濃度の化合物半導体層(17)を介在させても良い。

(もっと読む)

ホール素子

【課題】従来の位置検出装置では、第1のホール素子および第2のホール素子をそれぞれ別のチップ内に形成していた。従って、2チップを使用しているため、コストが高く、パッケージを小さくできないという問題があった。また、ダイボンドの位置ずれにより、前記第1のホール素子と前記第2のホール素子との間のギャップ精度が悪いという問題もあった。

【解決手段】本発明に係るホール素子では、前記第1のホール素子および前記第2のホール素子が1チップ内に形成される。また、適正なレイアウトによりチップサイズを縮小することができる。これにより、パッケージサイズを小さくすることができる。さらに、本発明に係るホール素子では、前記第1のホール素子および前記第2のホール素子がリソグラフィーにより同一チップに同時に形成されるので、前記第1のホール素子と前記第2のホール素子との間のギャップ精度を向上させることができる。

(もっと読む)

ゲルマニウム・ホール・プレートを有する集積ホール効果素子

集積回路及びその集積回路を製造する方法は、ゲルマニウム・ホール・プレートを有するホール効果素子を提供する。このゲルマニウム・ホール・プレートは、シリコンと比較して増大した電子移動度を提供し、それ故、より高感度なホール効果素子を提供する。 (もっと読む)

磁界センサ

【課題】 調整可能なグラフェンを用いた磁界センサを提供する。

【解決手段】 グラフェンセンス層を採用する磁界センサであって、センス層内を移動する電荷キャリアに作用するローレンツ力が、グラフェン層内を移動する電荷キャリアの経路に変化をもたらす。磁界の存在を示すこの経路の変化を検出することができる。センサは、非磁性の電気的絶縁材料によってグラフェン層から分離される1つまたは複数のゲート電極を含む。ゲート電極へのゲート電圧の印加により、グラフェン層の電気抵抗が変化し、このゲート電圧の印加を用いて、センサの感度および速度を制御することができる。

(もっと読む)

電流センサの製造方法

【課題】ホール素子チップの厚さを均一化し、感度特性が均一で歩留まりや耐熱性に優れた電流センサの製造方法とする。

【解決手段】InSb単結晶基板13を、エポキシ接着剤12が塗布された支持基板11に接着する。単結晶基板13を面出し表面研磨し、その鏡面研磨面に感磁性部14を形成する。仮接着剤16を均一に塗布した支持基板15の一面と、感磁性部14が形成された単結晶基板13の一面とを仮接着し、支持基板11を除去する。単結晶基板13を感磁性部14が露出するまで研磨し、個々の感磁性部14を支持基板15ごと切断して多数のホール素子チップ17を分割形成する。エポキシ接着剤19を介しホール素子チップ17をフェライトコア18に接着して支持基板15を除去し、感磁性部14に電極21及び保護膜22を形成する。フェライトコア18及び感磁性部14を含む磁気回路を他のコアを組み付けて構成し、電流センサを製造する。

(もっと読む)

磁電変換素子の製造方法

【課題】磁電変換素子を極めて容易に短時間で作業性の優れた連続方法で製造することを可能とする。

【解決手段】基板が磁性体の磁電変換素子用ペレットを、リードフレームに接続する工程を備える磁電変換素子の製造方法は、複数の半導体素子を形成したウエハの裏面に樹脂層を設ける工程と、樹脂層を設けたウエハをダイシングして個別の磁電変換素子用ペレットにする工程と、磁電変換素子用ペレットを、樹脂層を介してリードフレームに固着する工程と、磁電変換素子用ペレット上の電極をリードフレームと結線する工程とを具え、該樹脂層が厚み1〜50μmであり、前記樹脂層の樹脂がガラス転移点60〜160℃、接着活性温度170〜350℃、および熱伝導率0.2〜3.5W/m/℃を有している。

(もっと読む)

ホール素子の製造方法およびホール素子

【課題】移動度の高い単結晶の化合物半導体薄膜からなるホール素子を得る。

【解決手段】半導体薄膜形成用の支持基板に、第1シリコン層11の一方の面側に酸化皮膜よりなる絶縁層12を介して第1シリコン層11よりも薄層の第2シリコン層13が形成されているSOI基板を用い、第2シリコン層13上に単結晶の化合物半導体薄膜14を形成して4層構造の積層体10Bとし、積層体10Bの化合物半導体薄膜14側に接着剤22を介してコア基板21をさらに積層したのち、SOI基板を除去して化合物半導体薄膜14を露出させ、露出した化合物半導体薄膜14を所定にパターニングして複数の素子チップを作成し、その各素子チップにそれぞれ一対の入力用電極と出力用電極とを含む電極部を形成したのち、コア基板をダイシングして複数のホール素子を得る。

(もっと読む)

ホール素子の製造方法およびホール素子

【課題】ホール素子を製造するにあたって、半導体単結晶材料の材料効率をよくするとともに、素子と電極との電気的接続を信頼性の高いものとし、また、ダイシングブレードの長寿命化をはかる。

【解決手段】製造上の支持基板側で半導体単結晶薄膜からホール素子のチップ14aを剥離可能に形成し、これとは別工程で、ホール素子の大きさに予め切り出されたコア基板21上に絶縁層22を形成し、その絶縁層22上に導電性接着剤を用いてそれぞれ一対の入力用電極23,23と出力用電極24,24とを含む電極部25を形成し、上記支持基板から剥離したチップ14aをコア基板21の電極部25に実装する。

(もっと読む)

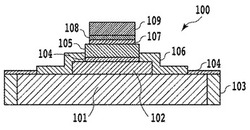

半導体装置及びその製造方法

【課題】低保磁力と低い残留磁束密度をもつ軟磁性膜を備え、この軟磁性薄膜で磁気収束する半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板1に設けられたホール素子2と、このホール素子1上に設けられた軟磁性薄膜6とを備え、軟磁性薄膜6が、少なくともホウ素を含有している。半導体基板1上で、かつホール素子2上に設けられた有機絶縁膜4と、この有機絶縁膜4と軟磁性薄膜6との間に設けられた金属導電層5とを備え、軟磁性薄膜6が、金属導電層5上で少なくとも1個以上のホール素子2の感磁部を覆うように配置されている。

(もっと読む)

回転状態検出装置

【課題】重金属汚染の影響による、検出精度の低下が抑止された回転状態検出装置を提供する。

【解決手段】半導体基板の厚さ方向に電流を流す少なくとも2つの電流端子と、厚さ方向に流れる電流と鎖交する磁束によって生じたホール電圧を検出する2つの電圧端子と、を有する縦型ホール素子と、該縦型ホール素子の出力信号に基づいて、回転体の回転状態を検出する検出部と、を備え、縦型ホール素子は、半導体基板に少なくとも3つ形成され、その内の2つの縦型ホール素子は、それぞれの縦型ホール素子における電圧端子間を結ぶ線分のなす角度θが0°より大きく180°より小さくなるように形成されており、検出部は、角度θを形成する2つの縦型ホール素子の出力信号を用いてアークタンジェント演算を行う演算部と、残りの縦型ホール素子の出力信号をパルス信号に変換する変換部と、を有する

(もっと読む)

半導体素子

【課題】特性劣化が小さい半導体素子を提供する。

【解決手段】本発明に係る半導体素子は、基板上に形成されたメサ構造を有する化合物半導体膜1と、化合物半導体膜1上に形成された短絡電極2と、外部との電気的接続を行うための取り出し電極3とを備える。短絡電極2および取り出し電極3は、化合物半導体膜1のメサ部分に接合する。取り出し電極3と化合物半導体膜1のメサ構造の長辺端部との接合面は、(111)面、(1−1−1)面、(−11−1)面、および(−1−11)面に平行な面のうち、少なくとも1つの面に対して−15°〜+15°の範囲であり、(11−1)面、(1−11)面、(−111)面、および(−1−1−1)面に平行な面に対して−15°〜+15°の範囲では、接合部が無いように形成されたことを特徴とする。

(もっと読む)

磁場センサ

【課題】平面的・空間的に分布し且つ動的な磁場の測定を実現可能とする磁気センサを提供する。

【解決手段】薄膜ホール効果素子THD、駆動回路DV、読出回路RD、検出制御配線SL1からSLm、検出出力配線RL1からRLnで構成された複数の要素回路PX11からPXmnをマトリクス状に配置して磁場センサ1を構成する。

(もっと読む)

半導体素子

【課題】リードフレーム及び半導体チップを封止するモールド樹脂とを備える半導体素子において、高温での特性劣化を抑制した半導体素子を提供すること。

【解決手段】半導体素子は、Cuを含むリードフレーム bと、リードフレーム b上に配置された半導体チップ aと、リードフレーム b及び半導体チップ aを封止する、ハロゲンを含有しないモールド樹脂 cとを備える。モールド樹脂 cには、難燃化材として、SnO3、CuO、Fe2O3、MoO3等の金属酸化物、Al(OH)3、Mg(OH)2、ZnSn(OH)6等の金属水酸化物、2ZO・3B2O3・3.5H2O、(NH4)2O・5B2O3・8H2O等のホウ酸を含有する化合物等を含むエポキシ樹脂を用いることができる。また、モールド樹脂 cは、主鎖にベンゼン環を有する安定で炭化しやすい化合物や原子間の結合が強い有機化合物を含むエポキシ樹脂であってもよい。

(もっと読む)

強磁性物質のドメイン構造および多重状態を用いた磁気記憶素子

【課題】磁気情報の記録される強磁性半導体層(magnetic Semiconductors、MS)自体をセンサー層として同時に利用することにより、磁気記録素子の構造を簡単にして工程を短縮し、生産単価を節減するばかりか、さらに多重ドメイン状態を利用した巨大な平面ホール効果(Planar Hall Effect)または磁気抵抗(Magnetoresistance)を測定して多重状態の情報を記録することができる記憶素子を提供する。

【解決手段】基板110と、前記基板110上に形成され、多重ドメイン状態を用いて多重の状態を平面ホール効果または磁気抵抗値を通じて貯蔵しセンシングする強磁性半導体層120と、前記強磁性半導体層上に形成された絶縁膜130と、前記絶縁膜上に形成された第1電流ライン140と、前記第1電流ライン上に形成された絶縁膜150と、前記絶縁膜上に形成された第2電流ライン160と、を含む。

(もっと読む)

ホール素子アレイ

【課題】平面的な磁界の位置を精度よく検出することが可能なホール素子アレイを提供する。

【解決手段】格子状の位置にモノリシックに形成され、ほぼ90度で交わる十字形の4つの頂部に接続部13を有し、対向するそれぞれの接続部13間に通電可能に形成された複数の半導体活性層11と、周辺部に折り返し部を有し、この折り返し部を除くとそれぞれX軸の方向及びX軸の方向とはほぼ90度異なるY軸の方向に沿って、隣接する半導体活性層11の接続部13同士を接続し、半導体活性層11内の一方の対向する接続部13間に電流を流せるように設けられたX列及びY列配線21、23と、X列及びY列配線21、23を介して接続された半導体活性層11のそれぞれの端部となる接続部13と接続された2個ずつの入出力電極31と、折り返し部と接続された出力電極33とを備える。

(もっと読む)

回転センサ

【課題】小型化に優れた回転センサを提供する。

【解決手段】半導体基板10に縦型ホール素子11が作り込まれ、半導体基板10の表面に平行な磁界を検出する。半導体基板10上に磁気抵抗素子12,13が形成され、半導体基板10の表面に平行な磁界の強さにより抵抗値が変化する。arctan演算器によって、磁気抵抗素子12により得られる信号と磁気抵抗素子13により得られる信号をarctanの演算をする。パルス化回路により、縦型ホール素子11の出力信号をパルス化する。合成器によりarctan演算器による信号と、パルス化回路による信号を合成して0〜360°の角度においてリニアな出力が得られる。

(もっと読む)

化合物半導体積層体

【課題】InAs層等の活性層を直接GaAs等の基板上に形成した構造の化合物半導体積層体であって、信頼性が高く、かつ、バルク単結晶に対して電子移動度の低下が小さい化合物半導体積層体を提供すること。

【解決手段】本発明に係る化合物半導体積層体は、GaAs基板上にInAs層を0.3μm以上と厚く形成し、そのInAs層上にInAs層と基板に平行方向の格子定数が等しく、基板に垂直方向の格子定数差が3%以内の化合物半導体保護層を形成することを特徴とする。すなわち、GaAs、InP、Siのバルク単結晶板、またはそれらの薄膜基板上に、直にInxGa1−xAsySb1−y(0≦x≦0.5、0≦y≦1)を活性層として、0.3μm以上3μm以下の厚さで形成する。この活性層には、導電性の小さな半導体層を保護層として直に形成する。

(もっと読む)

1 - 20 / 30

[ Back to top ]