Fターム[5F092BD15]の内容

ホール/MR素子 (37,442) | ホール素子、MR素子以外の素子 (1,073) | 材料 (835) | 非磁性体 (381) | 半導体 (125)

Fターム[5F092BD15]に分類される特許

81 - 100 / 125

ソリッドステート材料

ホスト材料と量子スピン欠陥とを含むソリッドステートシステムであって、量子スピン欠陥が室温で約300μs以上のT2を有し、ホスト材料が、約20ppb以下の全窒素濃度を有する単結晶CVDダイヤモンドの層を含み、量子スピン欠陥が形成されている所に最も近い表面上の点に中心がある約5μmの半径の円によって定義される領域内の単結晶ダイヤモンドの表面粗さRqが約10nm以下であるソリッドステートシステム、ソリッドステートシステムの調製方法及び約20ppb以下の全窒素濃度を有する単結晶ダイヤモンドのスピントロニクス用途での使用を開示する。 (もっと読む)

磁気センサー

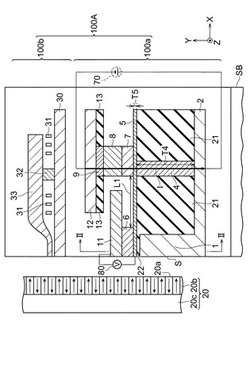

【課題】磁化自由層へスピン流を注入し易くすることにより、出力効率を向上させることが可能な磁気センサーを提供することを目的とする。

【解決手段】磁気センサー100aにおいて、非磁性導電層5と、非磁性導電層5の第一の部分上に設けられた磁化自由層6と、非磁性導電層5の第一の部分とは異なる第二の部分上に設けられた磁化固定層7と、非磁性導電層5及び磁化自由層6を間に挟んで対向する上部第一磁気シールド層11及び下部第一磁気シールド層1と、非磁性導電層5及び磁化固定層7を間に挟んで対向する上部第二磁気シールド層12及び下部第二磁気シールド層2と、下部第二磁気シールド層2と非磁性導電層5との間に設けられた第一電気絶縁層21と、下部第二磁気シールド層2と非磁性導電層5とを電気的に接続する第一電極層4と、を備え、非磁性導電層5を間に介して、磁化固定層7と第一電極層4とが互いに対向していることを特徴とする。

(もっと読む)

スピンFET

【課題】 ハーフメタルと同じ機能を室温で実現するスピンFETを提供する。

【解決手段】 半導体基板1は(100)Si、トンネル障壁層4,6は(100)MgO、ソース電極5及びドレイン電極7はそれぞれ(100)CoXFe1−X(0≦X≦1)から構成する。ソース電極5の磁化の向きMSは固定されており、ドレイン電極7の磁化の向きMDは外部から変更することができる。この素子は、ハーフメタルを用いてないにも拘らず、室温でスピンFETを実現することができる。

(もっと読む)

磁気センサー

【課題】積層方向の高さを低くして小型化を達成することにより、分解能を向上することが可能な磁気センサーを提供することを目的とする。

【解決手段】磁気センサー100aにおいて、非磁性導電層5と、非磁性導電層5の第一の部分上に設けられた磁化自由層6と、非磁性導電層5の第一の部分とは異なる第二の部分上に設けられた磁化固定層7と、非磁性導電層5及び磁化自由層6を間に挟んで対向する上部第一磁気シールド層11及び下部第一磁気シールド層1と、非磁性導電層5及び磁化固定層7を間に挟んで対向する上部第二磁気シールド層12及び下部第二磁気シールド層2と、下部第二磁気シールド層2と非磁性導電層5との間に設けられた電気絶縁層3と、を備え、下部第一磁気シールド層1は下部第二磁気シールド層2よりも非磁性導電層5に近く配置されている。

(もっと読む)

スピン依存伝達特性を有する電界効果トランジスタ及びそれを用いた不揮発性メモリ

【課題】ソース及びドレインに強磁性体によるショットキー接合を用いた金属−絶縁体−半導体電界効果トランジスタ(MISFET)を提供すること。

【解決手段】強磁性体であって、一方のスピンに対しては金属的なバンド構造(以下、「金属的スピンバンド」と称する。)を、他方のスピンに対しては半導体的又は絶縁体的なバンド構造(以下、「半導体的スピンバンド」と称する。)をとるハーフメタルからなり、スピン偏極した伝導キャリアを注入する強磁性ソースと、該強磁性ソースから注入されたスピン偏極した前記伝導キャリアを受けるハーフメタルからなる強磁性ドレインと、前記強磁性ソースと前記強磁性ドレインとの間に設けられ、前記強磁性ソース及び前記強磁性ドレインのそれぞれと接合した半導体層と、前記半導体層に対して形成されるゲート電極とを有することを特徴とするトランジスタ。

(もっと読む)

強磁性積層構造及びその製造方法

【課題】良好な界面特性をもつ強磁性薄膜、絶縁性薄膜、及び化合物半導体からなる強磁性積層構造を得る。

【解決手段】この磁性体積層構造10においては、化合物半導体1上に絶縁性薄膜2及び強磁性薄膜3が順次形成されている。絶縁性薄膜2は、蛍石型構造をもつフッ化化合物からなる。強磁性薄膜3は、Fe又はFeCo合金からなる強磁性体である。この強磁性積層構造10は、強磁性薄膜3から絶縁性薄膜2を通して化合物半導体1にスピン偏極電子が注入されて使用される。例えば、この強磁性積層構造10をスピンLEDに用い、化合物半導体1を発光層としても用いることができる。この場合には、この構造における各界面の結晶欠陥が少ないために、スピン偏極電子の発光層への高い注入効率が得られるため、高効率のスピンLEDを得ることができる。

(もっと読む)

磁気抵抗効果素子及びスピンMOS電界効果トランジスタ

【課題】 スピン分極率の高いフルホイスラー合金と反強磁性結合を形成する磁性体を含む、TMR比が高い磁気抵抗効果素子を提供する。

【解決手段】 強磁性体層11上には絶縁体層12が形成されている。絶縁体層12上にはフルホイスラー合金層13が形成され、フルホイスラー合金層13上には、面心立方格子構造を有する強磁性体層14が形成されている。さらに、強磁性体層14上には非磁性層15が形成され、非磁性層15上には強磁性体層16が形成されている。

(もっと読む)

スピンフィルタ効果素子及びスピントランジスタ

【課題】素子抵抗が低く、且つ、スピン偏極電子注入効率、又はスピン依存散乱効率の高いスピンフィルタ効果素子、及び、そのようなスピンフィルタ効果素子を用いたスピントランジスタを提供する。

【解決手段】本発明に係るスピントランジスタ10は、強磁性層SMを含む強磁性積層体を有するソース電極層3と、強磁性層DMを含む強磁性積層体を有するドレイン電極層7と、ソース電極層3及びドレイン電極層7が設けられた半導体層9と、半導体層9に直接又はゲート絶縁層GIを介して設けられたゲート電極層GEとを備え、ソース電極層3とドレイン電極層7のうち少なくとも一方は、半導体層9と強磁性積層体SM、DMとの間に介在する酸化物半導体層SO、DOをさらに有し、酸化物半導体層SO、DOは、半導体層9と、強磁性積層体との間のトンネル障壁を形成することを特徴とする。

(もっと読む)

半導体スピンデバイス及びスピンFET

【課題】 MR比を高めることが可能な半導体スピンデバイス、及び、特に、ソースとドレインとの間のMR比を向上させることが可能なスピンFETを提供する。

【解決手段】 スピンMOSFETにおけるソース側の界面抵抗とドレイン側の界面抵抗の値は本来異なっているが、この界面におけるトンネル障壁層の厚みを調整することにより、これらを略一致させる。これにより、スピンMOSFETにおける電気的な対称性が確保され、この場合の条件を解析すると、MR比が高くなることが見出された。

(もっと読む)

半導体装置

【課題】通常のC−MOSFET回路との整合性、混載可能性を保ちつつ安定した動作で、不揮発な再構成可能論理回路を構築することが可能なスピンMOSFETを備えた半導体装置を提供することを可能にする。

【解決手段】半導体基板と、半導体基板に離間して形成された第1ソース領域12および第1ドレイン領域14と、第1ソース領域と第1ドレイン領域との間に設けられる第1チャネル領域と、第1チャネル領域上に形成された第1ゲート絶縁膜と、ゲート絶縁膜上に形成された第1ゲート電極18と、第1ソース領域上に形成され第1方向に磁化容易軸を有する強磁性層を含む第1ソース電極Ms1と、第1ドレイン領域上に形成され第1方向に対して0度より大きく180度未満の角度をなす第2方向に磁化した強磁性層を含む第1ドレイン電極Md1と、第1ドレイン領域上に第1ドレイン電極と離間して形成され第2方向と略反平行な方向に磁化した強磁性層を含む第2ドレイン電極Md2と、を備えている。

(もっと読む)

磁気デバイス及び磁気メモリ

【課題】磁化反転しきい値が従来よりも低減された磁気デバイス、及びそのような磁気デバイスを用いた磁気メモリを提供する。

【解決手段】本発明に係る磁気デバイス30は、磁化固定層3、磁化自由層5、及び磁化固定層3と磁化自由層5とを接続する非磁性層4を有する磁気抵抗効果素子14と、磁化固定層3と磁化自由層5間に交流電流が重畳された直流電流を供給する重畳電流供給手段50とを備えることを特徴とし、従来よりも磁化反転しきい値が低減されている。

(もっと読む)

リコンフィギュラブル論理回路

【課題】高集積化が可能なリコンフィギュラブル論理回路を提供する。

【解決手段】それぞれが個別の制御データを送信可能な複数の制御線と、ソースおよびドレインが磁性体を含む複数のスピンMOSFETと、複数のスピンMOSFETの中から1つのスピンMOSFETを選択する選択部と、を有するマルチプレクサと、マルチプレクサによって選択されたスピンMOSFETのソースおよびドレインにおける磁性体の磁化が第1状態か第2状態かを判別する判別回路と、選択されたスピンMOSFETに書き込み電流を流し、選択されたスピンMOSFETにおける磁性体の磁化を第2状態にする第1の書き込み回路と、マルチプレクサによって選択されたスピンMOSFETに書き込み電流を流し、選択されたスピンMOSFETにおける磁性体の磁化を第1状態にする第2の書き込み回路と、を備えている。

(もっと読む)

トンネル磁気抵抗効果素子及びスピンMOS電界効果トランジスタ

【課題】規則性の高い結晶構造を持つホイスラー合金を用いたTMR比が高いトンネル磁気抵抗効果素子を提供する。

【解決手段】体心立方格子構造を有する強磁性層12上には、体心立方格子構造を有するCr層13が形成されている。さらに、Cr層13上には、ホイスラー合金層14、トンネルバリア層15、ホイスラー合金層16が順次形成されている。

(もっと読む)

半導体スピンデバイス及びスピンFET

【課題】 MR比を高めることが可能な半導体スピンデバイス、及び、特に、ソースとドレインとの間のMR比を向上させることが可能なスピンFETを提供する。

【解決手段】 スピンMOSFETにおけるソース側の界面抵抗とドレイン側の界面抵抗の値は本来異なっているが、この界面において不純物を添加することにより、これらを略一致させる。これにより、スピンMOSFETにおける電気的な対称性が確保され、この場合の条件を解析すると、MR比が高くなることが見出された。

(もっと読む)

スピンホール効果素子を用いた磁気センサ、磁気ヘッド及び磁気メモリ

【課題】強磁性層が1層のみで構成されるシンプルな構造のスピンホール効果素子を用いて、熱揺らぎを低減して高感度な信号検出を実現する磁気センサを得る。

【解決手段】非磁性体スピンホール効果層13,非磁性絶縁体層12,強磁性層11が積層された積層膜と、非磁性体スピンホール効果層13の側面に接続された非磁性体端子対141,142と、積層膜の膜厚方向に電流を印加する手段161とを備え、非磁性体スピンホール効果層13の厚みは、非磁性体スピンホール効果層を構成する材料のスピン拡散長の2倍よりも薄く、外部磁場により磁化された強磁性層11の磁化の向きを、非磁性体端子対141,142の両端に生じる電圧の極性によって検出する。

(もっと読む)

スピントランジスタおよびその制御方法

【課題】Rashbaスピン軌道相互作用とキャリア経路の分岐により、キャリアスピン上向き下向きを制御することを可能とし、さらにスピン偏極度に依存して、ドレイン電流が流れる超伝導接合を用いることにより、ドレイン電流の大きさをゲート電極で制御するスピントランジスタを実現する。

【解決手段】強磁性体電極(ソース)101と、超伝導体電極(ドレイン)102と、第1ゲート電極103と、第2ゲート電極104と、ゲートコンタクト層105と、2次元電子ガスが形成されているチャネル層106と、スペーサ層107と、キャリア供給層108と、バッファ層109と、基板110とを備えて、Rashbaスピン軌道相互作用とキャリア経路の分岐により、キャリアスピン上向き下向きを制御することを可能とするゲート電極と、超伝導体により形成されたドレイン電極を用いることにより、スピン偏極度によりドレイン電流が制御可能である。

(もっと読む)

スピントランジスタ及びそれを用いた不揮発性メモリ

【課題】トランジスタ内に含まれる強磁性体に磁化状態によって情報を記憶し、キャリアのスピンの向きに依存するトランジスタの出力特性を用いて情報を読み出す不揮発性メモリを提供すること。

【解決手段】絶縁性の強磁性体からなるトンネル障壁385と該トンネル障壁385を挟み込む強磁性体からなるソース381及び非磁性体または強磁性体からなるドレイン383とにより形成されるトンネル接合構造と、前記トンネル障壁385に対して形成されるゲート電極391と、を有するトランジスタ。

(もっと読む)

スピントランジスタ及びそれを用いた不揮発性メモリ

【課題】トランジスタ内に含まれる強磁性体に磁化状態によって情報を記憶し、キャリアのスピンの向きに依存するトランジスタの出力特性を用いて情報を読み出す不揮発性メモリを提供すること。

【解決手段】絶縁性の非磁性体からなるトンネル障壁365と該トンネル障壁365を挟み込む強磁性体からなるソース361及び強磁性体からなるドレイン363とにより形成されるトンネル接合構造と、前記トンネル障壁365に対して形成されるゲート電極371と、を有するトランジスタ。

(もっと読む)

スピントランジスタ

【課題】 スピン偏極したキャリアを、ドレインから効率よく取り出すことが可能なスピントランジスタを提供する。

【解決手段】 スピントランジスタ1は、強磁性体からなるソース20と、強磁性体からなるドレイン30と、ソース20及びドレイン30とショットキー接触を成す接触面を有する第1導電型の半導体層10と、接触面とは反対側の半導体層10の面上に直接又は絶縁体層12を介して設けられたゲート電極40と、を備えたスピントランジスタにおいて、ソース20と半導体層10との界面でのショットキー障壁の高さがΦBであるとき、少なくともソース20付近の半導体層10の不純物ドーピング濃度が(20×ΦB−1)×1018cm−3以上2×1019cm−3以下である。

(もっと読む)

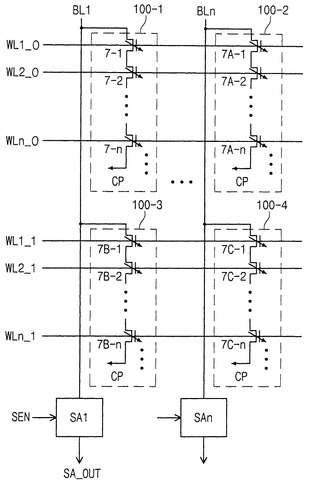

磁気抵抗ラム

【課題】セル構造が簡単かつセルサイズが小さく、従って製造工程が容易な磁気抵抗ラムを提供すること。

【解決手段】1つのビットラインとセルプレートとの間にNAND型に直列連結され、各々のゲートに複数のワードラインの信号が印加されるMRAMセルグループ、及び前記1つのビットラインに連結されセンスアンプイネーブル信号が印加されると、前記ビットラインに印加されたデータをセンシングするセンスアンプを備え、もしくは、

ビットラインとセルプレートとの間にNAND型に直列接続され、各々のゲート端子に複数のワードラインの信号が印加されるMRAMセルグループ、及び前記ビットラインに接続され前記MRAMセルグループに流れる電流を電圧に変換した後、前記MRAMセルグループ内のMTJの磁気分極方向の差による多重データを検出する多重データ検出回路を備える。

【選択図】図15  (もっと読む)

(もっと読む)

81 - 100 / 125

[ Back to top ]