Fターム[5F101BA07]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG配置 (488) | 他ゲート重なり (179) | CG重なり (168)

Fターム[5F101BA07]に分類される特許

1 - 20 / 168

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

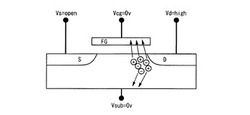

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

二重層フローティングゲートを備えているEPROMセル

【課題】インクジェットペンコントロールチップの既存の層を利用して製造できるEPROMを提供する。

【解決手段】EPROMセル70は、ソース領域及びドレイン領域を有する半導体基板52と、第1の金属層60と電気的に相互接続されている半導体ポリシリコン層56を含むフローティングゲート72と、第2の金属層64を含むコントロールゲートとを備えている。フローティングゲート72は、ソース領域及びドレイン領域に隣接して配置され、第1の誘電体層54によって半導体基板52から分離され、コントロールゲートの第2の金属層64は、第1の金属層60との間にある第2の誘電体層62を介して、第1の金属層60と容量結合されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】STIの形成によるウェル拡散層の不純物濃度の変化を抑制し、かつ、ウェル拡散層のドーズロスを抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。メモリセル領域には、複数のメモリセルが半導体基板上に形成されている。周辺回路領域には、複数のメモリ素子を制御する複数の半導体素子が形成されている。素子分離領域は、複数のメモリセル間を分離し、あるいは、複数の半導体素子間を分離する。周辺回路領域において半導体素子が形成されているアクティブエリアの不純物濃度は、半導体基板の表面に対して水平方向に素子分離領域の側面からアクティブエリアの内部へ向かって低下している。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】低いビットコストで積層化可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1メモリセルアレイ層10と、第1絶縁層31と、第2メモリセルアレイ層20とを有する。第1メモリセルアレイ層10は、複数の第1メモリセルMC1を具備する第1NANDセルユニットNU1を有する。第1メモリセルMC1は、第1半導体層11と、その上に形成された第1ゲート絶縁膜12と、第1浮遊ゲート13とを有する。第2メモリセルアレイ層20は、複数の第2メモリセルMC2を具備する第2NANDセルユニットNU2を有する。第2メモリセルMC2は、第2浮遊ゲート23と、第2ゲート絶縁膜22と、第2半導体層21とを有する。上下に連続する第1及び第2浮遊ゲート13,23の第1の方向の両側面に第1の方向と直交する第2の方向に延びる制御ゲート33が形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込みを高速化した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置110は、ベース半導体層10aと、電極70aと、チャネル半導体層30aと、ベーストンネル絶縁膜20aと、チャネルトンネル絶縁膜40aと、電荷保持層50aと、ブロック絶縁膜60aと、を有するメモリ部MC1を備える。チャネル半導体層30aは、ベース半導体層10aと電極70aとの間に設けられ、電極70aに対向するチャネル部31aを含む。ベーストンネル絶縁膜20aは、ベース半導体層10aとチャネル半導体層30aとの間に設けられる。チャネルトンネル絶縁膜40aは、電極70aとチャネル部31aとの間に設けられる。電荷保持層50aは、電極70aとチャネルトンネル絶縁膜40aとの間に設けられ、電荷を保持する。ブロック絶縁膜60aは、電極70aと電荷保持層50aとの間に設けられる。

(もっと読む)

不揮発性半導体記憶装置

【課題】素子領域内に含まれる不純物の拡散を抑制する。

【解決手段】不揮発性半導体記憶装置は、基板101と、前記基板101内に形成されたウェル領域102とを備える。前記装置は、前記ウェル領域102内に形成された素子分離溝Tにより、前記基板の主面に平行な第1方向に延び、前記第1方向に垂直な第2方向に互いに隣接するよう区画された複数の素子領域103と、前記素子分離溝T内に埋め込まれ、前記素子領域103同士を分離する素子分離絶縁膜104とを備える。前記装置は、前記複数の素子領域103の内部に、前記複数の素子領域のそれぞれを上部素子領域103Aと下部素子領域103Bとに分断するよう形成され、前記ウェル領域102内に注入された不純物の拡散を抑制する第1の拡散抑制層111と、前記上部素子領域103Aの前記第2方向に垂直な側面に形成され、前記不純物の拡散を抑制する第2の拡散抑制層112とを備える。

(もっと読む)

ボトムポリ制御ゲートを使用するPMOSフラッシュセル

【課題】制御ゲートが占有する面積を大幅に減らし、PMOSメモリ回路の密度を大幅に向上させることができるボトムポリ制御ゲートを使用するPMOSフラッシュセルを提供する。

【解決手段】2つのトランジスタのPMOSメモリセルは、SG−PMOS150a、FG−PMOS150b及び制御ゲート125を備える。SG−PMOS150aは、n型ウェル110中に設けられたドレイン及びソースを有する。FG−PMOS150bは、n型ウェル110中に設けられたソース及びドレインを有する。SG−PMOS150aのドレインとFG−PMOS150bのソースとは同じである。制御ゲート125は、第1のポリシリコン層からなり、アイソレーション構造115上に形成され、FG−PMOS150bの浮遊ゲート135bの延伸部分と重畳する。

(もっと読む)

半導体装置の製造方法

【課題】メモリセル領域と高電圧トランジスタとの高濃度不純物拡散領域を同時にイオン注入で形成し、且つ高電圧トランジスタ側の方が浅くなるように形成する。

【解決手段】シリコン基板1にメモリセル領域にゲート電極MG、SGを形成し(図3(b))、周辺回路領域にゲート電極PG(図3(c))を形成する。周辺回路領域のゲート電極PGは、高電圧トランジスタについては厚い膜厚のゲート絶縁膜11が形成されている。ゲート絶縁膜11を残した状態でTEOS酸化膜9を成膜し、スペーサ加工をする。この時、スペーサ9aを形成すると共に、ゲート絶縁膜11を半分程度エッチングして11aとする。TEOS酸化膜10を形成後に高濃度不純物拡散領域1d、1eをイオン注入で深さd1、d2で形成する。高電圧トランジスタについてはゲート絶縁膜11aを介して行うので、浅く形成される。

(もっと読む)

半導体装置

【課題】書き込みおよび消去特性が良好で、記憶情報の不揮発性が高い不揮発性記憶装置を提供する。

【解決手段】不揮発性記憶装置は、第1不純物領域1、第2不純物領域2、並びに第1不純物領域1および第2不純物領域2のいずれとも離間して形成された一組のソース領域3およびドレイン領域4、が区画された半導体基板10と、半導体基板10の上に形成された絶縁膜と、フローティングゲート30と、を有し、フローティングゲート30は、平面視において、第1部分31は第1不純物領域1に重複し、第2部分32は第1不純物領域1および第2不純物領域2の間に位置し、第3部分33は一組のソース領域3およびドレイン領域4の間に位置し、フローティングゲート30の第3部分33と半導体基板10との間に位置する絶縁膜は、フローティングゲート30の他の部分と半導体基板10との間に位置する絶縁膜よりも厚みが大きい。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置の特性の低下を抑制しつつ、メモリセルの微細化をはかった半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、基板101と、基板上に形成され、FN(Fowler-Nordheim)トンネル膜として機能するゲート絶縁膜111と、ゲート絶縁膜上に形成された第1の浮遊ゲート112と、第1の浮遊ゲート上に形成され、FNトンネル膜として機能する第1のゲート間絶縁膜113と、第1のゲート間絶縁膜上に形成された第2の浮遊ゲート114と、第2の浮遊ゲート上に形成され、電荷ブロック膜として機能する第2のゲート間絶縁膜115と、第2のゲート間絶縁膜上に形成された制御ゲート116とを備える。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

半導体記憶装置およびその制御方法

【課題】SOI構造の半導体記憶装置に電気的に書換え可能な不揮発性メモリを形成する手段を提供する。

【解決手段】第1の拡散層16、第2の拡散層17、前記第1および第2の拡散層間に配置された第3の拡散層、および第4の拡散層21と、前記第1および第2の拡散層とそれぞれ一部がオーバーラップし、前記第3の拡散層上から前記第4の拡散層にかけて延在するフローティングゲート電極13と、前記第1の拡散層および前記第3の拡散層に、共通の第1の電位を与える第1の制御線31と、前記第2の拡散層に、第2の電位を与える第2の制御線37と、前記第4の拡散層に、第3の電位を与える第3の制御線33と、を備え、前記フローティングゲート電極が前記第4の拡散層とオーバーラップした面積が、前記第2の拡散層とオーバーラップした面積よりも大きく、前記第1および第3の拡散層とオーバーラップした合計の面積よりも小さい。

(もっと読む)

半導体記憶装置

【課題】記憶素子間の干渉が少ない半導体記憶装置を提供する。

【解決手段】半導体記憶装置1において、シリコン基板11の上層部分の一部にSTI16を設け、シリコン基板11の上層部分をY方向に延びる複数本のアクティブエリアAAに区画する。そして、上下方向(Z方向)におけるアクティブエリアAAの中間部分27の幅Wmを、上部26の幅Wu及び下部28の幅Wlよりも細くする。

(もっと読む)

半導体装置

【課題】メモリセル領域に隣接して配置された周辺回路の基板コンタクトプラグが高抵抗になるという不良を防止する。

【解決手段】メモリセル領域2に隣接し、第一および第二の周辺回路を有する周辺回路領域3と、第一の周辺回路に形成された第一の基板コンタクトプラグ16aと、第二の周辺回路に形成された第二の基板コンタクトプラグ16bと、第一および第二の基板コンタクトプラグに対応して半導体基板に形成されたシリサイド領域とを備え、メモリセル領域の端部から第一の周辺回路までの距離は、メモリセル領域の端部から第二の周辺回路までの距離より大きく、第一の基板コンタクトプラグの横断面形状は第二の基板コンタクトプラグの横断面形状より大きく構成した。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】ドレイン電流の制御性を向上させつつ、メモリセルを縦方向に積層するとともに、メモリセルにフィン構造を用いた場合においても、制御ゲート電極および電荷蓄積層の加工の難易度を低下させる。

【解決手段】ブロック層13、電荷蓄積層14およびトンネル酸化膜15を順次介してフィン状の制御ゲート電極12aに埋め込まれたチャネル領域を有するボディ層17を設ける。

(もっと読む)

不揮発性半導体記憶装置

【課題】デポジッション膜を形成することなく、ゲートとコンタクトのショートを抑制する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1のコントロールゲート14を、フローティングゲート13側に位置する第1側面と、第1側面の反対に位置する第2側面と、コントロールゲート14の第1側面側の上部に形成されたシリサイド領域22と、コントロールゲート14の第2側面側の上部に形成された突出部8とを含むように構成する。そのサイドウォール絶縁膜21は、シリサイド領域22を覆うことなく突出部8の少なくとも一部を被覆する第1部分と、第1部分から連続的に設けられ、第2側面に接触して第2側面を被覆する第2部分とを含むものとする。

(もっと読む)

不揮発性メモリの構造および製造プロセス

【課題】浮遊ゲート構造を有する不揮発性メモリおよびその製造プロセスを提供する。

【解決手段】不揮発性メモリは、基板と、基板に設けられ、その上に突き出た分離構造と、基板上に突き出た分離構造の側壁上にある導電性スペーサーとしての浮遊ゲートと、各浮遊ゲートと基板の間のトンネル層とを含む。また、不揮発性メモリの製造プロセスは、基板上に突き出た分離構造が基板に形成され、トンネル層が基板上に形成され、その後、浮遊ゲートが基板上に突き出た第1分離構造の側壁上に導電性スペーサーとして形成されることを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリセルを有する半導体装置において、メモリ周辺回路の信頼性を向上させることのできる技術を提供する。

【解決手段】メモリ周辺回路領域の高圧系nMISおよび高圧系pMISのゲート絶縁膜14を、半導体基板1の主面上に順次積層された下層の絶縁膜11b、電荷蓄積層CSLおよび上層の絶縁膜11tにより構成し、続いて上層の絶縁膜11t上に積層されたn型の導電膜により高圧系nMISのゲート電極GHnまたは高圧系pMISのゲート電極GHpを構成する。メモリ周辺回路領域の低圧系nMISおよび低圧系pMISのゲート絶縁膜8を、半導体基板1の主面上に形成された酸化シリコン膜により構成する。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】不揮発性メモリ素子及びその製造方法が提供される。本発明の不揮発性メモリ素子は、基板と、互いに対向するように垂直伸張する第1部及び第2部と、前記第1部及び第2部を連結する底部とを前記基板上に含む半導体構造物と、前記半導体構造物の前記第1部及び第2部に沿って離隔配置されて互いに直列に連結された複数のメモリセルと、を含む。本発明の不揮発性メモリ素子の製造方法は、互いに対向するように垂直伸張する第1部及び第2部と、前記第1部及び第2部を連結する底部と、を基板上に含む半導体構造物を前記基板上に形成する段階と、前記半導体構造物の前記第1部及び第2部に沿って離隔配置され、互いに直列に連結された複数のメモリセルを形成する段階と、を含む。

(もっと読む)

フラッシュ・メモリ・デバイスおよびその製造方法

【課題】 制御ゲートと浮動ゲートとの間にジグザグ容量を含み、浮動ゲートおよびチャネルに対する制御ゲートの結合を増大するフラッシュ・メモリ・デバイスを提供する。

【解決手段】 フラッシュ・メモリ・デバイスは、ウェハと、このウェハの上に配置されたゲート酸化物層と、このゲート酸化物層、ウェハ、またはそれらの組み合わせの上に配置された浮動ゲートであって、平坦な浮動ゲート部およびこの平坦な浮動ゲート部の選択された領域の上に配置された概ね矩形の浮動ゲート部を含む浮動ゲートと、浮動ゲートの上に配置された高K誘電材料と、高K誘電材料の上に配置された制御ゲートとを含み、高K誘電材料が浮動ゲートを制御ゲートに結合するジグザグ・パターンを形成する。

(もっと読む)

1 - 20 / 168

[ Back to top ]