Fターム[5F101BA14]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG形状構造 (858) | CG側壁 (37)

Fターム[5F101BA14]に分類される特許

1 - 20 / 37

導電性側壁スペーサを有する不揮発性メモリ装置及びその製造方法

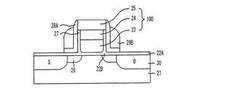

【課題】従来の窒化膜側壁を電荷トラップ媒体に利用する場合の信頼性劣化を改善した不揮発性メモリ装置を提供する。

【解決手段】半導体基板21上のゲート絶縁膜22Aと、該ゲート絶縁膜上に順に積層して形成された第1電極膜23、第2電極膜24、及びハードマスク膜25を有するゲート100と、該ゲートの第1電極膜23及び第2電極膜24の両側壁に形成された一対の再酸化側壁スペーサ27と、該再酸化側壁スペーサ及びゲート100のハードマスク膜25の両側壁上に形成された一対の側壁スペーサ28Aと、一対の側壁スペーサ28A上に形成された、電荷を捕獲及び放出する一対の導電性側壁スペーサ29Bと、半導体基板21内に形成された一対のLDD領域26と、半導体基板21内に形成されたソース/ドレイン領域30とを備え、導電性側壁スペーサ29Bが、ゲート100及び側壁スペーサ28Aよりも低い高さを有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】低いビットコストで積層化可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1メモリセルアレイ層10と、第1絶縁層31と、第2メモリセルアレイ層20とを有する。第1メモリセルアレイ層10は、複数の第1メモリセルMC1を具備する第1NANDセルユニットNU1を有する。第1メモリセルMC1は、第1半導体層11と、その上に形成された第1ゲート絶縁膜12と、第1浮遊ゲート13とを有する。第2メモリセルアレイ層20は、複数の第2メモリセルMC2を具備する第2NANDセルユニットNU2を有する。第2メモリセルMC2は、第2浮遊ゲート23と、第2ゲート絶縁膜22と、第2半導体層21とを有する。上下に連続する第1及び第2浮遊ゲート13,23の第1の方向の両側面に第1の方向と直交する第2の方向に延びる制御ゲート33が形成される。

(もっと読む)

メモリセル電荷記憶素子あたりに二重のコントロールゲートを有するフラッシュメモリセルアレイ

【課題】フローティングゲートが少なくとも2つのコントロールゲートラインと容量的に結合するようになっているフラッシュNANDタイプのEEPROMシステムの提供。

【解決手段】コントロールゲートラインはフローティングゲートの側壁と結合するようにフローティングゲート間に位置し、メモリセルの結合比が望ましく高められる。フローティングゲートの選択された行の両側の両方のコントロールゲートラインは普通同じ電圧まで高められ、隣接するフローティングゲートの選択されていない行に結合された第2のコントロールゲートラインは低く保たれる。選択されたフローティングゲートの領域でその電圧を選択的に高めるために、コントロールゲートラインを基板と容量的に結合させる。フローティングゲートの長さとコントロールゲートラインの厚さとは、スペーサのエッチマスクを形成することによってプロセスの最小分解エレメントより小さくされ得る。

(もっと読む)

メモリセルのアレイを作製する方法、メモリセルのアレイ及びメモリセルのアレイにおいてメモリセルを動作させる方法

【課題】安価なメモリデバイスを提供する。

【解決手段】1F2当り少なくとも1ビットを記憶するよう構成されたメモリセルのアレイは、アレイの最小ピッチの半分に等しい距離で離間した電子メモリ機能を与える実質的に縦型の構造を含む。電子メモリ機能を与える構造は、ゲート当り1ビットを超えて記憶するよう構成されている。また、アレイは、実質的に縦型の構造を含むメモリセルに対する電気接点も含む。セルは、第1のソース/ドレイン領域に隣接したゲート絶縁物にトラップされた多数の電荷レベルの1つを有するようプログラムすることができる。これにより、チャネル領域は第1のしきい値電圧領域と第2のしきい値電圧領域とを有し、プログラムされたセルが低減されたドレインソース電流で動作する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリセルを有する半導体装置において、メモリ周辺回路の信頼性を向上させることのできる技術を提供する。

【解決手段】メモリ周辺回路領域の高圧系nMISおよび高圧系pMISのゲート絶縁膜14を、半導体基板1の主面上に順次積層された下層の絶縁膜11b、電荷蓄積層CSLおよび上層の絶縁膜11tにより構成し、続いて上層の絶縁膜11t上に積層されたn型の導電膜により高圧系nMISのゲート電極GHnまたは高圧系pMISのゲート電極GHpを構成する。メモリ周辺回路領域の低圧系nMISおよび低圧系pMISのゲート絶縁膜8を、半導体基板1の主面上に形成された酸化シリコン膜により構成する。

(もっと読む)

NAND型フラッシュメモリおよびその製造方法

【課題】隣接するメモリセルMC間の干渉効果を低減ことが可能なNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリ100のメモリセルは、素子領域上にゲート絶縁膜を介して形成された柱状の浮遊ゲートと、素子領域のうち浮遊ゲートの両側に位置する領域に形成された拡散層と、浮遊ゲートの側面に形成されたIPD膜を介して前記浮遊ゲートの周囲を囲むように形成された制御ゲートと、を有する。

(もっと読む)

不揮発性メモリ及びマイクロコンピュータ

【課題】不揮発性メモリの消去動作における基板電流の最大値を低減すること。

【解決手段】本発明の不揮発性メモリ(2)は、半導体基板(30)に形成されたソース電極(53)及びドレイン電極(54)と、ソース電極とドレイン電極間の前記半導体基板上に形成された電荷トラップ層(52)と、電荷トラップ層上に配置されたゲート電極(50)とを有する不揮発性メモリセルがアレイ状に複数配列されて成る。不揮発性メモリは、ソース電極とゲート電極とに消去に必要な電圧を印加する消去モードを有する制御回路(33)を備える。前記消去モードにおいて、ゲート電極に電圧の印加を開始してから前記ゲート電極の電圧が消去に必要な所定電圧に達するまでの期間(63)が、ソース電極に電圧の印加を開始してから前記ソース電極の電圧が前記所定電圧に達するまでの期間(64)よりも長くされる。これによって、消去動作における基板電流の最大値が抑えられる。

(もっと読む)

NAND型不揮発性半導体記憶装置の製造方法及びNAND型不揮発性半導体記憶装置

【課題】NAND型不揮発性半導体記憶装置のリーク不良を低減し且つ未開口部分を低減する。

【解決手段】半導体基板上にゲート絶縁膜102、第1の電極103、第2の電極107及び第1のストッパ絶縁膜108を形成し且つ前記半導体基板101の表面に拡散層領域106を形成する工程と、前記拡散層領域106上の前記第1のストッパ絶縁膜108、前記第2の電極107及び前記第1の電極103をエッチングして開口部111及びコンタクト用ゲート110を形成する工程と、メモリセルゲート形成領域にインターポリ絶縁膜119及びコントロールゲート120を形成する工程と、前記コンタクト用ゲートを繋ぐようなソース線121及び個々の選択ゲートを繋ぐ配線層122を形成する工程と、を具備したことを特徴とするNAND型不揮発性半導体記憶装置の製造方法。

(もっと読む)

不揮発性半導体記憶装置、不揮発性半導体記憶装置の製造方法

【課題】基板にトレンチを形成することなく、メモリセルサイズの小さい不揮発性半導体記憶装置を提供する。

【解決手段】ゲート絶縁膜12を介して半導体基板4上に形成され、ゲート絶縁膜12と接する第1部分8aと、その第1部分8aの上面の一部から上方に延伸する形状を有する第2部分8bとを有するフローティングゲート8を備える不揮発性半導体記憶装置を構成する。また、その半導体基板4の表面に平行な平面を含むように、第1拡散層5と第2拡散層6とを形成する。半導体基板4の表層のチャネル領域上には、フローティングゲート8に並設されるコントロールゲート7を構成する。さらに、第1拡散層5に接続され、第1絶縁膜13を介して第1部分8aの第2側面及び第2部分8bの第1側面に形成された導電体膜を備える不揮発性半導体記憶装置を構成する。

(もっと読む)

不揮発性メモリ素子、その動作方法及びその製造方法

【課題】不揮発性メモリ素子、その動作方法及びその製造方法を提供する。

【解決手段】少なくとも一つの半導体層105と、半導体層105の内部にリセスされて配された複数の制御ゲート電極150と、複数の制御ゲート電極150と半導体層105との間に介在された複数の電荷保存層130と、複数の制御ゲート電極150を介して相互反対側に配され、半導体層105にそれぞれ容量結合された少なくとも一つの第1補助電極170a,及び少なくとも一つの第2補助電極170bと、を備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】消去ゲートとコントロールゲートとの間のシリサイド・ショートの発生確率を低減させる消去ゲートを備えた不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板1上に形成されたフローティングゲート3と、フローティングゲート3上に形成された消去ゲート10と、半導体基板表層のチャネル領域上にフローティングゲート3と並設され、フローティングゲート3及び消去ゲート10の一方の側面に形成されたコントロールゲート22と、消去ゲート10の上面に形成された第1シリサイド膜27と、コントロールゲート22の上面に形成された第2シリサイド膜26と、を備え、コントロールゲート22の上面の高さは、消去ゲート10の上面の高さと同じ若しくはそれよりも下方に位置することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】水素原子の拡散による特性変動が少ない半導体装置を提供することを課題とする。

【解決手段】半導体基板上に、ゲート絶縁膜を介してゲート電極を形成する工程と、前記半導体基板及び前記ゲート電極上に第一のシリコン窒化膜を形成する工程と、前記ゲート電極をマスクとして前記第一のシリコン窒化膜を介して不純物注入することにより前記半導体基板の表面層に拡散領域を形成する工程と、前記第一のシリコン窒化膜上に第二のシリコン窒化膜を形成する工程とを含み、前記第一のシリコン窒化膜が、前記第二のシリコン窒化膜より水素含有量が小さいことを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】セルコンタクトのアクティブ領域に対する位置合わせにずれが生じた場合でも、コンタクト抵抗を増大させない半導体装置及びその製造方法を提供する。

【解決手段】半導体基板20、半導体基板に設けられた素子分離膜21、層間絶縁膜60及び導電プラグ62を備えて構成される。半導体基板は、一方の主表面20a側に、第1の方向及び第2の方向に行列配列されたメモリセルを有している。導電プラグは、層間絶縁膜内に形成されていて、メモリセルと層間絶縁膜上に形成される配線74とを電気的に接続する。各メモリセルは、ゲート電極34と、一対の不純物拡散領域40を備えている。不純物拡散領域は、主表面側に金属シリサイド膜46を有している。導電プラグは、素子分離膜上と金属シリサイド膜上とに形成されている。金属シリサイド膜は、第1部分47と、第2部分48を備えていて、第1部分の厚みが第2部分の厚みよりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】砒素を含んだシリコン窒化膜に対して、燐酸を用いたウェットエッチングを行うと、ウェットエッチング液中に反応生成物(パーティクル)が発生し、汚染の原因になってしまう。

【解決手段】本発明の半導体装置の製造方法は、砒素が含まれている部分と砒素が含まれていない部分とを有するシリコン窒化膜を形成する工程と、ドライエッチングにより、前記シリコン窒化膜のうちの前記砒素が含まれている部分をエッチングする第1のエッチング工程と、ウェットエッチングにより、前記シリコン窒化膜のうちの前記砒素が含まれていない部分をエッチングする第2のエッチング工程と、を含む、ことを特徴とする

(もっと読む)

半導体メモリ装置の製造方法及び半導体メモリ装置の再生方法及び半導体メモリ装置の再出荷方法

【課題】情報データの書き込み及び消去を繰り返しても電荷保持特性の悪化を防ぐことが出来る半導体メモリ装置の製造方法、再生方法及び再出荷方法を提供する。

【解決手段】半導体基板に形成されたFET構造のメモリセルの複数からなり、メモリセルの複数の各々が単位ビットを記憶して情報データを保持している半導体メモリ装置の製造方法であって、メモリセルの複数を用意して、メモリセルの各々に情報データの各ビットを書き込む。そして、メモリセルの各々に情報データの各ビットを書き込んだ後、メモリセルの各々を所定の周囲温度の下に所定時間放置して、その後、メモリセルの各々に情報データの各ビットを書き込む。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】低いビットラインコンタクト抵抗を有する不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】第1及び第2フィン105a,105bを備え、第1導電型を有する半導体基板と、第1及び第2フィンの一端を連結する共通ビットライン電極160a,160bと、第1及び第2フィン105a,105bの一側面を覆い、第1及び第2フィン上を横切って延びる複数の制御ゲート電極150と、共通ビットライン電極160a,160bと複数の制御ゲート電極150との間に配置され、第1及び第2フィン105a,105bの一側面を覆い、第1及び第2フィン上を横切って延びる第1ストリング選択ゲート電極155aと、第1ストリング選択ゲート電極と複数の制御ゲート電極との間に配置され、第1及び第2フィンの一側面を覆い、第1及び第2フィン上を横切って延びる第2ストリング選択ゲート電極155bと、を備える不揮発性メモリ素子である。

(もっと読む)

半導体記憶装置及びこの半導体記憶装置への情報の記録方法

【課題】1セル当たりに必要なビット線の本数を増やすことなく、1メモリセルに3ビット以上の情報を記録可能にする。

【解決手段】半導体基板20の一方の主表面20a上に形成された制御電極下記憶部30と、御電極下記憶部上に形成された制御電極50と、第1及び第2不純物拡散領域24a及び24bと、第1及び第2抵抗変化部22a及び22bと、第1及び第2側壁記憶部40a及び40bとを備えて構成される。制御電極下記憶部は、トンネル酸化膜32、電荷蓄積膜34、及びトップ酸化膜36が順次に積層されて構成されている。第1及び第2側壁記憶部は、第1及び第2抵抗変化部上にそれぞれ形成されていて、トンネル酸化膜42a及び42b、電荷蓄積膜44a及び44b、及びトップ酸化膜46a及び46bが順次に積層されて構成される。

(もっと読む)

ソース側消去を伴うフローティングゲートメモリセルの半導体メモリアレイを形成する自己整合法及びこれによって形成されるメモリアレイ

【課題】ソース線の導電材料のブロックに面する鋭角縁部を備えたソース側消去メモリセルの設計及びその形成方法を提供すること

【解決手段】フローティングゲートメモリセルのアレイを形成する方法、及びこれによって形成されるアレイであり、各メモリセルが、第1導電型を有する半導体材料基板と、基板内に形成されたソース及びドレイン領域と、ソースの上方に配置され該ソースと電気的に接続された導電材料のブロックと、ソース領域の上方に配置され該ソース領域から絶縁された第1の部分とチャネル領域の上方に配置され該チャネル領域から絶縁された第2の部分とを有するフローティングゲートとを含む。フローティングゲートの第1の部分は、鋭角縁部で交わる傾斜上面及び側面を含む。チャネル領域の導電性を制御するために導電性制御ゲートがチャネル領域の上方に配置され該チャネル領域から絶縁される。

(もっと読む)

半導体記憶装置及びこれを備えた電子機器

【課題】仮想接地アレイ構造により構成された不揮発性メモリアレイにおいて、プログラム動作時の消費電力を低減する。

【解決手段】仮想接地アレイ構造により構成されたメモリセルアレイ内のメモリセルをプログラムする際、制御部100は、同一のワード線にゲート電極が接続された2つのメモリセルに並列にプログラムを行うように制御する。同一の制御線34s1、34s2、34s3、34s4に各2つのパスゲート35p1、35p5;35p2、35p6;35p3、35p7;35p4、35p8のゲート電極が接続されている。

(もっと読む)

半導体記憶装置、および半導体記憶装置の製造方法

【課題】空乏化を進めつつ、消去速度の劣化と閾値のばらつきを抑制する。

【解決手段】基板1と、導電路の始点となるソース領域2と、その終点となるドレイン領域3と、導電路が形成される領域上の第1絶縁膜4と、第1絶縁膜4上に形成され、所定値以下の濃度の不純物および所定値以上の濃度の水素原子が注入された浮遊ゲート5と、浮遊ゲート5を被覆する第2絶縁膜6と、第2絶縁膜6を介して浮遊ゲート5から分離して形成された制御ゲート8と、保護膜と、を備える。

(もっと読む)

1 - 20 / 37

[ Back to top ]