Fターム[5F101BA41]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | トラップ蓄積型 (3,039)

Fターム[5F101BA41]の下位に属するFターム

Fターム[5F101BA41]に分類される特許

21 - 40 / 64

半導体装置の製造方法

【課題】面方位が(110)面あるいはこれと等価な面であるシリコン層上に形成する酸化膜厚の制御を行うことのできる半導体装置の製造方法を提供すること。

【解決手段】面方位が(110)面あるいはこれと等価な面であるシリコン基板1表面の一部に、リンのイオン注入を行って、端部の不純物濃度が連続的に変化した第1の不純物領域2Aを形成する工程と、熱酸化を行って、シリコン基板1上に端部の厚さが連続的に変化したシリコン酸化膜3を形成する工程と、を含むこと、を特徴とする。

(もっと読む)

半導体装置

【課題】メモリセル間の干渉効果の抑制とセルの信頼性の維持の両方を実現する不揮発性メモリを備える半導体装置を提供する。

【解決手段】素子分離絶縁層STIと制御ゲート電極CGとの間でワード方向に隣り合う電流遮断層BLに実質的に挟まれるように、電流遮断層BLよりも誘電率が高い高誘電体層31を、その下面が電荷トラップ層24の頂面と同一または上方に位置するように設ける。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エッチングストッパ膜を有し、配線間容量の増大を抑制可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板11と、半導体基板11の表面上部に配設された層間絶縁膜29と、層間絶縁膜29に埋め込まれ、半導体基板11に対向する上面が層間絶縁膜29の上面と面一に配設され、互いに離間して配置された複数のビアプラグ31と、層間絶縁膜29及びビアプラグ31の表面上部に配設された層間絶縁膜39と、層間絶縁膜39によって分離され、ビアプラグ31と接続され、ビアプラグ31に対向する上面が層間絶縁膜39の上面と面一に配設され、層間絶縁膜39を挟んで相対向する側面に、層間絶縁膜29の側から順に、層間絶縁膜29とはエッチング性が異なり且つ層間絶縁膜39より比誘電率の高い側壁絶縁膜35、及び側壁絶縁膜35とはエッチング性が異なる側壁絶縁膜37を有する複数の第2配線33とを備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】電荷蓄積膜を備える半導体記憶装置に関し、電荷蓄積膜の電荷保持特性を向上させる。

【解決手段】ビット線とワード線とを有する半導体記憶装置(101)は、基板(111)と、前記基板上に形成された第1のゲート絶縁膜(121)と、前記第1のゲート絶縁膜上に形成された電荷蓄積膜(122)と、前記電荷蓄積膜上に形成された第2のゲート絶縁膜(123)と、前記第2のゲート絶縁膜上に形成されたゲート電極(124)とを備え、前記電荷蓄積膜のビット線方向の幅が、前記ゲート電極のビット線方向の幅よりも狭くなっている、又は、前記電荷蓄積膜のワード線方向の幅が、前記第1のゲート絶縁膜下の前記基板内に形成されるチャネル領域のチャネル幅よりも狭くなっている。

(もっと読む)

不揮発性メモリのプログラミング方法

【課題】メモリに書き込むための電圧、時間、及び電力を低減するための不揮発性メモリのプログラミング方法を提供する。

【解決手段】不揮発性メモリのプログラミング方法が提供される。その方法は、ソース又はドレインのキャリアを基板内へ注入すべくソース又はドレインに少なくとも電圧を印加する工程と、十分なエネルギーを有する基板内にあるキャリアが電荷記憶デバイスに到達すべく酸化層を通過することができるようにゲート又は基板に第3の電圧を印加する工程とを備える。

(もっと読む)

不揮発性半導体記憶素子、及び不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置が備える不揮発性半導体記憶素子を標準的なCMOSプロセスで製造するトランジスタを用いて構成する。

【解決手段】標準的なCMOSプロセスによるトランジスタ二個を一組とし備える記憶部200は、ソース・半導体基板間に発生するバンド間トンネル電流が流れる際に発生する正孔と電子を、半導体基板とゲート酸化膜の境界付近にある結晶欠陥にトラップさせる。結晶欠陥に正孔又は電子をトラップしたトランジスタは閾値が変化するので、記憶部200が備えるNMOSトランジスタ201とNMOSトランジスタ202の閾値の変化によるドレイン電流の差をSRAM部100が備えるセンスアンプ回路で検出することにより記憶されたデータの読み出しを行う。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体基板、および半導体基板の製造方法

【課題】容易にかつ低コストで従来のようなゲッタリング効果を得られるゲッタリングサイトを形成する半導体装置を得ることを目的とする。

【解決手段】本発明の一実施形態における半導体装置の製造方法は、(a)半導体基板1を準備する工程と、(b)半導体基板1の表面側からイオン注入し、半導体基板1の表層部にアモルファス層2を形成する工程と、(c)半導体基板1に熱処理を行ってアモルファス層2を再結晶化した再結晶層3を形成し、半導体基板1と再結晶層3との界面近傍に微少結晶欠陥4を形成する工程と、(d)再結晶層3に半導体素子5を形成する工程と、を備える。

(もっと読む)

不揮発性メモリ素子の動作方法

【課題】不揮発性メモリ素子の動作方法を提供する。

【解決手段】不揮発性メモリ素子の動作方法において、不揮発性メモリ素子の一つ以上の層に電荷を注入して不揮発性メモリ素子をリセッティングするステップと、不揮発性メモリ素子の一つ以上の層から前記電荷の少なくとも一部を除去して不揮発性メモリ素子をセッティングするステップと、を含む不揮発性メモリ素子の動作方法である。前記不揮発性メモリ素子は、複数のメモリセルの電荷保存層に電荷を注入してリセッティングされ、前記不揮発性メモリ素子は、前記複数のメモリセルのうち一つ以上の選択されたメモリセルの前記電荷保存層から前記電荷の少なくとも一部を除去してセッティングされる。

(もっと読む)

不揮発性メモリ装置及びその動作方法

【課題】不揮発性メモリ装置及びその動作方法を提供する。

【解決手段】少なくとも一つのメインストリング及び電荷供給ラインを備える不揮発性メモリ装置。それぞれのメインストリングは、複数のメモリセルトランジスタをそれぞれ備える第1サブストリングと第2サブストリングとをそれぞれ備える。電荷供給ラインは、それぞれのメインストリングの第1及び第2サブストリングに電荷を供給または遮断する。それぞれのメインストリングは、第1サブストリングに連結される第1接地選択トランジスタと、第1接地選択トランジスタに連結される第1サブストリング選択トランジスタと、第2サブストリングに連結される第2接地選択トランジスタと、第2接地選択トランジスタに連結される第2サブストリング選択トランジスタと、を備える。

(もっと読む)

不揮発性メモリ装置及びその形成方法

【課題】信頼性が向上した不揮発性メモリ装置及びその形成方法を提供する。

【解決手段】本発明の不揮発性メモリ装置は、基板に活性領域を定義する素子分離膜と、活性領域上に順次に位置する第1絶縁膜、非導電性の電荷貯蔵パターン、第2絶縁膜、及び制御ゲート線と、を備え、電荷貯蔵パターンは、水平部及び該水平部の周縁上に位置する突出部を含む。本発明によれば、電荷貯蔵パターンが素子分離膜上に形成されることなく活性領域上にのみ形成されるため、電荷貯蔵パターンに貯蔵された電子の移動による情報の歪曲現象を防止することができる。

(もっと読む)

抵抗素子を有する半導体装置及びその形成方法

【課題】本発明は、製造工程の間に相対的に安定に維持され、予測可能な抵抗値を有する抵抗素子を含む半導体装置とその形成方法を提供する。

【解決手段】この半導体装置は、第1領域と第2領域を備える基板と、第1領域の基板上の、第1ゲート絶縁膜及び該第1ゲート絶縁膜上の第1ゲート電極膜を備えた少なくとも一つの第1ゲート構造物と、を備える。

(もっと読む)

パッドオキサイドレイヤーを通じてチャージトラップレイヤー間で電子を移動させる不揮発性メモリ装置及びプログラミング方法

【課題】パッドオキサイドレイヤーを通じてチャージトラップレイヤーの間で電子を移動させる不揮発性メモリ装置及びプログラミング方法を提供する。

【解決手段】半導体基板と、半導体基板上に位置し、電子を保存できる第1チャージトラップレイヤーと、第1チャージトラップレイヤー上に位置するパッドオキサイドレイヤーと、パッドオキサイドレイヤー上に位置し、電子を保存できる第2チャージトラップレイヤーと、を備え、データを書き込むプログラミングモードで、パッドオキサイドレイヤーを通じて、第1チャージトラップレイヤーの第1エッジと第2チャージトラップレイヤーの第1エッジとの間で電子を移動させるか、またはパッドオキサイドレイヤーを通じて、第1チャージトラップレイヤーの第2エッジと第2チャージトラップレイヤーの第2エッジとの間で電子を移動させる不揮発性メモリ装置である。

(もっと読む)

不揮発性メモリ素子の動作方法

【課題】不揮発性メモリ素子の動作方法を提供する。

【解決手段】本発明は、複数のメモリセルを含む不揮発性メモリ素子において、複数のメモリセルのうち、データが記録された選択されたメモリセルに隣接するように連結された少なくとも一つのメモリセルのチャンネルを通じて、選択されたメモリセルのチャンネルにブースト電圧を誘導して記録されたデータを安定化させるステップを含むことを特徴とする不揮発性メモリ素子の動作方法を提供する。

(もっと読む)

不揮発性メモリ素子及びその動作方法

【課題】不揮発性メモリ素子及びその動作方法を提供する。

【解決手段】本発明は、ビットラインと共通ソースラインとの間にストリング選択トランジスタ、複数のメモリトランジスタ及び接地選択トランジスタを備え、ビットラインまたは共通ソースラインに消去電圧を印加して、複数のメモリトランジスタのデータを消去できる不揮発性メモリ素子である。

(もっと読む)

消去ゲートを用いて消去動作を行う半導体メモリ装置及び該半導体メモリ装置の製造方法

【課題】消去ゲートを用いて消去動作を行う半導体メモリ装置及び該半導体メモリ装置の製造方法を提供する。

【解決手段】半導体基板、電荷トラップ層及び少なくとも1つの消去ゲートを備える半導体メモリ装置。電荷トラップ層は、半導体基板上に位置し、流入された電子を保存する。少なくとも1つの消去ゲートは、チャージトラップレイヤの下に位置する。電荷トラップ層に保存された電子を除去する消去モードで、消去ゲートは、電荷トラップ層ホールを注入して、電荷トラップ層に保存された電子と注入されたホールとを再結合させる。

(もっと読む)

半導体集積回路

【課題】 信頼性高く不揮発記憶を書き込めるようにする。非記憶と不揮発記憶の両方、一時記憶(揮発記憶)と不揮発記憶の両方を一つの回路で行い得るようにする。

【解決手段】 前段回路の情報を状態検地強調回路Aを介して本段回路に書き込む。制御信号V selectがL、即ち/V selectがHの時、回路Aでは小電圧のVcc0とVss0が選択され、これが前段回路に印加される。この時、本段回路のn-Tr2のゲート-p型基板端子間には0V以上Vcc0-Vss0以下の電位しか印加されないのでオフとオンの判別が可能な程度にチャネル抵抗は変化するが十分な不揮発記憶書き込みを行うほどではない。V selectがH、即ち/V selectがLに変わると、回路Aでは大電圧のVcc3とVss3が選択され、これが前段回路に印加される。V selectがHになる直前のVnの論理がHならば、n-Tr2には不揮発オン状態の書込が行われ、p-Tr2には不揮発オフ状態の書込が行われる。

(もっと読む)

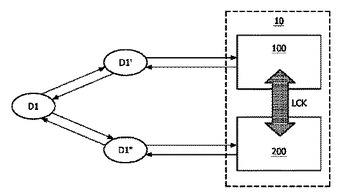

安全な不揮発性メモリ装置およびその内部データを保護する方法

本発明は、不揮発性メモリ装置に関し、この不揮発性メモリ装置は、格納すべき外部データ(D1)を不揮発性メモリ装置に供給する入力と、第1不揮発性メモリブロック(100)および第2不揮発性メモリブロック(200)と、を備え、第1不揮発性メモリブロック(100)および第2不揮発性メモリブロック(200)を、単独のチップ(10)上に設け、第1不揮発性メモリブロック(100)および第2不揮発性メモリブロック(200)は異なるタイプの構成とし、これにより第1不揮発性メモリブロック(100)および第2不揮発性メモリブロック(200)の双方に分散して(D1′、D1″)格納した外部データ(D1)から、データを取得するためには、第1不揮発性メモリブロックおよび第2不揮発性メモリブロックは互換性のない外部攻撃技術を必要とする。本発明は、さらに不揮発性メモリ装置内のデータを保護する方法に関する。  (もっと読む)

(もっと読む)

不揮発性記憶装置及びその動作方法

【課題】不揮発性記憶装置及びその動作方法を提供する。

【解決手段】本発明の装置は、n番目のビットラインに連結された第1トランジスターと、n+1番目のビットラインに連結された第2トランジスターとを含む。前記第1トランジスター及び前記第2トランジスターは、n番目のビットラインとn+1番目のビットラインとの間に直列に連結される。記憶セルのソース領域及びドレーン領域の構造が同一または類似の2トランジスター1ビット単位セルを有する不揮発性記憶装置を形成できる。また、2トランジスター2ビット単位セルを有することができるために記憶容量が2倍に増加できる。

(もっと読む)

不揮発性半導体記憶装置、不揮発性半導体記憶装置の状態決定方法および半導体集積回路装置

【課題】読み出しマージンを大きくとることができ、且つ、ワード線,ビット線の制御をVccレベルで行うことができる書き換え可能な不揮発性メモリセルを提供する。

【解決手段】記憶トランジスタ(nMOSトランジスタ)をサイドスペーサに電荷を注入することによりしきい値を制御可能なトランジスタで構成したインバータをクロス接続してフリップフロップを構成する。一方の記憶トランジスタに書き込みを行うときは、ソース線を介して記憶トランジスタのソースに高電圧を供給するとともに、反対側のインバータの負荷トランジスタを介して記憶トランジスタのゲートに高電圧を供給する。この書き込みを消去するときは、ソース線を介して記憶トランジスタのソースに高電圧を供給する。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】半導体基板の内部にリセスされてそれぞれ形成された複数の第1制御ゲート電極と、複数の第1制御ゲート電極の隣接した一対の間にそれぞれ配置され、複数の第1制御ゲート電極の上端に位置するように、半導体基板上にそれぞれ形成された複数の第2制御ゲート電極と、半導体基板と複数の第1制御ゲート電極との間にそれぞれ介在された複数の第1ストレージノード膜と、半導体基板と複数の第2制御ゲート電極との間にそれぞれ介在された複数の第2ストレージノード膜と、を備えることを特徴とする不揮発性メモリ素子である。

(もっと読む)

21 - 40 / 64

[ Back to top ]