Fターム[5F101BD12]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | メモリセル(センサ) (3,677) | MOSトランジスタ (3,641) | チャンネル領域 (360)

Fターム[5F101BD12]の下位に属するFターム

Fターム[5F101BD12]に分類される特許

21 - 40 / 111

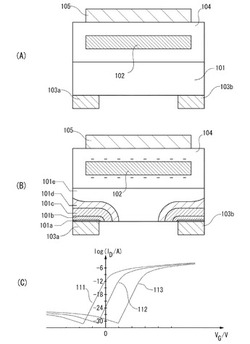

電界効果トランジスタおよび半導体装置の作製方法

【課題】導体半導体接合を用いた電界効果トランジスタのゼロ電流を低減せしめる構造を提供する。

【解決手段】半導体層101とゲート105の間に、絶縁物104により周囲を覆われた導体もしくは半導体よりなり、半導体層101を横切るように形成されたフローティング電極102を形成し、これを帯電させることにより、ソース電極103aやドレイン電極103bからのキャリアの流入を防止する。このため半導体層101中のキャリア濃度を十分に低く維持でき、よって、ゼロ電流を低減できる。

(もっと読む)

半導体装置

【課題】メモリセルの保持データが多値化された場合であっても正確なデータを保持することが可能なメモリセルを有する半導体装置を供給すること。

【解決手段】半導体装置に、酸化物半導体によってチャネル領域が形成されるトランジスタのソース及びドレインの一方が電気的に接続されたノードにおいてデータの保持を行うメモリセルを設ける。なお、当該トランジスタのオフ電流(リーク電流)の値は、極めて低い。そのため、当該ノードの電位を所望の値に設定後、当該トランジスタをオフ状態とすることで当該電位を一定又はほぼ一定に維持することが可能である。これにより、当該メモリセルにおいて、正確なデータの保持が可能となる。

(もっと読む)

記憶装置、半導体装置

【課題】長い期間においてデータの保持が可能な記憶装置を提供する。

【解決手段】記憶素子と、上記記憶素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタとを有する。上記トランジスタは、通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられており、また、活性層に酸化物半導体を含むためにオフ電流が極めて低い。上記記憶装置では、絶縁膜に囲まれたフローティングゲートに高電圧で電荷を注入するのではなく、オフ電流の極めて低いトランジスタを介して記憶素子の電荷量を制御することで、データの記憶を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト孔に埋め込まれる金属プラグの材料が層間絶縁膜に染み出すのを防止できる半導体装置を提供する。

【解決手段】隣り合う2つのメモリセル1のサイドウォール間の不純物拡散領域に電気的接続されるコンタクトプラグ40が、層間絶縁膜18を貫通して設けられている。コンタクト孔41の側壁は、層間絶縁膜18より緻密なシール膜42で覆われている。コンタクトプラグ40は、シール膜42の表面およびコンタクト孔41の底面部を覆うように形成されたバリアメタル膜43と、バリアメタル膜43に包囲された状態でコンタクト孔41内に埋め込まれた金属プラグ44とを含む。

(もっと読む)

半導体装置、及び半導体装置の駆動方法

【課題】データの書込みにおいて、電源電位を増やすことなく電圧を低減することで低消費電力化が実現された半導体装置を提供する。さらにデータの書込みにおいて、電源電位を増やすことなく選択トランジスタにおけるしきい値落ちの問題が抑制された半導体装置を提供する。

【解決手段】nチャネル型の選択トランジスタのゲートに電気的に接続するワード線に直列にダイオード電気的に接続されたトランジスタを電気的に接続し、さらに当該選択トランジスタのソース又はドレインの一方に電気的に接続するビット線と、ワード線との間に容量素子を設ける、またはビット線とワード線との線間容量を利用する。さらに書込みにおいて、ワード選択のタイミングをビット選択のタイミングよりも早くする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】メモリセルアレイを構成する複数のメモリセルが、複数行ごとに複数のブロックに分割され、共通ビット線は、各ブロックにおいて、選択トランジスタを介して分割ビット線と電気的に接続されており、メモリセルの一は、第1のチャネル形成領域を含む第1のトランジスタと、第2のチャネル形成領域を含む第2のトランジスタと、容量素子と、を有し、ソース線は、第1のソース電極と接続され、分割ビット線は、第1のドレイン電極および第2のソース電極と接続され、ワード線は、容量素子の電極の一方と接続され、信号線は、第2のゲート電極と接続され、第1のゲート電極と、第2のドレイン電極と、容量素子の電極の他方とが接続される半導体装置を提供する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、第1の信号線と、第2の信号線と、ワード線と、ソース線とビット線との間に、並列に接続されたメモリセルと、ソース線及びビット線と電気的に接続された第1の駆動回路と、第1の信号線と電気的に接続された第2の駆動回路と、第2の信号線と電気的に接続された第3の駆動回路と、ワード線と電気的に接続された第4の駆動回路と、を有し、メモリセルは、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、容量素子と、を有し、第2のトランジスタは、酸化物半導体材料を含んで構成される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタ160と、第2のトランジスタ162と、第1のトランジスタ160のソース領域またはドレイン領域120と、第2のトランジスタ162のチャネル形成領域144との間に設けられた絶縁層128と、を含むメモリセルを有し、第1のトランジスタ160と、第2のトランジスタ162とは、少なくとも一部が重畳して設けられる半導体装置である。また、絶縁層128と第2のトランジスタのゲート絶縁層146は、式((ta/tb)×(εrb/εra)<0.1)を満たす。(但し、式中、taはゲート絶縁層146の膜厚を示し、tbは絶縁層128の膜厚を示し、εraはゲート絶縁層146の誘電率を示し、εrbは絶縁層128の誘電率を示す。)

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を低減し、特性ばらつきが抑制された多結晶半導体層をチャネル領域とする半導体装置の製造方法を提供する。

【解決手段】半導体基板の上に絶縁体層を形成する工程と、絶縁体層上に狭窄部を有する非晶質または多結晶質の半導体層を形成する工程と、半導体層上に半導体層よりも熱膨張係数の大きい絶縁体層を形成する工程と、熱処理を行う工程と、絶縁体層を除去する工程と、狭窄部の側面にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、半導体層中にソース・ドレイン領域を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜に酸素ドープ処理を行って、第2の絶縁膜中に酸素原子を供給し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体メモリ装置

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体メモリ装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に、書き込みトランジスタのソースおよび読み出しトランジスタのソースをビット線に、読み出しトランジスタのドレインを読み出しワード線に接続する。ここで、書き込みトランジスタと読み出しトランジスタの導電型を異なるものとする。集積度を高めるために、バイアス線を他行の読み出しワード線で代用したり、記憶セルを直列に接続し、NAND構造とし、読み出しワード線と書き込みワード線を共用してもよい。

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】電磁波又は光が照射されても広義のリーク電流が増大せず、書き込み状態及び消去状態の安定した判別を可能とする。

【解決手段】電磁波シールド性能及び遮光性能を持つ層30及び31のどちらにも半導体層60の領域面積よりも大きい領域面積を持たせ、且つこの層30及び31を、半導体層60の上下を挟み込むように設けることで、電磁波及び光が半導体層60に侵入することを防ぐことができる。この結果、広義のリーク電流が格段に低減され、書き込み状態及び消去状態の判別を安定して行うことができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。また、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、半導体装置の各メモリセルを構成する、酸化物半導体を用いたトランジスタを直列に接続することにより、隣り合うメモリセルにおいて、酸化物半導体を用いたトランジスタのソース電極またはドレイン電極をお互いに接続させることができ、メモリセルの占有面積を低減することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、容量素子は、第2のトランジスタのソース電極またはドレイン電極と、ゲート絶縁層と、第2のトランジスタを覆う絶縁層上に設けられた容量素子用電極を含み、第2のトランジスタのゲート電極と、容量素子用電極とは、絶縁層を介して少なくとも一部が重畳して設けられる半導体装置を提供する。第2のトランジスタのゲート電極と、容量素子用電極とを、異なる層で形成することで、半導体装置の集積度を向上させることができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】電荷蓄積層をもち、電荷のトラップを利用する記憶素子の保持特性を向上させる技術を提供する。

【解決手段】電荷蓄積層(24)の上のメモリゲート(21)と、第1サイドゲート(22)と、第2サイドゲート(23)と、第1サイドゲート(22)側の第1不純物注入領域(31)と、第2サイドゲート(23)側の第2不純物注入領域(32)と、チャネル領域(33、34、35)とを具備する不揮発性半導体記憶装置を構成する。チャネル領域(33、34、35)は、電荷蓄積層(24)の下の第1領域(33)と、第1領域(33)と第1不純物注入領域(31)との間のセレクト側領域(34)と、第1領域(33)と第2不純物注入領域(32)との間のアシスト側領域(35)とを含むことが好ましい。そして、ゲート長方向におけるセレクト側領域(34)の長さ(L1)は、アシスト側領域(35)の長さ(L2)よりも長いものとする。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】成膜中に水素原子を含む不純物と強く結合する物質を成膜室に導入して、成膜室に残留する水素原子を含む不純物と反応せしめ、水素原子を含む安定な物質に変性することで、高純度化された酸化物半導体層を形成する。水素原子を含む安定な物質は酸化物半導体層の金属原子に水素原子を与えることなく排気されるため、水素原子等が酸化物半導体層に取り込まれる現象を防止できる。水素原子を含む不純物と強く結合する物質としては、例えばハロゲン元素を含む物質が好ましい。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】チャネル抵抗が低い半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、基板10と、基板10上にそれぞれ交互に積層された複数の導電層WLと複数の絶縁層25とを有する積層体と、積層体を貫通して形成されたメモリホールMHの側壁に設けられた電荷蓄積膜32を含むメモリ膜30と、メモリホールMH内におけるメモリ膜30の内側に設けられたSiGe膜51と、を備えた。

(もっと読む)

半導体装置の製造方法

【課題】良質な特性を有する半導体装置の製造方法を提供する。

【解決手段】制御ゲート電極202の表面に絶縁膜203を形成する工程と、絶縁膜203の表面に電荷蓄積層204を形成する工程と、電荷蓄積層204の表面にトンネル絶縁膜205を形成する工程と、トンネル絶縁膜205の表面にシリコン層206を形成する工程と、シリコン層206を形成した後、熱処理を行ってトンネル絶縁膜205及びシリコン層206の境界面近傍に存在する酸素とシリコンとを反応させる工程と、を備える。

(もっと読む)

NAND型不揮発性半導体記憶装置

【課題】セル間干渉効果によるしきい値ばらつきが抑制されたNAND型不揮発性半導体記憶装置を提供する。

【解決手段】列方向及び行方向にマトリクス状に配置される複数のメモリセルMTと、メモリセルに書込みを行う書込み回路8と、を具備し、メモリセルは、列方向において直列に接続され、行方向において共通のワード線に接続され、第1のメモリセルと、列方向において第1のメモリセルよりも寸法が小さい第2のメモリセルとを含み、書込み回路は、同一列に配置されたメモリセルのうち、所定の第1のメモリセルに書込みを行った後、別の第1のメモリセルに書込みを行い、所定の第1のメモリセルへの書込み及び別の第1のメモリセルへの書込みを行った後に、第2のメモリセルに書込みを行う。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを各々含む複数のメモリセルをマトリクス状に配置し、メモリセルの一と他のメモリセルとを接続する配線(ビット線とも呼ぶ)と、第1のトランジスタにおけるソース電極またはドレイン電極と、が、第2のトランジスタにおけるソース電極またはドレイン電極を介して電気的に接続した構成とした半導体装置を提供する。これにより、第1のトランジスタにおけるソース電極またはドレイン電極と、第2のトランジスタにおけるソース電極またはドレイン電極と、を異なる配線に接続する場合と比較して配線の数を削減することができるため、半導体装置の集積度を向上させることができる。

(もっと読む)

21 - 40 / 111

[ Back to top ]