Fターム[5F101BD14]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | メモリセル(センサ) (3,677) | MOSトランジスタ (3,641) | チャンネル領域 (360) | チャンネルドープ (111)

Fターム[5F101BD14]の下位に属するFターム

部分的チャンネルドープ (56)

Fターム[5F101BD14]に分類される特許

1 - 20 / 55

半導体装置の製造方法

【課題】同一セル内に複数設けられたビットへの個々への書き込み動作が他ビットへの書き込み量に依存することなく正常に行われ、さらには、書き込み・読み出し特性を損なうことなくSONOS構造セルのいっそうの微細化を可能とする半導体装置およびその製造方法を提供する。

【解決手段】本発明による半導体装置は、一対の第1拡散領域を有する基板と、該基板上に形成された酸化膜および該酸化膜上に形成された電荷蓄積層とを有するゲート部とを有し、前記電荷蓄積層は当該電荷蓄積層中に離隔して位置する複数のビット領域を有する電気的絶縁膜である。また、酸化膜は、ビット領域に対応する部分がトンネル酸化膜として作用する膜厚の薄膜部およびビット領域間に位置する部分がトンネル効果による電荷輸送を抑制する膜厚の厚膜部を有している。

(もっと読む)

固集積フラッシュメモリーセルストリング、セル素子、及びこの製造方法

【課題】優れた縮小化特性を有し、閾値電圧の散布を減らすことができるフラッシュメモリーセルストリング及びこの製造方法を提供する。

【解決手段】本発明は、フラッシュメモリーセルストリング及びこの製造方法に関する。前記フラッシュメモリーセルストリングは、多数のセル素子及び前記セル素子の端部に連結されるスイッチング素子を含む。前記セル素子は、半導体基板と、半導体基板に順次に積層される透過絶縁膜と、電荷貯蔵ノードと、コントロール絶縁膜と、制御電極とを備え、ソース/ドレーンが形成されないことを特徴とする。前記スイッチング素子は、セル素子に連結される側にソースまたはドレーンを含まないし、セル素子に連結されない側にソースまたはドレーンを含むが制御電極と重なり、又はまたは重ならないことを特徴とする。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリを提供する。

【解決手段】ビット線と、ソース線と、複数の不揮発性メモリが直列に接続されたNAND型セルと、選択トランジスタと、を有し、不揮発性メモリは、第1の絶縁膜を介した半導体上の電荷蓄積層と、第2の絶縁膜を介した電荷蓄積層上の制御ゲートと、を有し、NAND型セルの一方の端子は、選択トランジスタを介して、ビット線に接続され、NAND型セルの他方の端子は、ソース線に接続されたNAND型不揮発性メモリであって、第1の絶縁膜は、半導体に酸素雰囲気で高密度プラズマ処理を行った後、窒素雰囲気で高密度プラズマ処理を行うことで形成されるNAND型不揮発性メモリ。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

半導体メモリ装置

【課題】短チャネルでも動作するフローティングゲートを有する半導体メモリ装置を提供する。

【解決手段】フローティングゲート104に窒化インジウム、窒化亜鉛等の仕事関数が5.5電子ボルト以上の高仕事関数化合物半導体を用いる。このことにより、基板101とフローティングゲート104の間のフローティングゲート絶縁膜103のポテンシャル障壁が従来のものより高くなり、フローティングゲート絶縁膜103を薄くしても、トンネル効果による電荷の漏洩を低減できる。フローティングゲート絶縁膜103をより薄くできるのでチャネルをより短くできる。

(もっと読む)

半導体記憶装置の製造方法、及び半導体記憶装置

【課題】1つの実施形態は、例えば、トンネル電流を容易に増加できる半導体記憶装置の製造方法、及び半導体記憶装置を提供することを目的とする。

【解決手段】1つの実施形態によれば、半導体記憶装置の製造方法が提供される。半導体記憶装置の製造方法では、Ge、Sn、C、及びNのいずれかの不純物を半導体基板の表面に導入する。半導体記憶装置の製造方法では、前記不純物が導入された前記半導体基板の表面にトンネル絶縁膜が形成されるように、前記半導体基板を熱酸化する。半導体記憶装置の製造方法では、前記トンネル絶縁膜上に電荷蓄積層を有するゲートを形成する。半導体記憶装置の製造方法では、前記ゲートと自己整合的に前記半導体基板内に不純物拡散領域を形成する。

(もっと読む)

半導体記憶装置

【課題】チャネル領域にソース領域及びドレイン領域を形成せずに、信頼性が高い動作が可能な半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、第1の方向に延びる同一導電形のチャネル領域と、チャネル領域上に設けられた第1の絶縁膜と、第1の絶縁膜上に設けられた複数の浮遊ゲートと、浮遊ゲートの上に設けられた第2の絶縁膜と、第2の絶縁膜の上に設けられた制御ゲートとを備えている。複数の浮遊ゲートは第1の方向及びこれに交差する第2の方向に分断されている。制御ゲートは第1の方向に対して交差する第2の方向に延びている。浮遊ゲートのフリンジ電界によって、第1の方向で隣り合う浮遊ゲート間の下のチャネル領域の表面に反転層が形成される。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】従来の半導体記憶装置では、十分に半導体チップの面積を削減することができない問題があった。

【解決手段】本発明の半導体記憶装置は、半導体基板の平坦部に形成されたドレイン領域13と、半導体基板に形成された凸部の上端部に形成されたソース領域10と、ドレイン領域13の一部と重なる領域であって、かつ、平坦部の上層に形成されるコントロールゲート12と、コントロールゲート12と隣り合った領域であって、平坦部、凸部の壁面及びソース領域10の一部を覆う領域に形成されるフローティングゲート11と、を有する。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

半導体記憶装置

【課題】微細化が進んだ場合であってもトランジスタのカットオフ特性を改善しつつ、選択トランジスタのカットオフ特性のバラツキ及びジャンクションリークを抑制する。

【解決手段】半導体基板100上に形成されるp型ウェル2には、ビット線BLの長手方向に沿って形成されたトレンチ3に素子分離絶縁膜4が埋め込まれている。素子分離絶縁膜4によりp型ウェル2が分離され、メモリトランジスタが形成される素子形成領域2Aが形成される。ドレインコンタクト拡散領域15’の位置における素子分離絶縁膜4の高さは、メモリトランジスタMCの位置における素子分離絶縁膜4の高さよりも高くされている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリセルを有する半導体装置において、駆動力の低下を抑えて、信頼度を向上させることのできる技術を提供する。

【解決手段】メモリセルMC1をp型の導電性を示す導電膜からなる選択ゲート電極CGを有する選択用pMIS(Qpc)とp型の導電性を示す導電膜からなるメモリゲート電極MGを有するメモリ用pMIS(Qpm)とから構成し、書込み時には半導体基板1側からホットエレクトロンを電荷蓄積層CSLへ注入し、消去時にはメモリゲート電極MGからホットホールを電荷蓄積層CSLへ注入する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 メモリセルにおけるショートチャネル効果の抑制と誤書き込みの防止の両方を実現し、不揮発性半導体記憶装置の高性能・低コスト化をはかる。

【解決手段】 半導体基板101上に複数の不揮発性メモリセルを配置して構成される不揮発性半導体記憶装置であって、メモリセルは、基板101の表面部に離間して設けられたソース・ドレイン領域120と、ソース・ドレイン領域120の直下の基板101内に設けられ、基板101よりも誘電率が低い埋め込み絶縁膜151と、ソース・ドレイン領域120の間に形成されるチャネル領域上に設けられた第1ゲート絶縁膜102と、第1ゲート絶縁膜102上に設けられた電荷蓄積層103と、電荷蓄積層103上に設けられた第2ゲート絶縁膜104と、第2ゲート絶縁膜104上に設けられた制御ゲート電極105とを備えた。

(もっと読む)

半導体装置とその製造方法

【課題】 トランジスタと抵抗等複数種類の半導体素子を簡略化した工程で作成する。

【解決手段】 半導体装置の製造方法は、半導体基板にアスペクト比1以上の素子分離領域を形成し、ゲート絶縁膜を形成し、シリコン層を堆積し、パターニングしてゲート電極と抵抗素子を形成し、ゲート電極の側壁サイドウォールを形成し、第1の活性領域に高濃度の燐を、第2の活性領域及び抵抗素子に高濃度のp型不純物を、イオン注入し、500℃以下の温度でサリサイドブロック層を形成し、サリサイドブロック層を覆うように金属層を堆積し、選択的に金属シリサイド層を形成する。厚いゲート絶縁膜と著しく薄いゲート絶縁膜を形成し、サイドウォール形成前、厚いゲート絶縁膜は貫通しない第1導電型のイオン注入と、厚いゲート絶縁膜も貫通する逆導電型の斜めイオン注入を行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】高性能な書きこみ消去特性を有する不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板のp型ウエル2上にゲート絶縁膜6を介して選択ゲート18が形成され、p型ウエル2上に酸化シリコン膜15a、窒化シリコン膜15bおよび酸化シリコン膜15cからなる積層膜15を介してメモリゲート17が形成される。メモリゲート17は、積層膜15を介して選択ゲート18に隣接する。p型ウエル2の選択ゲート18およびメモリゲート17の両側の領域には、ソース、ドレインとしてのn型の不純物拡散層20,21が形成されている。不純物拡散層20,21の間に位置するチャネル領域のうち、選択ゲート18により制御され得る領域51とメモリゲート17により制御され得る領域52とにおける不純物の電荷密度が異なる。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の特性を向上させる。

【解決手段】電荷蓄積膜MI1に対して電荷を授受することで記憶動作を行う不揮発性メモリセルNVM1を有する半導体装置であって、不揮発性メモリセルNVM1は、シリコン基板1の主面s1に形成されたpウェルpw1と、主面s1上に電荷蓄積膜MI1を隔てて形成されたメモリゲート電極MG1とを有し、更に、シリコン基板1の主面s1のうち、電荷蓄積膜MI1下に位置するメモリチャネル領域ch1aにフッ素を含んでいる。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】ドレインディスターブ特性が満足でき、電子注入状態における電流の低下が抑制される半導体記憶装置の提供。

【解決手段】溝24を有するP型半導体基板2と、P型半導体基板2の溝24を有しない部分の表面に形成されたソース側N−拡散層44S、N+拡散層42S、ドレイン側N−拡散層44D、N+拡散層42Dと、溝24の側壁部、底部、N−拡散層44S、44D、N+拡散層42S、42Dの表面を覆うゲート酸化膜12と、溝24を埋め込むようゲート酸化膜12の表面に形成され、溝24が連続する方向に格子状に形成されたゲート電極14と、溝24の側壁部の表面のうち、少なくともゲート酸化膜12を介してN−拡散層44S、44Dと対向する領域に形成され、ゲート電極14との間に酸化膜12を介してスペーサ状に形成された窒化膜8と、ゲート電極14と直接接するように形成されたゲート裏打ち配線10と、を備える半導体記憶装置。

(もっと読む)

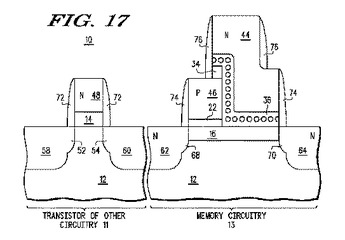

スプリット・ゲート・メモリ・デバイスの形成方法および装置

スプリット・ゲート・メモリ・デバイス(10)は、第1の仕事関数を有する選択ゲート(46)を基板(12)の第1の部分の上に有する。第2の仕事関数を有する制御ゲート(44)は、第1の部分に隣接する基板の第2の部分の上にある。スプリット・ゲート・メモリ・デバイス(10)の多数キャリアが電子であるとき、第1の仕事関数は第2の仕事関数よりも大きい。スプリット・ゲート・メモリ・デバイス(10)の多数キャリアがホールであるとき、第1の仕事関数は第2の仕事関数よりも小さい。基板(12)内の第1の電流電極(62)および第2の電流電極(64)は、制御ゲートおよび選択ゲートの下にあるチャネルによって分離される。制御ゲートおよび選択ゲートの異なる仕事関数は、デバイス性能を最適化するために各ゲートに対して異なる閾値電圧をもたらす。nチャネルデバイスでは、選択ゲートはp導電型であり、制御ゲートはn導電型である。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、製造コストの上昇を抑えつつ、歩留まりを向上させること。

【解決手段】シリコン(半導体)基板1と、シリコン基板1に形成される素子分離絶縁膜6と、シリコン基板1の上、及び素子分離絶縁膜6の上に形成され、素子分離絶縁膜6の上に側面13eを有する導電パターン13aと、素子分離絶縁膜6の上、導電パターン13aの上、及び導電パターン13aの側面13eに形成される絶縁膜16とを有し、導電パターン13aの側面13eにノッチ13wが形成された半導体装置による。

(もっと読む)

1 - 20 / 55

[ Back to top ]