Fターム[5F101BD12]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | メモリセル(センサ) (3,677) | MOSトランジスタ (3,641) | チャンネル領域 (360)

Fターム[5F101BD12]の下位に属するFターム

Fターム[5F101BD12]に分類される特許

41 - 60 / 111

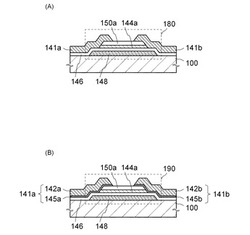

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

半導体装置

【課題】不揮発性記憶装置と揮発性記憶装置の双方のメリットを享受する記憶装置を提供する。

【解決手段】基板または基板上に設けられた第1のトランジスタと、第1のトランジスタよりも上に設けられた第2のトランジスタを有する半導体装置において、第1のトランジスタと第2のトランジスタの少なくとも一部を重畳させ、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極を電気的に接続させる。第1のトランジスタとしてはシリコン単結晶により設けられたものが好ましく、第2のトランジスタとしてはオフ電流が極端に小さい酸化物半導体により設けられたものが好ましい。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、第1の信号線と、第2の信号線と、ワード線と、ソース線とビット線との間に、接続されたメモリセルと、ビット線と電気的に接続された第1の駆動回路と、第1の信号線と電気的に接続された第2の駆動回路と、第2の信号線と電気的に接続された第3の駆動回路と、ワード線及びソース線と電気的に接続された第4の駆動回路と、を有し、第1のトランジスタは、酸化物半導体以外の半導体材料を用いて構成され、第2のトランジスタは、酸化物半導体材料を含んで構成される。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のソース電極および第1のドレイン電極と、第1のソース電極および第1のドレイン電極と電気的に接続され、酸化物半導体材料が用いられている第1のチャネル形成領域と、第1のチャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、を有する第1のトランジスタと、容量素子と、を有し、第1のトランジスタの第1のソース電極または第1のドレイン電極の一方と、容量素子の電極の一方とは、電気的に接続された半導体装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的とする。

【解決手段】チャネル形成領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極及び第1のドレイン電極と、を有する第1のトランジスタと、酸化物半導体層と、第2のソース電極及び第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、第2のソース電極または第2のドレイン電極の一方と、第2のゲート絶縁層と、第2のゲート絶縁層上に第2のソース電極または第2のドレイン電極の一方と重畳するように設けられた電極と、を有する容量素子と、を有し、第1のゲート電極と、第2のソース電極又は第2のドレイン電極の一方とは電気的に接続されている。

(もっと読む)

不揮発性メモリ素子を有する装置

【課題】新たな不揮発性メモリ素子を有する装置を提供する。

【解決手段】チャネル形成領域を構成する半導体材料として酸化物半導体を用いた不揮発性メモリ素子を有する装置を提供するものであり、制御ゲートと、第1の絶縁膜を介して制御ゲートと重ねて設けられた電荷蓄積層と、酸化物半導体材料を用いて形成され、第2の絶縁膜を介して電荷蓄積層と重ねて設けられたチャネル形成領域を有する酸化物半導体層と、によって不揮発性メモリ素子が構成されるものである。

(もっと読む)

不揮発性半導体記憶装置

【課題】NAND型フラッシュメモリにおいて、微細化にともなうソース領域およびドレイン領域の導通を回避できるようにする。

【解決手段】たとえば、p型ウェル12の少なくとも表面領域のボロン濃度が1E15cm-3以下となるように設定する。また、そのp型ウェル12の表面部に、ソース領域およびドレイン領域を有さず、トンネル酸化膜21を介して設けられた浮遊ゲートFGと、この浮遊ゲートFG上に絶縁膜22を介して設けられたワード線WLとなる制御ゲートCGとを有するゲート電極を備える、複数のフラッシュメモリセルMCnを設けてなる構成とされている。

(もっと読む)

ナノ線メモリ

【課題】単純な構造のナノ点を有するメモリを利用してマルチレベルを保存することができるメモリ素子を提供する。

【解決手段】ソース210及びソース210と対応するドレイン220と、ソース210とドレイン220との間を連結するように形成されているナノチャンネル230とを含み、ナノチャンネル230は、ソース210及びドレイン220の電圧によってソース210とドレイン220との間を電気的に連結するナノ線と、ナノ線上に吸着されて形成され、電荷を補集する複数のポテンシャルを有するナノ点とを含む。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの特性が良好な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置1において、シリコン基板11上にトンネル絶縁層12、電荷蓄積層13及び電荷ブロック層14をこの順に形成し、電荷ブロック層14上に複数の制御ゲート電極15を設ける。電荷ブロック層14は、比誘電率がシリコン窒化物の比誘電率よりも高い金属酸化物により形成し、制御ゲート電極15は、金属、金属シリサイド又はドーパントを含有するシリコンにより形成する。又は、電荷ブロック層14は、シリコン酸化物又はシリコン酸窒化物により形成し、制御ゲート電極15は、金属又は金属シリサイドにより形成する。そして、電荷ブロック層14と各制御ゲート電極15との間に、シリコン窒化物からなるキャップ層20を形成する。

(もっと読む)

メモリ装置

【課題】電荷トラップ層からのトンネル効果による電子の漏れを抑制することができ、データの保持時間の長期化を図ることができるとともに、トンネル酸化膜の薄膜化を可能として、データの書き込み速度の向上を図ることのできるメモリ装置を提供する。

【解決手段】シリコン層と、シリコン層と接して設けられたゲート絶縁膜と、ゲート絶縁膜に接して設けられたゲート電極とを有するメモリ素子を具備したメモリ装置において、ゲート絶縁膜は、トンネル酸化膜、電荷トラップ膜、ブロック酸化膜の3層を積層して構成されたゲート絶縁膜であり、ゲート電極は、ブロック酸化膜上に形成されたゲート電極であって、シリコン層が、当該シリコン層の厚さが2nm以上14nm以下となるように、ゲート絶縁膜によって挟まれた部分、又はゲート絶縁膜と他の絶縁膜とによって挟まれた部分を有する。

(もっと読む)

半導体素子とその製造及び動作方法

【課題】 半導体素子とその製造及び動作方法を提供する。

【解決手段】 相異なるナノ構造体を含む半導体素子である。例えば、半導体素子は、ナノワイヤーで形成された第1構成要素とナノパーティクルで形成された第2構成要素とを含む。ここで、ナノワイヤーは、双極性の炭素ナノチューブでありうる。第1構成要素は、チャンネル層であり、第2構成要素は、電荷トラップ層であるが、この場合、前記半導体素子は、トランジスタやメモリ素子でありうる。

(もっと読む)

強誘電体ゲート電界効果トランジスタ、それを用いたメモリ素子及び強誘電体ゲート電界効果トランジスタの製造方法

【課題】ゲート構造にIFI構造が含まれるMFS型メモリの強誘電体ゲート電界効果トランジスタにおいて、強誘電体膜の強誘電体特性及びトランジスタの電気特性の劣化を防止する。

【解決手段】Si基板1と、Si基板1上に少なくともHfSiON膜2、強誘電体膜3及びHfSiON膜4が、この順で積層されたゲート構造を有しており、HfSiON膜2及びHfSiON膜4は、強誘電体膜3を加熱処理によって形成する焼成温度で非晶質である。

(もっと読む)

半導体記憶装置

【課題】異なる階層に位置するメモリセル間の特性のばらつきを抑制できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置1は、半導体基板11と、半導体基板11上に設けられ、複数の絶縁層14と複数の導電層WL1〜WL4とが交互に積層された積層体と、積層体を貫通して形成された貫通ホールの内部に設けられ、絶縁層14と導電層WL1〜WL4との積層方向に延びる半導体層SPと、導電層WL1〜WL4と半導体層SPとの間に設けられた電荷蓄積層26と、を備え、半導体層SPにおける下部は上部よりも細く、導電層WL1〜WL4における少なくとも最下層は最上層よりも薄い。

(もっと読む)

ナノ構造メモリデバイス

本発明は、電流輸送チャネルを形成する少なくとも1つの半導体ナノワイヤ(3)と、前記ナノワイヤ(3)の少なくとも一部の周りに配置された1つ以上のシェル層(4)と、前記1つ以上のシェル層(4)に埋め込まれたナノサイズの電荷捕獲中心(10)と、前記1つ以上のシェル層(4)の少なくとも一部のそれぞれの周りに配置された1つ以上のゲート電極(14)とを備えるナノ構造メモリデバイスを提供する。好ましくは、前記1つ以上のシェル層(4)は、ワイドバンドギャップ材料又は絶縁体で構成される。前記電荷捕獲中心(10)は、前記1つ以上のゲート電極を用いることによってチャージされてもよく/書き込まれてもよく、1つ以上の前記電荷捕獲中心(10)に蓄積された電荷量の変化は、前記ナノワイヤ(3)の導電率を変更する。 (もっと読む)

半導体装置の製造方法及び半導体装置

【課題】一度の酸化処理でONO膜の上側酸化膜を下側酸化膜よりも厚く形成することができるミラービットの半導体装置の製造方法を提供する。

【解決手段】基板10上に第1酸化膜11、この第1酸化膜11よりも膜厚が薄い窒化膜12、第1酸化膜11よりも膜厚が薄い第2酸化膜13、及びゲート電極14を積層する工程と、第1酸化膜11の端部及び第2酸化膜13の端部を除去して窒化膜12を一部露出する工程と、第1酸化膜11が除去された基板10上に第3酸化膜15を形成すると同時に、窒化膜12の露出部分を酸化して第4酸化膜16を形成し且つゲート電極14の周囲に第5酸化膜17を形成して、第4酸化膜16と第5酸化膜17とが一体化した、第3酸化膜15よりも厚い酸化膜を形成する工程と、第3酸化膜15と第4酸化膜16との間に電荷蓄積層18aを形成する工程と、をこの順に行う。

(もっと読む)

フラッシュメモリ及びその製造方法

【課題】30nm以下の微細化に適応できるフラッシュメモリ及びその製造方法を提供する。

【解決手段】基板101に接続された上部にスペーサ絶縁膜116を有するフィン構造のビットラインから形成されたメモリセル部の最小加工寸法をFとするとき、独立に書き込み/消去可能なビットライン2本が対になって4F周期に配置されてメモリセル部が形成され、一対のフィンの上部を覆うように記憶絶縁膜が形成されている。

(もっと読む)

半導体素子及び半導体装置

【課題】短チャネル効果が抑制され高い電流駆動力を有する細線半導体素子を実現する。

【解決手段】半導体基板上に設けられた絶縁領域と、絶縁領域上に略平行に整列して設けられた第一導電型の複数の線状半導体層と、各線状半導体層に離間して設けられた第二導電型のソース・ドレイン領域と、ソース・ドレイン領域の間に設けられたチャネル領域と、各線状半導体層の上面と側面上に設けられた第一の絶縁膜と、第一の絶縁膜上に設けられ、複数の線状半導体層と交差するように連続的に設けられたゲート電極とを有し、線状半導体層を線方向に流れる電流に垂直、且つ基板表面に平行に測ったチャネル領域の長さが、チャネル領域中の不純物濃度で決まる最大空乏層幅の二倍以下であり、複数の線状半導体層の間隔が、線状半導体層の上面とゲート電極との間隔の二倍以下であり、絶縁領域の表面の少なくとも一部に於ける誘電率が、酸化シリコンの誘電率よりも低い。

(もっと読む)

半導体装置およびその製造方法

【課題】配線抵抗の電圧ドロップによるデータの消去特性バラツキを抑えることができる半導体装置を提供する。

【解決手段】メモリセル5それぞれは、素子形成基板1に形成されたトレンチ6と、トレンチ6の側壁に形成された酸化膜7と、トレンチ6の底部に形成されたトンネル酸化膜8と、酸化膜7およびトンネル酸化膜8を介してトレンチ6内に形成され、データが書き込まれるかまたはデータが読み出されるフローティングゲート9と、トンネル酸化膜8においてフローティングゲート9とは反対側に形成され、フローティングゲート9に書き込まれたデータを消去するための裏面電極2とを備えている。データの消去の際には、裏面電極2に電圧を印加することにより、各メモリセル5に記憶されたデータを一括消去する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】SOI上に形成された半導体層上にメモリセルユニット及び選択トランジスタを形成した場合に、選択トランジスタの特性を向上できる半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板11と、前記半導体基板上に設けられ開口を有する絶縁層12と、前記絶縁層上に設けられた半導体層13とを備える支持基板15と、前記半導体層上に設けられ、電流経路が直列接続された複数のメモリセルを備えるメモリセルユニットMUと、前記メモリセルユニットに隣接し、かつ前記開口の上方の前記半導体層上に配置され、前記開口の上方の前記半導体層の上面は前記メモリセルユニットが設けられた前記半導体層よりも中央近傍のみが低いリセス構造17を有し、前記リセス構造上における前記半導体層上に設けられたゲート絶縁膜18と、前記ゲート絶縁膜上に設けられたゲート電極19とを備えた選択トランジスタSTとを具備する。

(もっと読む)

41 - 60 / 111

[ Back to top ]