Fターム[5F101BE07]の内容

不揮発性半導体メモリ (42,765) | 周辺技術 (5,862) | 消去 (2,505) | 電気消去消去回路 (2,403)

Fターム[5F101BE07]に分類される特許

2,001 - 2,020 / 2,403

SONOSメモリ素子の動作方法

【課題】SONOSメモリ素子の動作方法を提供する。

【解決手段】基板に離隔して形成されており、所定の導電性不純物がドーピングされた第1及び第2不純物領域(14、12)と、第1及び第2不純物領域間の基板上に形成されたゲート酸化膜(16)と、ゲート酸化膜上に形成された第1トラップ層(18)と、第1トラップ層上に形成された絶縁膜(20)と、絶縁膜上に形成されたゲート電極(22)と、を備えるSONOSメモリ素子の動作方法において、第1不純物領域(14)及びゲート電極(22)にそれぞれ第1電圧(V1)及びゲート電圧(Vg)を印加し、第2不純物領域(12)に0Vよりも小さな第2電圧(V2)を印加してSONOSメモリ素子にデータを記録する。

(もっと読む)

半導体記憶装置

【課題】 微細化とソース拡散層の低抵抗化が可能な不揮発性半導体記憶装置を提供する。

【解決手段】 基板4に形成されたP型のウェル2上にN型のソース拡散層104およびN型のドレイン拡散層が形成された不揮発性半導体記憶装置であって、各ソース拡散層104をその延伸方向に沿った直線と基板4の法線とを含む平面で切った断面が凹凸形状となっており、凸部の上壁層306および凹部の下壁層307が側壁層308を介して連続することでソース拡散層104をなすとともにこの上下壁層306・307および側壁層308を覆うようにシリサイド204aが形成され、かつ該シリサイド204aを覆うように絶縁層205が形成され、上壁層306上に位置するシリサイド204aと絶縁層205との界面および下壁層307上に位置するシリサイド204aと絶縁膜205との界面の距離dが1000Å以下である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】電荷保持能力の高いフローティングゲート電極を備えた不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体領域の上に設けられ窒素を含むシリコン酸化膜からなるトンネル絶縁膜4と、フローティングゲート電極5とを備えている。トンネル絶縁膜4におけるフローティングゲート電極5との界面領域には、その全面に複数の電荷捕獲サイトが分布しており、フローティングゲート電極への電子注入においては、複数の電荷捕獲サイトのうち局所領域に形成された各電荷捕獲サイトを除く電荷捕獲サイトに、電荷が捕獲されない。

(もっと読む)

半導体装置およびその製造方法

【課題】 パターンの寸法精度が高い半導体装置を提供する。

【解決手段】 半導体装置は、半導体基板50と、半導体基板50の主表面上のpウエル70に形成されたトレンチと、トレンチ内に形成され、埋込み不良箇所41を有する分離領域40と、その一部が分離領域40上に形成され、埋込み不良箇所41上に終端部を有するアシストゲート電極12とを備える。そして、アシストゲート電極12は、埋込み不良箇所41に埋込まれることによって他の部分よりも厚く形成された厚肉部Tを有している。

(もっと読む)

斬新な低電力不揮発性メモリおよびゲートスタック

良好な電荷保持のために、高い電荷ブロッキングバリアおよび深いキャリアトラッピングサイトを維持しながら、直接的なトンネルプログラミングと消去を可能にするNOR又はNANDメモリアーキテクチャにおいて、バンドギャップ技術に基づくゲートスタックを、反転モードおよび通常モードのフローティングノードメモリセルにおける非対称トンネルバリアと一緒に、使用することを促進する不揮発性メモリデバイスおよびアレイが記載されています。低電圧で直接的なトンネリングプログラムと消去の能力は、高いエネルギーキャリアからゲートスタックおよび結晶格子に対する損害を減少させて、書込み疲労を減少させ、デバイス寿命を増進させます。低電圧で直接的なトンネルプログラムと消去の能力は、また、低電圧設計およびさらなるデバイス形状性のスケーリングを介して、サイズ縮小を可能にします。本発明のメモリセルは、また、多数ビット記憶を可能にします。これらの特性は、本発明のメモリデバイスの実施の形態が、システム内のDRAMおよびROM双方に取って代わることができて、ユニバーサルメモリの定義内で動作することを可能にします。 (もっと読む)

磁気抵抗ランダム・アクセス・メモリ(MRAM)を用いた不揮発性メモリ・システム

不揮発性メモリ・システム(230)は、複数の磁気抵抗メモリ・セルを含む磁気抵抗ランダム・アクセス・メモリ(MRAM)(232)と、複数のフローティングゲート・メモリ・セルを含むフローティングゲート不揮発性メモリ(234)と、MRAM(232)及びフローティングゲート不揮発性メモリ(234)に結合された制御器(236)とを含む。制御器(236)は、システム・バス(220)に結合されるよう適合され、且つシステム・バス(220)から開始されたアクセスに応答して、MRAM(232)及びフローティングゲート不揮発性メモリ(234)のうちの選択された1つを制御する。  (もっと読む)

(もっと読む)

消去速度の遅いメモリセルを補正するために、ワードライン変更条件を利用して非揮発性メモリを消去する方法

非揮発性メモリシステムのメモリセルに印加する電圧条件を消去動作中に変更することによって、選択メモリセルの消去動作を、システム内の同時に消去されている他のメモリセルの消去動作と一致させる。変更された条件は、NANDストリング内の容量結合した電圧を補正できる。消去動作についてNANDストリングをバイアスした後に、又、消去電圧パルスの印加を開始した後に、1又は複数の内部メモリセルのワードラインを浮遊させることができる。選択した内部ワードラインを浮遊させることで、結合しているセルのトンネル誘電領域に亘って生じたピーク消去電位が通常レベルから低下する。その結果、これらのセルの消去速度が遅速化して、これよりも遅いストリングの消去エンドメモリセルの消去速度と実質的に一致する。別個のワードラインをそれぞれ異なる時間に浮遊させて、異なるメモリセル消去動作を異なる分量で変化させることができる。  (もっと読む)

(もっと読む)

ビット線構造およびその製造方法

本発明は、ビット線構造およびその製造方法に関する。この方法では、分離トレンチ(T)は、導電性レンチ充填層(5)によって、第2コンタクト部(KS)と第2コンタクト部(KS)に隣接する第1コンタクト部(KD)との少なくとも付近が充填されている。上記導電性レンチ充填層(5)は、埋め込み接触バイパス線を得るために、第2コンタクト部(KS)に隣接する第1不純物領域(D)を相互連結している。  (もっと読む)

(もっと読む)

フローティングゲートメモリのプログラミング方法

【課題】フラッシュEEPROMに生じるセルの過消去の問題を解決する。

【解決手段】本発明の方法によりプログラミング中により低いワード線電圧Vp1を使用することができる。さらに、本発明によりメモリセルアレイ10のフラッシュプログラミングに使用した場合に比較的狭い閾値電圧分布Vtが得られる。またプログラムされるセルのソース11/基板23接合を逆バイアルすることにより圧縮ゲート電流効率が向上する。逆バイアスは、例えば、ソース11にバイアス電圧を印加するかもしくはソース11に直列にダイオード27、抵抗29もしくは他のインピーダンスを接続して行われる。逆バイアスによりフラッシュプログラミング圧縮中にプログラムされるセルもしくはアレイ全体のソース電流ISが制限される。

(もっと読む)

ビット線構造およびその製造方法

本発明は、表面ビット線と埋め込みビット線(5、SL)とを備えたビット線構造に関するものである。この埋め込みビット線は、トレンチ(T)の上部領域に形成されており、第1接続層(11)を介して、その第1不純物領域(S)に接続されている。トレンチ(T)の下部領域では、さらに、第2トレンチ絶縁層(4)によって埋め込みビット線(5、SL)から絶縁された第1トレンチ充填層(3)が、位置している。  (もっと読む)

(もっと読む)

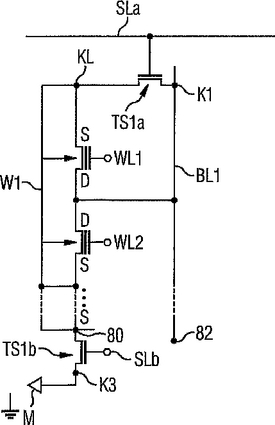

集積されたメモリ回路構造、特にUCPフラッシュメモリ

【課題】チップ面積の低減および電気特性の改善の少なくとも一方を実現できるメモリ回路構造50を提供する。

【解決手段】トランジスタをそれぞれ含む複数のメモリセルをマトリックス状に配置する。上記マトリックスの行における、メモリセルの各トランジスタの各制御電極に各ワード線WL1、WL2を配置する。上記マトリックスの列における、メモリセルの各トランジスタの各端子電極に各ビット線BL1、W1を配置する。スイッチング素子TS1aを、上記列毎に配置する。上記スイッチング素子TS1aは、上記の同一の列に位置する2つの各ビット線BL1、W1同士を電気的に断接できるようになっている。上記スイッチング素子TS1aにより、メモリ回路構造50における、チップ面積を低減および/または電気特性を改善できる。  (もっと読む)

(もっと読む)

マルチビット及びマルチレベル不揮発性メモリ素子、その動作方法及び製造方法

【課題】マルチビット及びマルチレベル不揮発性メモリ素子、その動作方法及び製造方法を提供する。

【解決手段】フィンの両側壁にスペーサ形態にそれぞれ形成された一対のゲート電極と、ゲート電極と半導体基板との間にそれぞれ形成された一対のストレージノードと、を備える不揮発性メモリ素子である。ゲート電極は、相互に離隔されてフィンにそれぞれ形成されたソース及びドレインを共有する。チャンネル領域は、ソース及びドレイン間のフィンの両側壁の表面領域にそれぞれ形成される。

(もっと読む)

半導体装置とその製造方法

接地線抵抗とビット線容量が低いフラッシュメモリ半導体装置を提供する。 半導体装置は、複数の半導体素子を形成した半導体基板構造体上方に形成され、平坦な表面を有する第1絶縁層と、第1絶縁層の全厚さを貫通して形成された複数の柱状導電性プラグと、第1絶縁層の全厚さを貫通して形成され、延在する複数の壁状導電性プラグと、柱状導電性プラグと壁状導電性プラグとを覆って、第1絶縁層上に形成され、平坦な表面を有する第2絶縁層と、第2絶縁層の全厚さを貫通して形成され、柱状導電性プラグの少なくとも1つと接続される第1部分と、第2絶縁層の中間までの深さに形成され、壁状導電性プラグの少なくとも1つと離間しつつ交差する第2部分とをそれぞれ有するデュアルダマシン構造の複数の第1配線と、を有する。  (もっと読む)

(もっと読む)

不揮発性半導体メモリ装置

【課題】浮遊電極と電極間絶縁膜間、または制御電極と電極間絶縁膜の界面層に係り、特性の良好な不揮発性半導体メモリ装置を提供する。

【解決手段】 半導体基板10の主面上にトンネル絶縁膜11を介して選択的に形成された浮遊電極12と、浮遊電極12上に第一の界面層13を介して電極間絶縁膜14を形成し、さらにその上に第二の界面層15を介して制御電極16を形成し、各電極12,16に対応して基板の主面に形成されたソース・ドレイン領域17とを備えた不揮発性半導体メモリ装置であって、浮遊電極12とも電極間絶縁膜14ともことなる第一の材料からなる第一の界面層13と、制御電極16とも電極間絶縁膜14とも異なる第二の材料からなる第二の界面層15の少なくとも一方を有すること特徴とする構造を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】 低消費電流でかつ小チップレイアウト面積の不揮発性半導体記憶装置を提供する。

【解決手段】 不揮発性メモリセル(MC;MC0,MC1)において、メモリセルトランジスタ(MT)と直列に選択トランジスタ(ST)を接続する。この選択トランジスタは、2層ゲート構造とし、各ゲート(G1,G2)の電圧を個々に駆動する。これらの選択トランジスタの積層ゲート電極層間の容量結合を用いて、選択トランジスタのゲート電位を所定の電圧レベルに設定する。選択トランジスタゲート電圧発生部の発生電圧レベルの絶対値を小さくすることができ、消費電流を低減でき、また電圧発生部のレイアウト面積を低減することができる。

(もっと読む)

検知回路

【課題】電源電圧の急激な変化(電源ノイズ)による誤動作を防止できる検知回路を提供すること。

【解決手段】固定電位点と、パワーオン時、固定電位点からの電位差が変化していく可変電位点との電位差が所定の電位差となったことを検知する、半導体基板に形成される検知回路であって、可変電位点の電位にバイアスされる第1の半導体領域に形成され、可変電位点に接続される第1の抵抗体(r3)と、固定電位点の電位にバイアスされる第2の半導体領域に形成され、可変電位点に接続されない第2の抵抗体(r1)とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】 電極層の電気的特性の悪化を抑制できるようにする。

【解決手段】 ゲート電極分離領域GVに形成された第1の多結晶シリコン層5を除去する工程の前に、ゲート電極形成領域GCに形成されたシリコン窒化膜10、WSi膜9、第3の多結晶シリコン層8、ONO膜7、第2の多結晶シリコン層6の側壁を保護するための保護膜14を形成しているため、これらの各層6〜10を保護することができ第1の多結晶シリコン層5をエッチング処理するときの各層6〜10の機能低下を抑制できる。

(もっと読む)

バックバイアスを用いてSOI基板に形成されたフラッシュブロックを消去するためのフラッシュメモリ素子の製造方法、その消去方法及びその構造

【課題】工程が簡単で、再現性が高く、リフラッシュが可能なフラッシュ素子をSOI基板を用いて製作する方法を提供し、フラッシュ素子の大きさを小型に製作するために、SOI基板を用いて製作する方法を提供する。

【解決手段】本発明に係わるSOI基板上に形成されたフラッシュブロックでバックバイアスを用いてフラッシュブロックを消去できるフラッシュメモリ素子の製作方法は、SOI基板上にフラッシュブロックが形成されるステップ及びSOI基板の下面にボディー電極が形成されるステップとを含む。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルの微細化に伴うオフリークを低減させることのできる半導体記憶装置およびその製造方法の提供。

【解決手段】トレンチ部1aを有する基板1と、トレンチ部1aに隣接する基板1上に絶縁膜2を介して配設されたセレクトゲート3と、セレクトゲート3下の基板1表面に設けられた第1のウェル1bと、トレンチ部1aの底部ないし側壁部表面に絶縁膜8aを介して配設されたフローティングゲート6と、フローティングゲート6下のトレンチ部1a底部表面に設けられた第2のウェル1cと、トレンチ部1a底部表面に設けられた第1の拡散領域7aと、フローティングゲート6の上に絶縁膜8を介して配設されたコントロールゲート11と、で一つの単位セルを構成し、セレクトゲート3に対してトレンチ部1aの側壁面ないし底面近傍をチャネルとし、第1のウェル1bの不純物濃度は、第2のウェル1cの不純物濃度以下である。

(もっと読む)

反転ビット線、電荷をトラップする不揮発性メモリ、およびその動作方法

【課題】電荷をトラップするメモリセルを用いた不揮発性メモリであって、反転ビット線に基づくメモリデバイスの実用的な形態および動作方法を提供する。

【解決手段】電界によって引き起こされる反転層を用いて、ソースおよびドレインへの注入の代わりとする、電荷をトラップするメモリデバイス。メモリセルは2ビットを記憶するようになっており、ひとつのビットは電荷トラップ構造体の左側、もうひとつは右側にある。負のゲート電圧のファウラー−ノルトハイム(FN)トンネル効果を用いて、正の閾値電圧の消去状態が引き起こされ、これによって、正の電圧において電荷平衡状態が確立される。低電流ソース側ホット電子注入プログラム法が用いられる。

(もっと読む)

2,001 - 2,020 / 2,403

[ Back to top ]