Fターム[5F102FB10]の内容

接合型電界効果トランジスタ (42,929) | 特殊動作 (121) | その他の特殊動作 (22)

Fターム[5F102FB10]に分類される特許

1 - 20 / 22

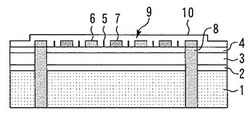

ワイドバンドギャップ半導体デバイス

【課題】製造が容易であり、デバイス特性の変動を抑制できるワイドバンドギャップ半導体デバイスを得る。

【解決手段】SiC基板1上にAlN格子緩和層2、GaNチャネル層3、及びAlGaN電子供給層4が順に設けられている。これらは、1.42eVより広いバンドギャップを持つ半導体材料からなる。AlGaN電子供給層4に、トランジスタを含む活性領域9が設けられている。SiC基板1は、光学的な不純物又は格子欠陥により着色され、可視光領域の光を吸収する。従って、このデバイスは波長360nm〜830nmの可視光領域の光に対して不透明である。

(もっと読む)

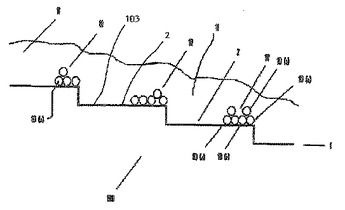

テラヘルツ波素子

【課題】テラヘルツ波を発生又は検出するテラヘルツ波素子において、単色性が良いテラヘルツ波を効率良く出射する。

【解決手段】テラヘルツ波素子は、基板101の上に形成された第1の半導体層102と、第1の半導体層102の上に形成された第2の半導体層104と、第2の半導体層104の上に形成されたゲート電極106と、第2の半導体層104の上にゲート電極106を挟んで対向するように形成されたソース電極107及びドレイン電極108と、第2の半導体層104の上におけるゲート電極106とソース電極107との間及びゲート電極106とドレイン電極108との間に形成され、複数の金属膜109が周期的に配置された周期構造を有する周期金属膜109A,109Bと、ゲート電極106及び複数の金属膜109の上方に配置された第1のミラー111と、基板101の下に形成された第2のミラー112とを備えている。

(もっと読む)

ジチエノベンゾジチオフェン誘導体からなる有機半導体材料前駆体、インク、絶縁部材、電荷輸送性部材、有機電子デバイス

【課題】印刷等の簡便なプロセスで成膜できる溶解性を有し、成膜後は簡単な処理により不溶化し、後工程でのダメージを軽減できると共に、不溶化処理後は良好な半導体特性を示すジチエノベンゾジチオフェン誘導体からなる有機半導体材料前駆体、該前駆体を含有するインク、該インクを用いて作製された絶縁部材、電荷輸送性部材、有機電子デバイスの提供。

【解決手段】下記一般式(I)で表されるジチエノベンゾジチオフェン誘導体からなることを特徴とする有機半導体材料前駆体。

〔上記式中、X及びYは、外部刺激によりXとYが結合してX−Yとして一般式(I)の化合物から脱離する基を表し、R1及びR2はそれぞれ独立に、アルキル基、又はアリール基を表し、R3〜R10はそれぞれ独立に、水素、アルキル基、アルコキシ基、アルキルチオ基、又はアリール基を表す。〕

(もっと読む)

超伝導体構造、その製造方法、及び電子素子

【課題】鉄砒素系超伝導体の高品質な超伝導薄膜を備えた超伝導体構造、その製造方法、及び電子素子を提供すること。

【解決手段】基板と、前記基板上に形成され、III-V族半導体から成るバッファ層と、前記バッファ層上に形成され、下記式(1)で表される組成を有する超伝導薄膜と、を含み、前記超伝導薄膜におけるAs−As間隔は、前記III-V族半導体におけるV族原子間距離の約1倍であることを特徴とする超伝導体構造。式(1)LnFeAsO1-pFq(式(1)において、Lnは1種以上のランタノイド元素であり、0<p<1、0≦q<1)

(もっと読む)

テラヘルツ受信素子

【課題】高効率でテラヘルツ波を受信することが可能であるテラヘルツ受信素子を提供する。

【解決手段】本発明のテラヘルツ受信素子Aは、高抵抗基板1と、前記高抵抗基板1の第1の主面上に形成されているグランド面10と、前記高抵抗基板1の前記第1の主面に対向する第2の主面上に形成され、ヘテロ接合により形成されるチャネル層3を含む半導体層と、前記半導体層に形成され、前記チャネル層3とともに電界効果型トランジスタを形成するソース電極5、ゲート電極9及びドレイン電極6とを備え、前記半導体層は、前記ゲート電極9とショットキー接合されたストライプ状の凸部7を有し、前記ストライプ状の凸部7に含まれる複数の凸部それぞれは、前記ゲート電極9の下方において前記ソース電極5、前記ゲート電極9及び前記ドレイン電極6の並び方向に直交する。

(もっと読む)

半導体装置およびその製造方法

【課題】線形性に優れた半導体抵抗素子を提供する。

【解決手段】本発明の半導体装置は、GaAs基板101上に形成され、3−5族化合物半導体から構成されるHBT130と、GaAs基板101上に形成され、HBT130を構成する半導体エピタキシャル層の少なくとも1層から構成される半導体抵抗素子120とを備え、半導体抵抗素子120は、ヘリウム不純物を含む。

(もっと読む)

電界効果型トランジスタを有する半導体装置

【課題】良好な絶縁性を確保しつつ極めて高い誘電率を有するゲート絶縁膜の機能と、空乏層が形成されることのない金属性のゲート電極の機能とを備え、ゲート電圧のチャネル領域への静電的支配力を可及的に大きくすることのできる半導体装置を提供することを可能にする。

【解決手段】第1導電型の第1半導体層12に離間して設けられた第2導電型の第1ソース領域12aおよび第1ドレイン領域12bと、第1ソース領域と第1ドレイン領域との間の第1半導体層に設けられる第1チャネル領域12cと、第1チャネル領域上に設けられたハーフメタル強磁性金属の第1ゲート電極60と、第1ソース領域に接続するように設けられたハーフメタル強磁性金属の第1ソース電極50aと、を備え、第1ゲート電極の磁化64cの向きが、第1ソース電極の磁化64aの向きと略反平行である。

(もっと読む)

超伝導量子干渉素子

【課題】超高感度な超伝導量子干渉素子を提供する。

【解決手段】磁束を捕捉するための領域5を開けた二次元電子ガス3に超伝導体電極1,2を接続することにより、超伝導体−二次元電子ガス−超伝導体接合を超高感度な超伝導量子干渉素子として利用することができる。また、ゲート電極4を備える。これにより、超伝導量子干渉素子の臨界電流値ICや抵抗値RNを可変することができる。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜に起因する問題を排除し、微細化に適した電界効果トランジスタを含む半導体装置を提供する。

【解決手段】半導体で形成されるチャネル領域102と、チャネル領域102上に形成されるゲート電極310と、チャネル領域102を挟んで両側に形成される同一導電型を有するソース領域210およびドレイン領域220とを具備する電界効果トランジスタを含む半導体装置であって、ゲート電極320が金属原子を含有する導電体によって形成され、チャネル領域102の少なくとも一部とゲート電極310が接触しており、チャネル領域102と、ソース領域210およびドレイン領域220が異なる導電型を有することを特徴とする半導体装置。

(もっと読む)

スピンFET及びスピンメモリ

【課題】スピンFET/スピンメモリの低消費電力と高信頼性を実現する。

【解決手段】本発明の例に関わるスピンFETは、磁化方向が固定される磁気固着層12と、磁化方向が変化する磁気フリー層13と、磁気固着層12と磁気フリー層13との間のチャネルと、チャネル上にゲート絶縁層18を介して配置されるゲート電極19と、磁気フリー層13上に配置され、電場により磁化方向が変化する磁性層15とを備える。

(もっと読む)

炭化珪素系半導体素子および発光素子

【課題】バンドギャップを小さくすると共に電子散乱が抑制され、炭化珪素を用いたチャネル領域でのキャリア移動度を向上させた半導体素子、並びにレーザを発振する発光素子を提供する。

【解決手段】SiC基板11上に、AlドープされたSi0.9M0.1C混晶(Mは、Ge,Sn,Pbの少なくとも一種)よりなる薄膜または細線のAlドープSiMC層14が設けられている。また、SiC基板11の内部に、AlドープされたSi0.9M0.1C混晶(Mは、Ge,Sn,Pbの少なくとも一種)よりなる薄膜または細線のAlドープSiMC層14が設け発光させる。

(もっと読む)

スピントランジスタ

【課題】 空間的非一様Rashbaスピン軌道相互作用を用いてキャリアスピンの上向き下向きを分離し、さらにスピン偏極度に依存して、ドレイン電流が流れる超伝導接合を用いてドレイン電流の大きさをゲート電極で制御する。

【解決手段】 強磁性体ではなく常伝導体により構成された常伝導電極(ソース)101と、超伝導電極(ドレイン)102と、電極120と、ゲート電極103と、ゲートコンタクト層104と、二次元電子ガスが形成されているチャネル層105と、スペーサ層106と、キャリア供給層107と、バッファ層108と、基板109と、ゲート絶縁層110を備えて、空間的非一様Rashbaスピン軌道相互作用により、キャリアのスピン上向き下向きを分離することを可能とするゲート電極と、超伝導体により形成されたドレイン電極を用い、スピン偏極度によりドレイン電流を制御可能とし、磁場や磁性体を一切使わずにスピントランジスタを形成する。

(もっと読む)

導電性ナノワイヤの製造方法

本発明は、導電性または半導性ナノワイヤのアレイを製造する方法に関する。この方法は一般に、基板上に階段状原子テラスの微斜面を形成し、ドーパント材料の部分層を堆積させて、原子テラスの幅より狭い幅を有するナノストライプを形成し、好ましくはナノストライプおよび露出テラス面をオーバー層で被覆して多層構造体を形成し、場合によりこの多層構造体をアニールし、ドーパントナノストライプの原子を基板およびオーバー層のいずれか又は両方の内部へ拡散させてナノワイヤを形成する工程を含む。この方法は、規則的トポグラフィーパターンを備えた他の基板にも適用できる。本発明は、これらのナノワイヤを用いて作製した各種エレクトロニクスデバイスにも関する。  (もっと読む)

(もっと読む)

記憶素子、記憶装置および発光素子

【課題】 製造が容易で信頼性が高く、かつ、トンネル絶縁膜を必要としない記憶素子、記憶装置、および、発光素子を提供すること。

【解決手段】 この記憶素子は、導電性を有するリング13と、磁性体10と、第1の配線14と、第2の配線15とを備える。上記磁性体10は、リング13の貫通穴に挿通されている。第1の配線14は、リング13の外周面の第1部分から延び、第2の配線15は、上記外周面上における第2部分から延びている。この記憶素子は、第2の配線15から第1の配線14に電子を移動させた場合において、第1の配線14に流れる電流の電流値を検出することによって、磁性体10に書き込まれた記憶情報を読み取るようになっている。

(もっと読む)

高性能FETデバイス及び方法

【課題】半導体FETデバイスの機能及び高周波性能を改善するために用いることができる、ゲート電圧バイアス供給回路素子を備えたエピタキシャル積層構造を提供する。

【解決手段】半導体電界効果トランジスタ(FET)デバイスの性能を改善するためのゲート電圧バイアス供給回路素子を備えたエピタキシャル積層構造は、基板と、該基板上にエピタキシャルに成長したn型またはp型の第1の層の半導体膜であって、基板と第1の層膜との間にバッファ層が存在する可能性がある第1の層の半導体膜と、第1の半導体層上にエピタキシャルに成長した活性半導体層であって、活性層の導電型が第1の半導体層の導電型と反対であり、またFETを形成するのに十分なゲート、ドレイン、ソースへの電気コンタクトを備えたゲート領域及びドレイン領域及びソース領域を有する活性半導体層と、基板または第1の半導体層上の電気コンタクトと、デバイス性能を向上させるのに十分な電圧極性及び大きさで、ゲートコンタクト及び基板または第1の半導体層に電気的に接続されたゲート電圧バイアス供給回路素子と、からなる構造を利用する。  (もっと読む)

(もっと読む)

双方向型電界効果トランジスタおよびマトリクスコンバータ

【課題】単一のデバイスで双方向に流れる電流を制御できる双方向型電界効果トランジスタおよびこれを用いたマトリクスコンバータを提供する。

【解決手段】双方向型電界効果トランジスタは、半導体基板1と、半導体基板1上に設けられ、該基板1の主面に平行なチャネルと該チャネルのコンダクタンスを制御するためのゲート電極13aとを含むゲート領域と、チャネルの第1端側に設けられた第1領域と、チャネルの第2端側に設けられた第2領域とを備え、第1領域の第1電極11aからチャネルを介して第2領域の第2電極12aへ流れる順方向電流および第2電極12aからチャネルを介して第1電極11aへ流れる逆方向電流が、ゲート電極13aに印加されるゲート電圧によって制御される。

(もっと読む)

多量子ビット化装置、多量子ビット化方法、多量子ビット情報処理装置、多量子ビット情報処理方法。

【課題】原子核スピンを利用して一素子の中で多量子ビットを実現する。

【解決手段】原子核スピンの角運動量が1/2よりも大きい原子核を含む領域を備えた素子1に対し、当該領域における各エネルギー準位間のエネルギー差にそれぞれ対応した複数のマイクロ波を照射する。これにより、素子内部でマイクロ波による光子と原子核スピンとが結合するとともに核磁気共鳴が生じ、それぞれの原子核スピン間の遷移をコヒーレントに制御することを可能にする。

(もっと読む)

ダイヤモンド半導体素子及びその製造方法

【課題】 トランジスタ特性が優れ、また高効率で紫外線発光が可能なダイヤモンド半導体素子及びその製造方法を提供する。

【解決手段】 ダイヤモンド基板1上に、高濃度にBがドープされ夫々ソース及びドレインとなる高ドープダイヤモンド層2及び3を局所的に形成する。また、高ドープダイヤモンド層2と高ドープダイヤモンド層3との間には、極低濃度にBがドープされチャネル層となる低ドープダイヤモンド層4、Bがドープされゲートとなるドープダイヤモンド層6、及び極低濃度にBがドープされチャネル層となる低ドープダイヤモンド層5をこの順に形成する。更に、高ドープダイヤモンド層2上にソース電極となる金属電極7、高ドープダイヤモンド層3上にドレン電極となる金属電極8、ドープダイヤモンド層6上に、ゲート電極となる金属電極9を形成し、ダイヤモンドトランジスタ10にする。

(もっと読む)

量子リング、磁気センサ、磁気センサの使用方法および半導体装置

【課題】 単一の材料を含む種々の材料により良好なヘテロティック相を形成することができ、磁気センシングなどが可能な量子リング、この量子リングを用いた磁気センサおよびその使用方法、さらにはこの量子リングを用いた半導体装置を提供する。

【解決手段】 第1のランダムポテンシャルにより電子が局在的な振舞いをする物理系が発現する第1の領域11と、この第1の領域11を取り囲むようにこれに接して設けられ、第1のランダムポテンシャルより強度が小さい第2のランダムポテンシャルにより電子が波動的な振舞いをする物理系が発現する第2の領域13と、第2の領域13を取り囲むようにこれに接して設けられ、第2のランダムポテンシャルより強度が大きい第3のランダムポテンシャルにより電子が局在的な振舞いをする物理系が発現する第3の領域12により量子リングを構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 従来よりも高い温度でも動作できるクーロンブロケードを用いた量子効果素子

を提供すること。

【解決手段】 後方障壁閉じ込めポテンシャルを形成するための下部SiO2層43と上

部SiO2層45と、p−型層47と、これらSiO2層43、45、p−型層47各端

と交わる傾斜面51と、傾斜面51上にSiO2活性層61を介して設けられたゲート電

極31を有し、このゲート電極31のうち、SiO2層43、45の各端を覆うる部分は

狭くなっている。

(もっと読む)

1 - 20 / 22

[ Back to top ]