Fターム[5F102GC02]の内容

接合型電界効果トランジスタ (42,929) | ゲート配置 (2,808) | 横型FETの下部ゲート (57)

Fターム[5F102GC02]に分類される特許

1 - 20 / 57

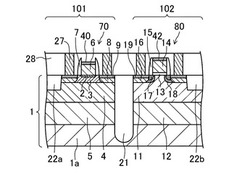

半導体装置及びその製造方法

【課題】低周波雑音が低減されるとともに、素子面積の小さい半導体装置及びその製造方法を製造コストを増大させずに提供する。

【解決手段】半導体装置は、第1導電型の下部ゲート領域4と、第2導電型のチャネル領域3と、第1導電型の上部ゲート領域2と、チャネル領域3の両側に位置する第2導電型のソース及びドレイン領域8と、上部ゲート領域2上に形成されたゲート電極6と、ゲート電極6の両側面上に形成されたサイドウォールスペーサ7とを有するJFET70を備える。上部ゲート領域2とソース及びドレイン領域8とは、チャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間しており、ソース及びドレイン領域8は、ゲート長方向におけるゲート電極6の両側方であってサイドウォールスペーサ7の外側を含む領域に形成されている。

(もっと読む)

半導体装置

【課題】電子走行層にFeが入り込むことを抑制し、半導体層等にクラックの発生が抑制される電界効果型トランジスタを提供する。

【解決手段】基板11の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層14と、高抵抗層14の上に形成された多層中間層15と、多層中間層15の上に半導体材料により形成された電子走行層16と、電子走行層の上に半導体材料により形成された電子供給層17と、を有し、多層中間層15は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする半導体装置。

(もっと読む)

電気化学素子および電気化学素子を用いた相補型回路

【課題】従来の電気化学素子とは逆極性でオンオフ動作を行うイオン移動型電気化学素子を提供する。この素子を従来型の電気化学素子とを組合せれば、低消費電力の相補型回路を構成できる。

【解決手段】イオン拡散材料として使用する酸化タンタルを挟んで一方にゲート電極を配置し、もう一方に絶縁物材料によって隔てられたソース電極とドレイン電極を配置する。このとき、ソース・ドレイン電極間の電気的接続を実現するゲート電圧(オン電圧)がオフ状態を実現するゲート電圧(オフ電圧)よりも低い電気化学素子が得られる。

(もっと読む)

半導体装置

【課題】高耐圧を確保でき、かつ大電流を流すことができるMOSトランジスタを備えた半導体装置を提供する。

【解決手段】P型拡散層15に起因してN型拡散層13に第1空乏層23が形成される。ゲート電極19にゲート電圧が印加されていない状態では、P型ポリシリコンからなるゲート電極19及びN型拡散層13の仕事関数差に起因してN型拡散層13に第2空乏層25が形成される。空乏層23,25によってソースコンタクト用拡散層9とドレインコンタクト用拡散層11が電気的に遮断される。ゲート電極19にゲート電圧が印加された状態では、第2空乏層25が消滅又は縮小することによってソースコンタクト用拡散層9とドレインコンタクト用拡散層11がN型拡散層13を介して電気的に導通する。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】チャネルとなるナノワイアの周囲をゲート電極が取り巻いて形成されているFETが、より容易に高い精度で製造できるようにする。

【解決手段】被覆ナノワイア103を配置した基板121のゲート電極形成領域の上に、被覆ナノワイア103に交差して下部ゲート電極122に重なる上部ゲート電極124を形成する。上部ゲート電極124の形成は、公知のリソグラフィー技術とリフトオフとにより行えばよい。例えば、被覆ナノワイア103が下部ゲート電極122と交差して配置されている基板121の上に、電子ビーム露光により電極形成部に開口を備えるレジストパターンを形成し、この上に、電極材料を堆積する。この後、先に形成してあるレジストパターンを除去すれば、上部ゲート電極124が形成できる。

(もっと読む)

半導体装置の製造方法

【課題】膜の形成によって生じる半導体基板の反りを緩和できる、半導体装置の製造方法を提供する。

【解決手段】SiC半導体基板10の主面上にイオン注入用マスク材18を形成する。マスク材は半導体基板とは異なる熱膨張係数を有する。レジスト膜20をマスクとしてドライエッチングにより複数の装置形成領域の間の領域上(ダイシングライン)14に切欠き部16aを有するマスク用膜16を形成する。イオン注入などの工程を経て半導体装置を形成後、ダイシングラインに沿って各装置形成領域に分離する。

(もっと読む)

半導体基板、電界効果トランジスタ、半導体基板の製造方法および電界効果トランジスタの製造方法

【課題】DWB法における貼り合わせ時にIII-V族化合物半導体層が受けるダメージを小さくするとともに、受けたダメージの影響および界面準位の影響を低く抑え、高いキャリアの移動度を有するIII-V族MISFETを提供する。

【解決手段】ベース基板102と第1絶縁体層104と半導体層106とを有し、ベース基板102、第1絶縁体層104および半導体層106が、ベース基板102、第1絶縁体層104、半導体層106の順に位置し、第1絶縁体層104が、アモルファス状金属酸化物またはアモルファス状金属窒化物からなり、半導体層が、第1結晶層108および第2結晶層110を含み、第1結晶層108および第2結晶層110が、ベース基板102の側から、第1結晶層108、第2結晶層110の順に位置し、第1結晶層108の電子親和力Ea1が、第2結晶層110の電子親和力Ea2より大きい半導体基板を提供する。

(もっと読む)

半導体装置、及びその製造方法

【課題】低消費電力・低電圧動作で、高利得・低歪特性を有し、かつ低コスト化が実現可能な半導体装置とその製造方法を提供する。

【解決手段】本発明に係る半導体装置のpチャネルFET2は、ソース/ドレインを形成する高濃度p型半導体層33と、その直下層に配設された低濃度p型半導体層32と、高濃度p型半導体層33上に形成された第1電極層41と、低濃度p型半導体層32の下方に形成され、ゲートとなる高濃度n型半導体層22と、その上に形成された第2電極層42とを備える。nチャネルFET3は、ソース/ドレインを形成する高濃度n型半導体層22と、ゲートを形成する高濃度p型半導体層33と、その下方に形成された低濃度n型半導体層21と、第1電極層42と、第2電極層42とを備える。

(もっと読む)

起動回路、スイッチング電源用IC及びスイッチング電源装置

【課題】起動回路を構成するJFETのピンチオフ維持のために生じる電力損失を低減できる起動回路、スイッチング電源用IC及びスイッチング電源装置を提供する。

【解決手段】起動電源(電源コンデンサ)と平滑コンデンサによる補助電源との間に接続され、起動電源による起動電流を平滑コンデンサに流すMOSFETと、ドレイン端子がMOSFETのドレイン端子に接続され、ソース端子が抵抗を介してMOSFETのゲート端子に接続されたJFETと、起動時にJFETのピンチオフ電圧が第1基準電圧値となるように制御し、起動後にJFETのピンチオフ電圧が第1基準電圧値未満の値である第2基準電圧値となるように制御するピンチオフ電圧制御部(可変電圧源)とを備える。

(もっと読む)

III族窒化物半導体装置

【課題】p型III族窒化物半導体8をドライエッチングして形成した平坦表面に電極を形成してもオーミック接触させることができない。

【解決手段】p型III族窒化物半導体8の電極形成範囲をドライエッチングして溝8dを形成し、その溝8dに金属20を充填して電極を形成する。p型III族窒化物半導体8のドライエッチング面は、エッチングによって生じた欠陥によってn型化しているために、平坦平面にドライエッチングしておいて電極を形成するとオーミック接触しない。溝8dを設けておくと、欠陥が少ない溝8dの側面においてp型III族窒化物半導体8と電極がオーミック接触し、半導体と電極の接触抵抗が低減する。

(もっと読む)

半導体装置

【課題】J−FETのピンチオフ電圧のばらつき低減を図ること、及び低いピンチオフ電圧の実現を図ることが課題となる。

【解決手段】P型半導体基板5上にN型エピタキシャル層6を堆積する。前記N型エピタキシャル層6の表面にN+型ソース層3を形成する。前記N型エピタキシャル層6の表面に前記N+型ソース層3を取り囲んで1対のP+型ゲート層2a、2bを形成する。前記P+型ゲート層2bから離間した領域の前記N型エピタキシャル層6の表面にN+型ドレイン層1を形成する。

(もっと読む)

高周波回路

【課題】最小ループと2セルループのオッドモード発振を共に抑制する高周波回路を提供する。

【解決手段】半導体基板上に並列に配列された複数のトランジスタと、第1の絶縁基板上に配置され、複数のトランジスタのゲート端子電極にそれぞれ接続された複数の入力整合回路と、第1の絶縁基板上に配置され、入力整合回路に隣接して配置された入力側第4発振抑制抵抗と、入力側第4発振抑制抵抗に直列接続された入力側第1キャパシタと、隣接する入力整合回路間を繋ぐ伝送線路上の点と入力側第1キャパシタ間に接続された入力側第1インダクタとを有する入力側発振抑制回路とを備え、入力側第1インダクタのインダクタンス値をL1、入力側第1キャパシタのキャパシタンス値をC1とすると、1/{2π(L1×C1)1/2}で表される入力側第1インダクタと入力側第1キャパシタの共振周波数が、2セルループの発振周波数fosc2に等しい高周波回路。

(もっと読む)

増幅回路装置

【課題】J−FETを増幅回路装置として採用する場合に、意図しない低周波信号の入力を防止し、規格値を超過するドレイン電流が発することを回避する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FETのゲート−ソース間に接続される抵抗とによってハイパスフィルタ5を構成する。ハイパスフィルタ5の遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。n型半導体基板上にバックゲート領域となるp型半導体層を設けてpn接合を形成し、この接合容量をハイパスフィルタ5の容量とする。

(もっと読む)

増幅回路装置

【課題】意図しない低周波信号の入力を防止し規格値を超過するドレイン電流が発生することを回避できる増幅回路装置を提供する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量4を付加し、当該容量4とJ−FET1のゲート−ソース間に接続される抵抗2とによってハイパスフィルタを構成する。ハイパスフィルタの遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。チップを構成する基板の裏面に絶縁層を設けてこれを誘電体とし、導電部材と基板とで平行平板型の容量4を接続する。

(もっと読む)

増幅回路装置

【課題】意図しない低周波信号の入力を防止することにより、規格値を超過するドレイン電流を発生することを回避できる接合形電界効果トランジスタを用いた増幅回路装置を提供する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FET1のゲート−ソース間に接続される抵抗2とによってハイパスフィルタ5を構成する。ハイパスフィルタ5の遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。チップを構成する基板の裏面にイオン注入によりn型不純物層を設け、p+型半導体基板とpn接合を形成して接合容量をハイパスフィルタ5の容量4とする。

(もっと読む)

接合型電界効果トランジスタ

【課題】 従来のJ−FETでは、動作領域内のゲート領域(トップゲート領域)は、動作領域外周に設けられた深いゲート領域を介してのみ、半導体基板(バックゲート領域)と接続していた。このため動作領域の中央と外周ではゲート抵抗にばらつきが生じ、ゲート抵抗の増加によるノイズ電圧の増加や、不均一動作によるゲインの低下が問題であった。

【解決手段】 格子状のゲート領域(トップゲート領域)を有するJ−FETにおいて、行列状にソース領域と交互に配置されていたドレイン領域の一部を深いゲート領域に置き換え、動作領域内にも深いゲート領域を設ける。ドレイン領域を一部省くことで生じるドレイン電流の流れない無効領域をできる限り減らすため、ソース領域が配置されるセルについてドレイン電流が流れない方向のゲート領域を短くする。

(もっと読む)

半導体デバイスおよび方法

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのショットキーダイオード10は、半導体からなる基板11と、基板11上に形成されたn型層12とを備えている。n型層12は基板11側の表面である第1の面12Aとは反対側の表面である第2の面12Bから第1の面12Aに向けて延びるように形成された溝13を有している。溝13の底部である底壁13Aに接触する位置には絶縁体としての酸化物層14が配置されており、かつ溝13の側壁13Bに接触するようにn型層12とショットキー接触可能な金属膜15が溝13を埋めるように形成されている。さらに、n型層12の第2の面12Bに接触するようにアノード電極16が配置されている。

(もっと読む)

半導体装置

【課題】半絶縁性基板に形成されたゲートパッドにマイナスの電圧が印加され、半絶縁性基板の裏面に形成された裏面電極にプラスの電圧が印加されても、リーク電流を抑制できる半導体装置を提供する。

【解決手段】裏面電極10が形成された半絶縁性基板11の表面上に並列に形成された、複数のゲート電極15がゲート電極接続部21に接続されるとともに、このゲート電極接続部21が複数に分割された半導体装置であって、ゲート電極接続部21間の半絶縁性基板11の表面に形成されたn型の抵抗層22と、このn型の抵抗層22の周囲を覆うように、p型不純物層23と、このp型不純物層23の周囲を覆うように、所望の濃度で形成されたn型不純物層24と、を具備し、ゲートパッド29は、ゲート電極接続部21と、このゲート電極接続部21に隣接するn型の抵抗層22上の引き出し電極25とを接続するように形成される。

(もっと読む)

コンプリメンタリー接合電界効果トランジスタを備えた炭化珪素半導体装置およびその製造方法

【課題】平坦面に対してデバイス形成できる絶縁分離構造を有し、かつ、高周波でのノイズ伝播や高温時でのリーク電流の発生を抑制できるCJFETを備えたSiC半導体装置を提供する。

【解決手段】絶縁分離層3にてn-型SiC層2やp-型SiC層4を絶縁分離する。これにより、平坦面に対してデバイス形成を行うことができる。このため、製造工程の簡略化を図ることが可能となる。また、PN分離ではなく、半絶縁性のイントリンシック層にて構成された絶縁分離層3によって絶縁分離構造を構成しているため、絶縁分離層3によって高周波ノイズを吸収することによる高周波でのノイズ伝播の抑制を行えると共に、高温時でのリーク電流の発生の抑制を行うことが可能となる。

(もっと読む)

1 - 20 / 57

[ Back to top ]