Fターム[5F102GR09]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 半導体基体内に付加領域を設けたもの (876) | 絶縁領域(高抵抗領域を含む) (273)

Fターム[5F102GR09]に分類される特許

141 - 160 / 273

半導体装置とその製造方法

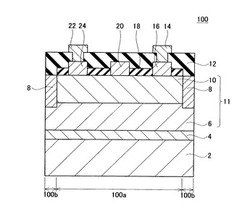

【課題】 ヘテロ接合を有する半導体装置において、素子領域から電流がリークすることを抑制する。

【解決手段】 半導体装置100は、バンドギャップを異にする窒化物半導体層6、10が積層されている半導体積層部11を有しており、半導体積層部11が素子領域100aと素子領域100aの周囲に形成されている素子分離領域100bを備えている。素子領域100aは、素子分離領域100bにより他の領域から絶縁されている。半導体装置100は、素子領域100a内の半導体積層部11の表面に、主電極に接続する一対の電極群24,16を形成する電極群形成工程と、素子分離領域100b内の半導体積層部11の表面に、スパッタ法を用いてスパッタ層12を形成するスパッタ工程を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】細く深いバイアホールが設けられる場合でも、ソースインダクタンスを十分に低減し、高い放熱効率を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】SiC基板1上に化合物半導体領域2を形成し、その後、化合物半導体領域2上にゲート電極4g、ソース電極4s及びドレイン電極4dを形成し、更に、化合物半導体領域2上にソース電極4sに接続されるAu膜10を形成する。次に、SiC基板1の裏面にレーザビームを照射して、SiC基板1、化合物半導体領域2及びAu層を貫通するバイアホール21を形成する。次に、バイアホール21の側面及びSiC基板1の裏面にわたってビア配線14を形成する。次に、バイアホール21内に溶融金属滴32を充填し凝固させることにより、導通ビアを形成する。そして、溶融金属滴32を充填する際に、SiC基板1を溶融金属滴32に対して相対的に振動させる。

(もっと読む)

半導体装置およびその製造方法

【課題】追加部材を形成することなく表面保護膜の端部での剥がれを防止でき、チップエッジからの水分浸入を防止して信頼性(耐湿性)を向上できる半導体装置を提供する。

【解決手段】この半導体装置では、エピタキシャル層4Aを覆う表面保護膜11が高抵抗GaAs層(素子間絶縁層)5の外周側の外周エピタキシャル層4A−1の一部を覆って上記一部に接しているので、表面保護膜11の端部の密着性が向上して外部からの水分侵入を防止できる。

(もっと読む)

接合型電界効果トランジスタ

【課題】 基板が低濃度の半導体基板のみからなるJ−FETは、静電破壊耐量は高いが、ノイズ電圧が大きく、ノイズ特性のばらつきも大きい問題があった。一方、ノイズ対策として、高濃度の半導体基板に低濃度の半導体層を積層した基板構造のJ−FETでは、ゲート抵抗の低減によりノイズ電圧を小さくできノイズ特性も安定する反面、静電破壊耐量が劣化する問題があった。

【解決手段】 高濃度半導体基板の条件を、所望の静電破壊耐量が得られる比抵抗及び厚みとし、これに低濃度の半導体層を積層した基板構造とする。これにより静電破壊耐量を劣化させない範囲でノイズ特性のばらつきを抑え、ノイズ電圧を小さくすることができる。また同時にノイズ特性に影響を与えない範囲で静電破壊耐量を向上させることができる。従って、従来構造と比較して市場要求に比較的柔軟に対応できるJ−FETを提供できる。

(もっと読む)

接合型電界効果トランジスタ

【課題】 基板が低濃度の半導体基板のみからなるJ−FETは、静電破壊耐量は高いが、ノイズ電圧が大きく、ノイズ特性のばらつきも大きい問題があった。一方、ノイズ対策として、高濃度の半導体基板に低濃度の半導体層を積層した基板構造のJ−FETでは、ゲート抵抗の低減によりノイズ電圧を小さくできノイズ特性も安定する反面、静電破壊耐量が劣化する問題があった。

【解決手段】 高濃度半導体基板に低濃度の第1半導体層と、第1半導体層より高濃度の第2半導体層を積層する基板構造とする。これにより静電破壊耐量を劣化させない範囲でノイズ特性のばらつきを抑え、ノイズ電圧を小さくすることができる。また同時にノイズ特性に影響を与えない範囲で静電破壊耐量を向上させることができる。従って、従来構造と比較して市場要求に比較的柔軟に対応できるJ−FETを提供できる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の周囲に形成される空洞と保護膜に形成されるホールとの境界部分の開口を封止しやすい構造を実現する。

【解決手段】半導体装置を、ゲート電極3と、高さが低い部分6Aと高さが高い部分6Bとを有する階段状の空間6をゲート電極3の周囲に有する保護膜4と、高さが低い部分6Aに接するように保護膜4に形成されたホール5とを備えるものとする。

(もっと読む)

スイッチング回路

【課題】、接合型電界効果トランジスタ(JFET)の高温動作時のオン抵抗を低減して、高温時の動作特性を改善すること。

【解決手段】出力切替回路34は、温度検出装置33によって検出された温度が所定の閾値温度以上であるとき、第2の駆動回路32に出力切替指示を与える。これにより、第2の駆動回路は、MOSFET35を駆動して、JFET10に立ち上がり電圧(順方向降下電圧)VF以上のゲート電圧VGSが印加され、JFETはバイポーラ動作される。これにより、高温時のJFET10のオン抵抗の増加を抑制できる。

(もっと読む)

半導体装置及びその製造方法

【課題】高電圧動作時においても良好な特性を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】半絶縁性のSiC基板1上に化合物半導体領域2が形成されている。i−GaN層2aの表層部分は電子走行層として機能し、その下の部分はバッファ層として機能する。バッファ層は、SiC基板1の表面に存在する格子欠陥の電子走行層への伝播を防止している。n−AlGaN層2cは電子供給層として機能する。n−GaN層2dには、n−AlGaN層2cを露出する2個の開口部が形成されており、開口部の各々に、オーミック電極がソース電極4又はドレイン電極5として形成されている。更に、n−GaN層2d、ソース電極4及びドレイン電極5を覆うシリコン窒化膜10が形成されている。シリコン窒化膜10には、1.4×1022個/cm3以上のSi−H結合基が含まれている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電流コラプスの小さな窒化物半導体デバイス用のショットキ電極を提供する。

【解決手段】窒素を含む3−5族化合物の半導体層と、前記半導体層に接して前記半導体層より上層に形成された導電体層と、を備えた半導体装置であって、前記導電体層は、2種以上の金属層が積層された積層金属層が合金化されて形成された合金であり、前記合金の仕事関数は、合金化前に前記半導体層に接していた金属の仕事関数より大きい半導体装置が提供される。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】化合物半導体デバイスのスイッチング速度等の性能を向上できる半導体基板を提供する。

【解決手段】シリコン基板102と、シリコン基板の上に形成された絶縁膜104であってアスペクト比が√3/3以上のシリコン基板に達する開口部を有する絶縁膜104と、開口部に形成された化合物半導体結晶108であって絶縁膜104の表面より凸に形成されたシード化合物半導体結晶108と、シード化合物半導体結晶108の特定面をシード面として、絶縁膜の上にラテラル成長されたラテラル成長化合物半導体層112と、を備えた半導体基板。

(もっと読む)

化合物半導体スイッチ回路装置

【課題】スイッチMMICのスイッチング素子を構成するFETに櫛状パターンのゲート電極を採用した場合、線形性には優れるが、高調波歪み特性が良好でなく、特にハイパワー用途に適用するには限界があった。またDPDTでは信号経路が変わった場合に櫛状パターンの櫛歯部の先端から高周波信号が伝播することとなり、高周波信号の漏れが大きくなる問題があった。

【解決手段】櫛状パターンのゲート電極を有する第1FETと、曲折パターンのゲート電極を有する第2FETを組み合わせて多段接続し、スイッチング素子を構成する。またスイッチング素子の両端を櫛状パターンのゲート電極のFET(第1FET)とし、ゲート電極を対向させて配置する。ゲート電極の配線部によってパッドから伝播する高周波信号を遮断できる。これにより線形性と高調波歪み特性がいずれも良好なスイッチMMICを提供できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】GaN系電界効果トランジスタをノーマリオフで動作させつつ、チャネルの電流密度を増加する。

【解決手段】窒素を含む3−5族化合物半導体のチャネル層と、前記チャネル層に電子を供給する電子供給層であって前記チャネル層に対向する面の反対面に溝部を有する電子供給層と、前記電子供給層の前記溝部に形成されたp形半導体層と、前記p形半導体層と接して形成された、または、前記p形半導体層との間に中間層を介して形成された制御電極と、を備えた半導体装置を提供する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】GaN系電界効果トランジスタをノーマリオフで動作させつつ、チャネルの電流密度を増加する。

【解決手段】窒素を含む3−5族化合物半導体のチャネル層と、前記チャネル層に電子を供給する電子供給層と、前記電子供給層の前記チャネル層に対向する面の反対面に形成された、窒素を含む3−5族化合物の真性またはn形の半導体層と、前記半導体層と接して形成された、または、前記半導体層との間に中間層を介して形成された制御電極と、を備えた半導体装置を提供する。

(もっと読む)

ZnO系トランジスタ

【課題】高性能、高品質のチャ領域を構成することができるZnO系トランジスタを提供する。

【解決手段】MgZZnO基板1上に、MgXZnO層2、MgYZnO層3が積層されている。MgXZnO層2とMgYZnO層3の界面で2次元電子ガスが発生する。4はゲート絶縁膜又は有機物電極であり、MgYZnO層3に接して形成されている。ゲート絶縁膜又は有機物電極4上にはゲート電極5が、ドナードープ部3a上には各々ソース電極6、ドレイン電極7が形成されている。このように、トランジスタのチャネル領域をMgZnO層で形成する。

(もっと読む)

チップ内隣接構成デュアル静電誘導トランジスタ及びこれを用いたオーディオ用パワーアンプ回路

【課題】解決しようとする課題は、差動増幅器の入力段の対構成の差動トランジスタに最適な特性の揃ったディュアル静電誘導トランジスタを提供して、トランジスタ製造上の選別を容易にし、対形成不良を少なくし、回路製作上の調整作業を容易にすることである。

【解決手段】本発明では、半導体の1ウェーハ内の隣同士に隣接して、対構成の同一導電型、同一サイズの静電誘導トランジスタを構成して、差動増幅器の入力段用には、1チップとして組立し提供したものである。

(もっと読む)

半導体装置及びその製造方法

【課題】ダイオードの外付けによる部品点数の増加及び占有面積の増大を抑えた、高いアバランシュエネルギー耐量を有する窒化物半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板10と、半導体基板10の第1の面側にカソード12が形成され、第2の面側にアノード13が形成されたダイオード11と、半導体基板10の上に形成されたトランジスタ21とを備えている。トランジスタ21は、半導体基板10の上に形成された半導体層積層体23と、半導体層積層体23の上又は上部に互いに間隔をおいて形成されたソース電極24及びドレイン電極25と、ソース電極24とドレイン電極25との間に形成されたゲート電極27とを有している。ソース電極24は、アノード13と電気的に接続され、ドレイン電極25は、カソード12と電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、デバイス特性及び信頼性を向上させる。

【解決手段】半導体装置を、半導体基板6上に形成された化合物半導体積層構造1と、少なくとも化合物半導体積層構造1の表面に露出している部分を覆う第1絶縁膜4と、第1絶縁膜4上に形成された第2絶縁膜5とを備えるものとし、第2絶縁膜5を第1絶縁膜4よりも水素を多く含むものとする。

(もっと読む)

窒化物半導体装置の製造方法

【課題】 電流コラプスの抑制と高耐圧化が実現できると共に、微結晶構造の窒化物半導体層を緩やかに傾斜した形状に形成し、電界集中を緩和することができる窒化物半導体装置の製造方法を提供する。

【解決手段】 アルミニウムを含まない高絶縁性の第2の窒化物半導体層に形成した側壁が斜めに傾斜した凹部内に、ゲート電極を形成する。側壁が斜めの凹部は、第2の窒化物半導体装置の成長温度を徐々に低くしながら成長させ、その後、成長温度に応じてエッチングレートが異なるエッチング液を使用してエッチングして形成する。

(もっと読む)

ヘテロ接合電界効果型トランジスタおよびその製造方法

【課題】ソース/ドレイン電極の下側のポテンシャル障壁を低くすることにより、寄生抵抗の増大を防止することを目的とする。

【解決手段】本発明に係るヘテロ接合電界効果型トランジスタは、窒化物半導体からなるヘテロ接合電界効果型トランジスタであって、チャネル層30と、チャネル層30上にスペーサ層40を介して形成されたバリア層50を備える。そして、バリア層50上に形成されたゲート電極80と、バリア層50上に、ゲート電極80を挟んで形成されたソース/ドレイン電極70とを備える。スペーサ層40は、ゲート電極80の下側の領域に形成され、チャネル層30およびバリア層50のいずれよりもバンドギャップが大きい第1のスペーサ層41を備える。そして、スペーサ層40は、ソース/ドレイン電極70の下側の領域に形成され、第1のスペーサ層41よりもバンドギャップが小さい第2のスペーサ層42を備える。

(もっと読む)

窒化物半導体トランジスタ及びその製造方法

【課題】電流コラプスを抑制し、パワートランジスタに適用可能なノーマリーオフ型の窒化物半導体トランジスタ及びその製造方法を提供する。

【解決手段】窒化物半導体トランジスタは、基板11と、基板11の上に形成された第1の窒化物半導体層13と、第1の窒化物半導体層13の上に形成され、第1の窒化物半導体13と比べてバンドギャップエネルギが大きい第2の窒化物半導体層14と、第2の窒化物半導体層14の上に形成され、開口部を有する第3の窒化物半導体層15とを備えている。開口部を埋めるようにp型の第4の窒化物半導体層16が形成され、第4の窒化物半導体層16の上にはゲート電極21が形成されている。

(もっと読む)

141 - 160 / 273

[ Back to top ]