Fターム[5F102GS07]の内容

接合型電界効果トランジスタ (42,929) | ゲート電極構造 (2,097) | 平面形状 (492)

Fターム[5F102GS07]の下位に属するFターム

Fターム[5F102GS07]に分類される特許

1 - 20 / 166

半導体装置の製造方法

【課題】チャージアップに起因するリーク電流及び閾値電圧の変動を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体層内に、活性領域30を含むFET34、活性領域30からなるスクライブライン36、FET34とスクライブライン36との間に位置する不活性領域32、及び不活性領域32を横断してFET34とスクライブライン36とを電気的に接続する接続領域38を設ける工程と、半導体層上に絶縁膜20を形成する工程と、ドライエッチング法により絶縁膜20に選択的に開口部21を形成する工程と、を有する半導体装置である。

(もっと読む)

窒化物半導体装置

【課題】櫛型形状のソース電極とドレイン電極が交差指状に配置された電極構造を有し、各櫛形電極の先端部での電界集中が緩和された窒化物半導体装置を提供する。

【解決手段】ゲート電極5と電気的に接続され、ゲート電極5とドレイン電極4間で絶縁膜7上に配置されたゲートフィールドプレート50と、ソース電極3と電気的に接続され、絶縁膜8を介して窒化物半導体層と対向するようにゲートフィールドプレート50とドレイン電極4間の上方に配置されたソースフィールドプレート30とを備え、ゲート電極5とドレイン電極4間の距離、ゲートフィールドプレート50のドレイン側端部とゲート電極5のドレイン側端部間の距離、及びソースフィールドプレート30のドレイン側端部とゲートフィールドプレート50のドレイン側端部間の距離の少なくともいずれかが、ソース電極3とドレイン電極4の、歯部分の直線領域よりも歯部分の先端領域において長い。

(もっと読む)

高周波回路装置

【課題】 電気的特性を向上させた高周波回路装置を提供する。

【解決手段】 高周波回路装置は、一端同士1331,1341が互いに離間して対向した2つの伝送線路133,134と、2つの伝送線路の一方の一端に実装され、該実装面となる下面電極30と、該実装時に下面電極の上方に位置する上面電極32を備えるキャパシタCと、2つの伝送線路の対向する一端同士の間の領域に配置され、一端同士を電気的に接続する抵抗素子Rと、キャパシタの上面電極と2つの伝送線路の他方との間を電気的に接続する接続導体135とを備える。

(もっと読む)

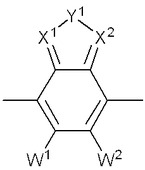

高分子化合物及びそれを用いた光電変換素子

【課題】開放端電圧が高い有機光電変換素子を製造しうる高分子化合物を提供することを目的とする。

【解決手段】式(1)で表される構成単位を有する高分子化合物。

(1)

〔式中、X1及びX2は、それぞれ独立に、窒素原子又は=CH−を表す。Y1は、硫黄原子、酸素原子、セレン原子、−N(R1)−又は−CR2=CR3−を表す。R1、R2及びR3は、それぞれ独立に、水素原子又は置換基を表す。W1は、シアノ基、ニトロ基、フッ素原子を有する1価の有機基又はフッ素原子を表す。W2は、W1とは異なる基を表す。〕

(もっと読む)

印刷可能な半導体構造、並びに関連する製造方法及び組立方法

【課題】選択された物理的寸法、形状、組成、及び、空間的配置を有する高品質印刷可能半導体素子の製造、転写、組み立てのための高歩留りの経路を与える。

【解決手段】大面積基板及び/又はフレキシブル基板を含む基板上へのミクロサイズ及び/又はナノサイズの半導体構造の配列の高精度の位置合わせ転写及び集積を行なう。また、バルクシリコンウエハ等の低コストバルク材料から印刷可能半導体素子を形成する方法、及び、広範囲の機能的な半導体デバイスを形成するための多目的で商業的に魅力的な印刷ベースの製造ブラットフォームを可能にするスマート材料処理を行う。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】耐圧を高めた窒化物半導体素子及び製造方法を提供する。

【解決手段】第1の窒化物層31と該第1の窒化物層31の材料より広いエネルギバンドギャップを有する材料を含む第2の窒化物層33とが異種接合され、該接合界面寄りに2次元電子ガス(2DEG)チャネルが形成された窒化物半導体層30と、窒化物半導体層30上にオーミック接触されるソース電極50とドレイン電極60と、ソース電極50とドレイン電極60との間の窒化物半導体層30上に形成され、ソース電極50から所定距離だけ離間された第1の側壁からドレイン側へ長く形成された多数のP型窒化物半導体セグメント80と、ソース電極50とドレイン電極60との間でソース電極50に近く形成され、多数のP型窒化物半導体セグメント80間の窒化物半導体層30上及びP型窒化物半導体セグメント80上に接触されるゲート電極70とを含む。

(もっと読む)

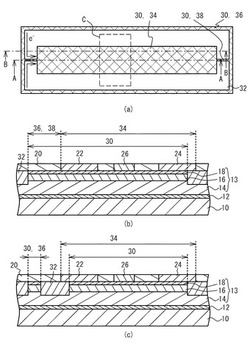

半導体装置および半導体装置の製造方法

【課題】半導体装置について、小型化を図りつつ、ドレイン耐圧を向上する。

【解決手段】ゲート電極20と、ゲート電極20と離間するソース電極24と、平面視でゲート電極20からみてソース電極24の反対側に位置し、かつゲート電極20と離間するドレイン電極22と、平面視でゲート電極20とドレイン電極22の間に位置し、絶縁膜26を介して半導体基板10上に設けられ、かつゲート電極20、ソース電極24およびドレイン電極22と離間する少なくとも一つのフィールドプレート電極30と、絶縁膜26中に設けられ、かつフィールドプレート電極30と半導体基板10を接続する少なくとも一つのフィールドプレートコンタクト40と、を備え、平面視でフィールドプレート電極30は、フィールドプレートコンタクト40からソース電極24側またはドレイン電極22側の少なくとも一方に延伸している。

(もっと読む)

窒化物系半導体装置

【課題】ダイオード部とトランジスタ部の面積比率を自由に設定することが可能な窒化物系半導体装置を提供することを目的とする。

【解決手段】第1HEMT部30及び第2HEMT部31から成るトランジスタ部1と、第1電極24と電気的に短絡された第1ショットキー電極28及び第1ゲート電極26と電気的に第2ショットキー電極29から成るダイオード部2と、を備えて構成されている。また、第1電極24と第2電極25との間の領域に第1電極24に沿って、第1ゲート電極26及び第1ショットキー電極28が交互に形成され、かつ、第2電極25に沿って、第2ゲート電極27及び第2ショットキー電極29が交互に形成されている。さらに、第1ゲート電極26と第2ゲート電極27とは、対向して形成されており、第1ショットキー電極28と第2ショットキー電極29とは対向して形成されている。

(もっと読む)

トランジスタ回路、双方向スイッチ回路、ダイオード回路及びトランジスタ回路の製造方法

【課題】トランジスタのゲートへの電流を防ぐ。

【解決手段】ノーマリーオン型の第1トランジスタと、ドレインが、第1トランジスタのソースと接続され、第1トランジスタとカスコード接続されたノーマリーオフ型の第2トランジスタと、第2トランジスタのソースと第1トランジスタのゲートとの間に設けられた、第2トランジスタのソースから第1トランジスタのゲートへと流れる電流を抑制する第1電流抑制部とを備えるトランジスタ回路を提供する。

(もっと読む)

炭化珪素半導体装置

【課題】スイッチング素子のソースおよびドレイン間に還流ダイオードが接続された構造を有する炭化珪素半導体装置を一の炭化珪素基板を用いて提供する。

【解決手段】第1層34は第1導電型を有する。第2層35は、第1層34の一部が露出されるように第1層34上に設けられ、第2導電型を有する。第1〜第3不純物領域は、第2層35を貫通して第1層34に達する。第1および第2不純物領域11、12の各々は第1導電型を有する。第3不純物領域13は、第1および第2不純物領域11、12の間に配置され、かつ第2導電型を有する。第1〜第3電極S1、D1、G1は、第1〜第3不純物領域11〜13のそれぞれの上に設けられている。ショットキー電極SKは、第1層34の一部の上に設けられ、第1電極S1に電気的に接続されている。

(もっと読む)

炭化珪素半導体装置

【課題】オン抵抗が低く高速動作が可能でありノーマリオフ特性を有し、かつ一の基板を用いて構成された炭化珪素半導体装置を提供する。

【解決手段】第1、第2、第4および第5不純物領域11、12、21、22は第1導電型を有し、第3不純物領域13は第2導電型を有する。第1〜第3不純物領域11〜13は第1導電型の第1層34に達する。第4および第5不純物領域21、22は第2層35上に設けられている。第1〜第5電極S1、D1、G1、S2、D2は第1〜第5不純物領域のそれぞれの上に設けられている。第1および第5電極S1、D2の間と、第3および第4電極G1、S2の間とは電気的に接続されている。第4および第5不純物領域21、22の間を覆うゲート絶縁膜I2上に第6電極G2が設けられている。

(もっと読む)

テラヘルツ波素子

【課題】テラヘルツ波を発生又は検出するテラヘルツ波素子において、単色性が良いテラヘルツ波を効率良く出射する。

【解決手段】テラヘルツ波素子は、基板101の上に形成された第1の半導体層102と、第1の半導体層102の上に形成された第2の半導体層104と、第2の半導体層104の上に形成されたゲート電極106と、第2の半導体層104の上にゲート電極106を挟んで対向するように形成されたソース電極107及びドレイン電極108と、第2の半導体層104の上におけるゲート電極106とソース電極107との間及びゲート電極106とドレイン電極108との間に形成され、複数の金属膜109が周期的に配置された周期構造を有する周期金属膜109A,109Bと、ゲート電極106及び複数の金属膜109の上方に配置された第1のミラー111と、基板101の下に形成された第2のミラー112とを備えている。

(もっと読む)

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

【課題】印刷可能半導体素子を製造するとともに、印刷可能半導体素子を基板表面上に組み立てるための方法及びデバイスを提供する。

【解決手段】デバイス、デバイス部品は、幅広いフレキシブル電子デバイス及び光電子デバイス並びにデバイスの配列を高分子材料を備える基板上に形成する。伸張形態で良好な性能が得られる伸縮可能な半導体構造及び伸縮可能な電子デバイスを形成する。

(もっと読む)

電動機駆動装置

【課題】装置全体としての長寿命化を図りつつ、装置全体としての小型化を可能とする電動機駆動装置を提供する。

【解決手段】駆動部12は、横型半導体素子からなる1回路2接点式の切替素子16,17を2つ有している。第1の切替素子16は、コモン端子160を電動機11に接続し、第1の端子161および第2の端子162を電源部15に接続する。第2の切替素子17は、コモン端子170を電動機11に接続し、第1の端子171および第2の端子172を電源部15に接続する。制御部14は、各切替素子16,17において、コモン端子160,170が、第1の端子161,171および第2の端子162,172に対して択一的に接続されるように、各切替素子16,17を個別に切替制御する。

(もっと読む)

電界効果トランジスタ

【課題】動的な耐圧であるダイナミック耐圧の低下を抑制できるGaN系のHFETを提供する。

【解決手段】このGaN系のHFETでは、各ソース電極12の長手方向の長さL2と各ドレイン電極11の長手方向の長さL1とが同じ長さである。また、ソース電極12の長手方向の端12A,12Bの長手方向の位置は、ドレイン電極11の長手方向の端11A,11Bの長手方向の位置と一致している。ソース電極12の長手方向の両端12A,12Bがドレイン電極11の長手方向の両端11A,11Bよりも長手方向外方へ突出していない構成により、ソース電極12の端12A,12Bからドレイン電極11の端11A,11Bへ向かって電子流が集中することを回避できる。

(もっと読む)

電界効果トランジスタ

【課題】動的な耐圧であるダイナミック耐圧の低下を抑制できるGaN系のHFETを提供する。

【解決手段】このGaN系のHFETでは、ドレイン電極12の長手方向の端12A,12Bから長手方向と直交する短手方向に伸ばした仮想線M1,M2よりも長手方向外方に位置すると共にソース電極11に隣接する領域の下のGaN系積層体5、およびドレイン電極12の長手方向の端12A,12Bに長手方向外側に隣接する領域の下のGaN系積層体5に2次元電子ガスが存在しない2次元電子ガス除去領域31が形成されている。2次元電子ガス除去領域31の存在によって、スイッチング時の動的な電界変動によってソース電極11の端部からドレイン電極12の端部へ向かって電子流が集中することを回避できる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 JFET等のような低ノイズ特性が要求される半導体装置において、発生するノイズを低減すると共に、半導体装置を小さい寸法で製造する。

【解決手段】 半導体装置は、半導体層(101)に形成された素子分離(102)、第1導電型の不純物層(104)、第1導電型のソース領域(106)、第1導電型のドレイン領域(107)、第2導電型のゲート領域(105)、絶縁膜(108)を介して形成された制御電極(109)を備える。制御電極(109)に電圧を印加すると、半導体装置の動作中に制御電極(109)の下の不純物層(104)に空乏層を発生させることができ、キャリアは絶縁膜(108)と不純物層(104)の界面から離れて流れる。

(もっと読む)

半導体装置及び電力増幅器

【課題】トランジスタの占有面積をほとんど増やすことなく、かつ、HBTとHFETとを接続する配線による悪影響を受けないBi−HFET(半導体装置)を提供する。

【解決手段】基板101上に形成されたHFET160と、HFET160上に形成されたHBT170とを備え、HFET160は、チャネル層102と、コンタクト層104とを有し、HBT170は、HFET160のコンタクト層104と接続、又は、一体化されたサブコレクタ層107と、コレクタ層108と、ベース層109と、エミッタ層110と、エミッタキャップ層111と、エミッタコンタクト層112とを有し、コレクタ層108、ベース層109及びエミッタ層110は、メサ形状の構造体であるベースメサ領域830を構成し、ゲート電極202は、第一のコレクタ電極203とベースメサ領域830との平面的な間に設けられたリセス領域820内に形成されている。

(もっと読む)

半導体回路

【課題】ON状態とOFF状態のコントラスト(High/Low比)が高く、消費電力が少なく、端子数および配線数が少ない回路を提供する。

【解決手段】半導体回路は、複数個のNOT回路が縦続接続され、最終段のNOT回路の出力端子と初段のNOT回路の入力端子とが接続されている。NOT回路は、ゲート11とソース13とが一体構造で形成され、ゲート10が入力端子3に接続され、ドレイン12が出力端子5に接続され、ゲート11およびソース13がグランド端子6に接続されたインプレーンダブルゲートトランジスター1と、ゲート20,21およびソース23が一体構造で形成され、ゲート20,21およびソース23がインプレーンダブルゲートトランジスター1のドレイン12に接続され、ドレイン22がバイアス端子4に接続された自己バイアス型インプレーントランジスター2とから構成される。

(もっと読む)

1 - 20 / 166

[ Back to top ]