Fターム[5F102HC11]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | 蒸着、スパッタ (562)

Fターム[5F102HC11]の下位に属するFターム

斜め方向からの蒸着 (2)

蒸着の際に段切れを利用するもの

Fターム[5F102HC11]に分類される特許

541 - 560 / 560

半導体装置及びその製造方法

【課題】耐圧に優れ、強度の高いIII−V族窒化物半導体からなる半導体装置を実現する。

【解決手段】本発明の構造では、第1のソース電極106がバイアホール112を介して導電性基板101に接続されており、また、第2のソース電極110が形成されている。これにより、ゲート電極108とドレイン電極107との間に高い逆方向電圧が印加されても、ゲート電極108のうちドレイン電極107に近い側の端部に起こりやすい電界集中を効果的に分散または緩和することができるため、耐圧が向上する。また、素子形成層を形成する基板として導電性基板101を用いているため、導電性基板101には裏面まで貫通するバイアホールを設ける必要がない。したがって、導電性基板101に必要な強度を保持したまま、第1のソース電極106と裏面電極115とを電気的に接続することができる。

(もっと読む)

電界効果トランジスタ

【課題】 電界効果トランジスタ特性の劣化を低減し、微細化を実現することが可能なガリウム砒素電界効果トランジスタを提供する。

【解決手段】 基板31と、メサ11と、メサ11上に形成されたソース電極13、ドレイン電極14及びゲート電極12とを備え、メサ11上面には、櫛形状のソース電極13及びドレイン電極14の指状部13a、14aが互いに組み合わさるように対向して位置し、かつミアンダ形状のゲート電極12がソース電極13とドレイン電極14との間に位置する形状の上面パターンが形成され、ソース電極13及びドレイン電極14の指状部13a、14aの基部となる共通部13b、14bは、メサ11上面に形成され、ゲート電極12における指状部13a、14aと平行な直線部12aの下方に位置する部分は、ゲート電極12における隣り合う直線部12aをつなぐ屈曲部12bの下方に位置する部分と電気的に分離されている。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】 放熱特性を損なうことなく基板リーク電流と誘電損失とを低減させた窒化物半導体装置およびその製造方法を提供する。

【解決手段】 表面と裏面とを有するシリコン基板と、シリコン基板の表面上に設けられた窒化物半導体層とを有する窒化物半導体装置において、シリコン基板の裏面上に、高熱伝導性絶縁物質層が設けられる。また、窒化物半導体装置の製造方法が、窒化物半導体層を形成したシリコン基板を溶液に浸漬し、電気化学法によりシリコン基板の裏面に高熱伝導性絶縁物質層を析出させる工程を含む。

(もっと読む)

窒化物系化合物半導体装置及びその製造方法

【課題】 極めて簡単な手段を採ることで、窒化物系化合物半導体と電極との接触抵抗を低下させ、また、電極表面及び電極パターンエッジのモフォロジを良好に維持することを可能にして高い信頼性を実現できるようにする。

【解決手段】 金属窒化物、例えばTiNを含む第1の層及びMox Ga1-x (0<x<1)を含む第2の層が半導体に近い側から前記の順に積層されてなる電極を備えてなることが基本になっている。

(もっと読む)

半導体装置とその製造方法

【課題】 ヘテロ構造を備えているとともにIII-V族化合物半導体で構成される半導体装置において、安定的なノーマリオフ動作を実現する。

【解決手段】 p−GaN層32とSI−GaN層62とAlGaN層34が積層され、AlGaN層34の表面側にショットキー接続されているゲート電極44を備えている半導体装置である。p−GaN層32とSI−GaN層62よりもAlGaN層34のバンドギャップの方が大きく、さらに、SI−GaN層62は、その不純物濃度が1×1017cm-3以下であることを特徴としている。

(もっと読む)

窒化物半導体ヘテロ構造電界効果トランジスタ構造とその作製法

【課題】界面の急峻性等の品質に優れたInGaNチャネルまたは、高いバンドオフセットを持つバリア層を用いた窒化物半導体HFET構造の作製を可能とする、およびHFET構造の作製の再現性を向上する。

【解決手段】窒化物半導体薄膜上に、InxGa1−xN(0≦x≦1)層を有し、その上に窒化物半導体中間層を有し、その上にAlN層を有する窒化物半導体素子構造とする。窒化物半導体薄膜上に、InxGa1−xN(0≦x≦1)層を有し、その上にAlN層を有する窒化物半導体素子構造とする。

InxGa1−xN層は組成の異なる多層膜とする。

窒化物半導体中間層は、GaN、もしくはAlN、もしくはAlxGa1−xN、もしくはそれらの多層膜である窒化物半導体素子構造とする。

(もっと読む)

半導体装置及びその製造方法

【課題】炭化珪素層に対する良好なコンタクトを確保しつつ、炭化珪素層に接続された電極の剥離を抑制する。

【解決手段】炭化珪素層11を有する半導体装置の製造方法であって、(A)炭化珪素層11の上に導電層21を形成する工程と、(B)導電層21と炭化珪素層11を反応させて、炭化珪素層11に接する反応層12およびシリサイド層23からなる合金層を形成する工程と、(C)シリサイド層23の少なくとも一部を除去することにより、反応層12の表面の少なくとも一部を露出させる工程と、露出させた反応層12の表面上に電極層13を形成する工程とを含む。

(もっと読む)

3−5族化合物半導体とその製造方法および半導体素子

【課題】埋め込み構造作製のための再成長において、速やかに再成長表面が平坦な構造となり、薄層の3-5族化合物半導体を製造する方法を提供する。

【解決手段】一般式InuGavAlwN(0≦u≦1、0≦v≦1、0≦w≦1、u+v+w=1)で表される第1の3−5族化合物半導体からなる層の上に、後記の第2の3−5族化合物半導体の成長条件においても安定な絶縁性材料または金属材料からなるパターンを有し、該第1の3−5族化合物半導体と該パターンの上に、一般式InxGayAlzN(0≦x≦1、0≦y≦1、0≦z≦1、x+y+z=1)で表される第2の3−5族化合物半導体からなる層を有する3−5族化合物半導体において、該絶縁性材料または金属材料がSiO2、SiNx、タングステンのいずれかの材料であり、該パターンが第1の3−5族化合物半導体の[1-100]方向に概ね平行なラインパターンであり、該ラインパターンの幅が1μm以下であることを特徴とする3−5族化合物半導体。

(もっと読む)

半導体デバイス用の改良型誘電体パシベーション

半導体デバイスは、少なくとも1つの表面を含むIII族窒化物半導体材料の層と、半導体材料の電気的応答を制御するための、表面上にある制御コンタクトと、制御コンタクトに隣接する1つの表面の少なくとも一部を被覆する誘電体バリア層であって、III族窒化物のバンドギャップよりも大きなバンドギャップと、III族窒化物の導電帯からずれている導電帯とを有する、誘電体バリア層と、III族窒化物の表面の残り部分を被覆する誘電体保護層とを備えている。  (もっと読む)

(もっと読む)

複数のフィールドプレートを有するワイドバンドギャップトランジスタ

ソース電極およびドレイン電極が半導体層に接触した、基板上の複数の活性半導体層を備えるトランジスタ。ゲートが、ソース電極とドレイン電極との間に、複数の半導体層上に形成される。複数のフィールドプレートが、半導体層上に配置され、各フィールドプレートは、ゲートのエッジからドレイン電極に向かって延び、また各フィールドプレートは、前記半導体層から、また他のフィールドプレートから分離される。最上部のフィールドプレートは、ソース電極に電気的に接続され、他のフィールドプレートは、ゲートまたはソース電極に電気的に接続される。  (もっと読む)

(もっと読む)

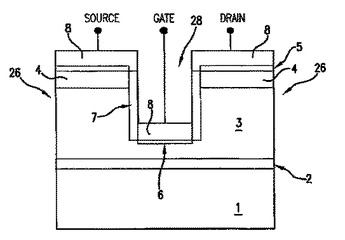

高圧接合型電界効果トランジスタ

本発明は、第2の導電型基板(10)内の第1の導電型の第1のウエル(11)と、前記第1のウエル内のそれぞれ第1の導電型からなるソース(14)及びドレイン(15)と、第2の導電型からなる第2のウエル(12)内に配設されている第2の導電型のゲート(16)とを有している高圧接合型電界効果トランジスタに関しており、前記第2のウエルは逆行性のタイプからなり、さらにソース、ゲート、ドレインの素子がフィールド酸化膜領域(13a〜13d)によって相互に離間されていることを特徴としている。またゲート(16)からソース及びドレイン領域の方向にフィールドプレート(17a,17b)がフィールド酸化膜(13a,13b)の上方で延在している。  (もっと読む)

(もっと読む)

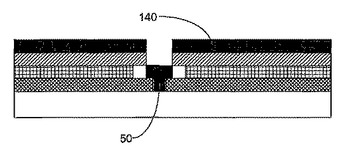

自己整列型炭化ケイ素半導体デバイスおよびそのデバイスの作成方法

電流安定性の改善された自己整列型炭化ケイ素パワーMESFETおよびそのデバイスの作成方法を記載する。このデバイスは、ゲート凹部により分離されたレイズドソースおよびドレイン領域を含み、低ゲートバイアスにおいてでさえ表面トラップ効果が低減されるため、電流安定性が改善される。このデバイスは自己整列型プロセスを用いて作成され得る。このプロセスでは、金属エッチマスクを用いて、nドープのSiCチャネル層上のn+ドープのSiC層を備えた基板がエッチングされてレイズドソースおよびドレイン領域が規定される。この金属エッチマスクがアニールされ、ソースおよびドレイン・オームコンタクトが形成される。単層または多層の誘電性フィルムが成長または堆積され異方性エッチングされる。蒸着または別の異方性堆積技術を用いて、ショットキーコンタクト層および最終金属層が堆積され、オプションとして、誘電性層の等方エッチングされる。  (もっと読む)

(もっと読む)

デバイス製造方法および基板

電磁放射線を用いた一回の露光プロセスでT−ゲートを製造する方法が開示される。  (もっと読む)

(もっと読む)

保護層および低損傷陥凹部を備える窒化物ベースのトランジスタならびにその製作方法

窒化物ベースの半導体チャネル層上に窒化物ベースの半導体バリア層を形成すること、および窒化物ベースの半導体バリア層のゲート領域上に保護層を形成することによって、トランジスタが製作される。パターニングされたオーム性接触金属領域が、バリア層上に形成され、第1および第2のオーム性接触を形成するためにアニールされる。アニールは、保護層をゲート領域上に載せたままで実施される。バリア層のゲート領域上に、ゲート接点も形成される。ゲート領域内に保護層を有するトランジスタも形成され、バリア層の成長させたままのシート抵抗と実質的に同じシート抵抗をもつバリア層を有するトランジスタも同様である。  (もっと読む)

(もっと読む)

炭化珪素半導体素子及びその製造方法

半導体素子の製造方法は、炭化珪素基板1上に形成された炭化珪素薄膜2内にイオンを注入する工程と、炭化珪素基板を減圧雰囲気で加熱することで炭化珪素基板の表面にカーボン層5を形成する工程と、カーボン層5を形成する工程より高い圧力で、且つ高い温度の雰囲気中で炭化珪素基板を活性化アニールする工程とを含んでいる。 (もっと読む)

III族窒化物素子の不動態化およびその方法

【課題】

【解決手段】III族窒化物半導体素子およびその製造方法の実施形態は、高温処理中にIII族窒化物材料に損傷を与えずに、素子のコンタクトを形成することを可能にする低抵抗の不動態化層を備えてよい。不動態化層は、素子全体を不動態化するために用いられてよい。不動態化層は、さらに、素子のコンタクトと活性層との間に設けられて、導電のための低抵抗の電流路を提供してもよい。この不動態化処理は、FET、整流器、ショットキダイオードなど、任意の種類の素子に用いて、破壊電圧を改善すると共に、コンタクトの接合部付近の電界集中効果を防止してよい。不動態化層は、外部拡散に関してIII族窒化物素子に影響を与えない低温アニールで活性化されてよい。

(もっと読む)

電極、その製造方法およびそれを用いた半導体素子

低接触抵抗を実現しつつ表面荒れの少ない電極が得られる技術を提供する。

半導体膜101の上部に設けられる電極であって、この半導体膜101の上部にこの半導体膜の側から順に積層された第一金属層102と第二金属層103とを有し、この第一金属膜102が、Alからなり、この第二金属膜103が、Nb、W、Fe、Hf、Re、TaおよびZrからなる群より選ばれる1種以上の金属からなることを特徴とする電極。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長の短いゲート電極を有し、しかも低抵抗で高周波特性が優れている半導体装置およびその製造方法を提供する。

【解決手段】少なくともノンドープInGaP層又はノンドープInAlGaP層からなる上層半導体層12と、この上層半導体層直下にGaAs層またはAlGaAs層からなる下層半導体層11を含む半導体基板に、上層半導体層表面から上層半導体層への浸入が、下層半導体層で略停止するショットキーゲート電極15と、このショットキーゲート電極部に接続して第1の電極の抵抗を低減する第2の電極部16からなるT字型ゲート電極を形成する。

(もっと読む)

窒化物系III―V族化合物半導体装置の電極構造

【課題】 半導体上の膜付着力が強く、かつ温度特性が優れたショットキー電極を備えた窒化物系III−V族化合物半導体装置の電極構造を提供する。

【解決手段】 この窒化物系III−V族化合物半導体装置の電極構造は、電極4の材料として金属窒化物(窒化タングステン)を用いたので、半導体GaN層3への膜付着力が強く、かつ、加熱によってショットキー特性が劣化することがないショットキー電極4を得ることができた。

(もっと読む)

ヘテロ接合型電界効果トランジスタ

【課題】耐圧性、特性安定性に優れ、ゲートリーク電流が低減されたヘテロ接合型電界効果トランジスタを提供すること。

【解決手段】半導体基板上にバッファ層と、チャネル層と、スペーサ層と、キャリア供給層と、ショットキーバリア層と、高濃度不純物ドープキャップ層とが順次堆積され、ソース電極及びドレイン電極がキャップ層表面に形成され、ソース電極とドレイン電極の間のキャップ層にショットキーバリア層に達する開口部が形成され、開口部に露出したショットキーバリア層表面にゲート電極が形成されているヘテロ接合型電界効果トランジスタであって、キャップ層が複数の細線で構成され、細線間はショットキーバリア層が露出し、ソース電極及びドレイン電極が、細線と細線間に露出したショットキーバリア層との両方に接触していることを特徴とするヘテロ接合型電界効果トランジスタを構成する。

(もっと読む)

541 - 560 / 560

[ Back to top ]