Fターム[5F102HC11]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | 蒸着、スパッタ (562)

Fターム[5F102HC11]の下位に属するFターム

斜め方向からの蒸着 (2)

蒸着の際に段切れを利用するもの

Fターム[5F102HC11]に分類される特許

101 - 120 / 560

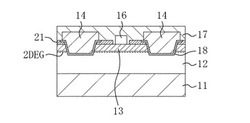

半導体装置

【課題】コンタクト抵抗が小さいオーミック電極を備えたIII−V族窒化物半導体を用いた半導体装置を実現できるようにする。

【解決手段】半導体装置は、基板11の上に順次形成された、第1のIII−V族窒化物半導体層12及び第1のIII−V族窒化物半導体12と比べてバンドギャップが大きい第2のIII−V族窒化物半導体層13と、p型の導電型を有する第3のIII−V族窒化物半導体層21と、第1のオーミック電極14とを備えている。第1のオーミック電極14は、下部が第2のIII−V族窒化物半導体層13及び第3のIII−V族窒化物半導体層21を貫通し且つ第1のIII−V族窒化物半導体層12における2次元電子ガス層よりも下側の領域に達するように形成されている。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法、および半導体装置の動作方法

【課題】電界集中を緩和し、高い耐圧を得ることが可能な半導体装置を提供する。

【解決手段】

半導体層上において、第1フィールドプレートFAは、第1絶縁膜上に、第1電極102と第2電極103との間に相互に間隔を置いて配置され、第2フィールドプレートFBは、第2絶縁膜上に、第1電極102上方から第2電極103上方までの間に相互に間隔を置いて配置され、

第1電極および第2電極側末端のFBは、第1電極または第2電極およびそれに隣り合うFAに重なり、

前記第1電極および第2電極側末端FB以外の一方のFAまたはFBは、第1電極から第2電極への方向と垂直方向に隣り合う複数の他方のFAまたはFBに重なり合い、前記第1電極および第2電極側末端FB以外の他方のFAまたはFBは、第1電極から第2電極への方向に隣り合う2つの前記一方のFAまたはFBに重なり合う半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのショットキーダイオード10は、半導体からなる基板11と、基板11上に形成されたn型層12とを備えている。n型層12は基板11側の表面である第1の面12Aとは反対側の表面である第2の面12Bから第1の面12Aに向けて延びるように形成された溝13を有している。溝13の底部である底壁13Aに接触する位置には絶縁体としての酸化物層14が配置されており、かつ溝13の側壁13Bに接触するようにn型層12とショットキー接触可能な金属膜15が溝13を埋めるように形成されている。さらに、n型層12の第2の面12Bに接触するようにアノード電極16が配置されている。

(もっと読む)

テラヘルツ波受信素子

【課題】テラヘルツ波を効率よく受信し、信号/雑音比を向上したテラヘルツ波受信素子を提供する。

【解決手段】第1の波長λ1のテラヘルツ波を受信するテラヘルツ波受信素子100であ

って、2以上の半導体層(バッファ層102aおよび電子供給層104a)のヘテロ接合により形成される2次元電子チャネル層103a、ゲート幅方向にλ1/2の長さを有するゲート電極111a、ドレイン電極113aおよびソース電極112aを有する第1のFET100aと、第1のFET100aのゲート電極111aのゲート幅方向における中央部と接続され、かつ、ゲート電極111aと直交するように配置されたゲート配線114aとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系HEMT及びMIMキャパシタを同一基板上に設ける場合でも小型化することができる半導体装置及びその製造方法を提供する。

【解決手段】基板1の表面上に下部電極11を形成し、下部電極11上に誘電体膜12を形成し、誘電体膜12上に基板1の表面に接する上部電極14aを形成する。また、基板1の裏面から基板1をエッチングすることにより、上部電極14aの基板1の表面に接する部分に達するビアホール1aを基板1に形成し、基板1の裏面上にビアホール1aを介して上部電極14aに接するビア配線36を形成する。

(もっと読む)

電子回路装置

【課題】ノーマリオフ型の炭化珪素接合FETはゲートの特性が、使い勝手が悪いという問題がある。これは、ノーマリオフを実現するためにゲート電圧が0Vでオフしていなければならず、かつ、ゲート・ソース間のpn接合に電流が流れないようにオン状態としてはゲート電圧を2.5V程度に抑える必要があるため、実質的にゲート電圧を0Vから2.5Vの間で制御しなければならないためである。従って、閾値電圧からオン状態のゲート電圧までが1Vから2V程度しかなく、ドレイン電流がゲート電圧の変化に非常に敏感であるため、ゲートの制御が難しい。

【解決手段】本願発明は、ノーマリオフ型の炭化珪素接合FETのゲートに、接合FETのゲート容量と同等か少し小さな容量を持つ素子を接続したものである。

(もっと読む)

高周波半導体装置

【課題】小型かつ高性能な半導体装置を提供すること。

【解決手段】第1のGaAs層11、およびこのGaAs層11に対して水平方向が長手方向となるように形成された四角柱状の第2のGaAs層12と、第1、第2のGaAs層11、12の表面に形成されたAlGaAs層13と、第1のGaAs層11の裏面に形成されたドレインパッド14と、第2のGaAs層12上のAlGaAs層13の表面に形成された帯状のソースパッド16と、第1のGaAs層11上のAlGaAs層13上のうち、第2のGaAs層12の両側に形成された帯状のゲートパッド15と、を具備し、第1のGaAs層11の厚さは、第2のGaAs層12のうち、両側にゲートパッド15が形成された領域(ゲート領域18)を除く部分の厚さよりも厚く形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】簡便に半導体集積回路を小領域に電気的に分離する。

【解決手段】厚さが150〜600μm程度のInP基板、GaAs基板等の化合物半導体基板1の表面に半導体集積回路2を形成し、化合物半導体基板1の裏面(半導体集積回路2が形成された表面とは反対側の面)に、直角に交わっている複数の切込溝3を設け、半導体集積回路2の表面から切込溝3の底面までの距離を50〜150μmとし、切込溝3内にAu等の金属4を埋め込み、金属4を化合物半導体基板1の裏面全面にも設ける。

(もっと読む)

はんだ濡れ性の前面金属部を備えるIII族窒化物パワーデバイス

【課題】外部回路接続に棒はんだを用いる、複数の相互接続金属層およびはんだ濡れ性の前面金属部構造を備えるHEMTを含むIII族窒化物パワーデバイスの、いくつかの典型的な実施形態を提供する。

【解決手段】はんだ濡れ性の前面金属部140aおよび140bの構成は、TiNiAgのようなトリメタルからなり、HEMTのソースおよびドレインコンタクトを交互の細長いデジットまたはバーとして露出するように設けられる。また、単一のパッケージは、前面金属部構造140aおよび140bが交互の相互嵌合したソースおよびドレインコンタクトを露出する、こうしたHEMTを多数集積し、これはIII族窒化物デバイスを用いるDC‐DCパワー変換回路設計に有利となり得る。外部回路接続に棒はんだを用いることにより、横方向の導電が可能となり、これによりデバイスのオン抵抗Rdsonを低減する。

(もっと読む)

電子デバイス及びオーミック電極形成方法

【課題】製造工程において高温で短時間のアニールを可能にすることにより、イオン注入の工程が不要なAlxGa1−xN/AlyGa1−yNヘテロ接合のオーミック電極を備える電子デバイスを提供する。

【解決手段】

電子デバイスは、ワイドバンドギャップ化合物半導体層と、前記ワイドバンドギャップ化合物半導体層上に形成されるオーミック電極とを含む電子デバイスであって、前記ワイドバンドギャップ化合物半導体層は、IniAljGakN(i+j+k=1,0≦i≦1,0<j≦1,0≦k<1)からなる化合物半導体バリア層とAlyGa1−yN(0<y≦1)からなる化合物半導体チャネル層からなり、前記オーミック電極は、前記化合物半導体バリア層上に密着層が積層され、前記密着層上にオーミック層が積層されて形成された電極であり、前記密着層はZrからなるようにする。

(もっと読む)

ヘテロ接合型電界効果トランジスタ

【課題】HFETの種々の特性を改善する。

【解決手段】ヘテロ接合型電界効果トランジスタでは、サファイア基板の上面上において第1の金属層(2)とヘテロ接合を含む窒化物半導体層(5、6)とがこの順に形成されており、窒化物半導体層上にはソース電極(7)、ゲート電極(8)およびドレイン電極(9)が配置されており、第1の金属層は開口部(4)を含むようにパターン化されており、窒化物半導体層は第1の金属層の開口部で露出されたサファイア基板の上面から結晶成長しており、第1の金属層はソース電極へ電気的に接続されていることを特徴としている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体装置のソース電極、ドレイン電極及びゲート電極を形成するいずれの領域においても、残渣のない良好な半導体/金属界面が得られるようにする。

【解決手段】化合物半導体装置の製造方法を、基板1上に化合物半導体積層構造4を形成する工程と、化合物半導体積層構造上に金属膜5A〜5Cを形成する工程と、金属膜上にソース電極7及びドレイン電極8を形成する工程と、金属膜の一部を酸化又は窒化して、金属酸化物膜又は金属窒化物膜5CXを形成する工程と、金属酸化物膜又は金属窒化物膜上にゲート電極9を形成する工程とを含むものとする。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】デバイス特性を維持し、ゲートリーク電流を低減できる電界効果トランジスタ及びその製造方法を提供する。

【解決手段】本発明に係る電界効果トランジスタ100は、III−V族窒化物半導体層構造と、半導体層構造上に離間して形成されたソース電極105及びドレイン電極106と、ソース電極105及びドレイン電極106の間に形成されたゲート電極108と、ソース電極105上及びドレイン電極106上に形成された電極保護膜107と、半導体層構造上に、ソース電極105、ドレイン電極106、ゲート電極108及び電極保護膜107の上面の少なくとも一部を覆うように形成され、半導体層構造を保護する第1のパッシベーション膜109を備え、第1のパッシベーション膜109は、所定の材料に対して化学的に活性であり、電極保護膜107は、所定の材料に対して化学的に不活性な金属である。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプスが抑制された窒化物半導体を用いた電界効果トランジスタを容易に実現できるようにする。

【解決手段】電界効果トランジスタは、基板100の上に形成され、第1の窒化物半導体層122及び第2の窒化物半導体層123を有する半導体層積層体102を備えている。半導体層積層体102の上には、互いに間隔をおいてソース電極131及びドレイン電極132が形成されている。ソース電極131とドレイン電極132との間には、ソース電極131及びドレイン電極132と間隔をおいてゲート電極133が形成されている。ドレイン電極132の近傍には正孔注入部141が形成されている。正孔注入部141は、p型の第3の窒化物半導体層142及び第3の窒化物半導体層142の上に形成された正孔注入電極143を有している。ドレイン電極132と正孔注入電極142とは、電位が実質的に等しい。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】ダイヤモンド薄膜内に存在する結晶欠陥、不純物等を減少させ、高品質なダイヤモンド薄膜を作製可能なダイヤモンド薄膜作製方法を提供すること。

【解決手段】ダイヤモンドが安定な高圧力下でアニールを行う。これにより、結晶中に含まれる格子欠陥等が回復、除去され、ダイヤモンド結晶薄膜を高品質化する事ができる。「(ダイヤモンドが)安定な、安定に」とは、ダイヤモンドがグラファイト化せずにダイヤモンドの状態を保つ状態を指す。ダイヤモンドが安定にアニール出来る領域内でアニールを行う温度(アニール温度、とも呼ぶ)Tおよびアニールを行う圧力(アニール圧力、とも呼ぶ)Pが決定される。この領域は、図21に示される、P>0.71+0.0027TまたはP=0.71+0.0027Tを満たし、なおかつP≧1.5GPaの領域である。このような領域は、図21中の斜線部分である。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】ノーマリオフ特性が安定的に得られる窒化物半導体装置を提供すること。

【解決手段】基板1と、基板1上に形成され、且つ、ヘテロ接合界面22aを有する窒化物半導体層2と、窒化物半導体層2に形成されたリセス3と、を備える窒化物半導体装置であって、

窒化物半導体層2は、基板1上に形成されたAlx1Inx2Ga1−x1−x2N(0≦x1<1、0≦x2≦1、0≦(x1+x2)≦1)からなるキャリア走行層22と、キャリア走行層22上に形成されたAlyGa1−yN(0<y≦1、x1<y)からなる第1の層231、第1の層231上に形成されたGaNからなる第2の層232、及び、第2の層上に形成されたAlzGa1−zN(0<z≦1、x1<z)からなる第3の層233を有するキャリア供給層23と、を備え、

凹部3は、第3の層233を貫通し、凹部底面31において第2の層232の主面が露出するように形成される。

(もっと読む)

化合物半導体装置の製造方法及び化合物半導体装置

【課題】工程増を最小限とした簡便な手法で、基板に反りを生ぜしめることなく、また基板上方の化合物半導体層の結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い装置構成を得る。

【解決手段】SiC基板1上の素子分離領域に相当する部位にマスク2を形成し、マスク2を覆うようにSiC基板1上に緩衝層3を第1の温度で形成し、第1の温度より高い第2の温度で加熱処理して緩衝層3のうちSiC基板1上の部位を結晶化し、緩衝層3の上方に化合物半導体層10を形成して、化合物半導体層10のマスク2の上方に相当する部位を素子分離領域とする。

(もっと読む)

半導体装置、半導体ウェハ、半導体装置の製造方法及び半導体ウェハの製造方法

【課題】ダイシング工程における半導体装置の歩留低下が抑制できる半導体ウェハ及び半導体装置を安価に提供することを目的とする。

【解決手段】基板1と、前記基板1上に形成され且つ素子形成領域2を有する化合物半導体層3と、前記素子形成領域2に形成された少なくとも1つの半導体素子と、を備える半導体装置であって、前記化合物半導体層3が、前記基板1上において選択的に形成された低結晶膜31と、前記基板1上に隣接して形成され且つ前記素子形成領域2を有する第1の化合物成長層32と、平面的に見て前記素子形成領域2を包囲するように前記低結晶膜31上に隣接して形成され且つ前記第1の化合物成長層32よりも低い結晶性を有する第2の化合物成長層33と、を備えることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】炭化珪素基板を用いた接合型FETにおいて、ゲート・ソース間のpn接合領域において生じるリーク電流を低減する。

【解決手段】炭化珪素基板を用いたトレンチ型接合FETにおいて、トレンチ5の側壁および底面に窒素を導入することにより、トレンチ5の表面にn型層8およびn+型層9を形成する。これによりp+型ゲート領域4とn+型ソース領域3との接合領域であるpn接合領域はダメージの多いトレンチ5の側壁ではなく半導体基板21の主面において露出し、また、その露出する領域は狭まるため、pn接合領域におけるリーク電流を低減することができる。

(もっと読む)

101 - 120 / 560

[ Back to top ]