Fターム[5F110AA01]の内容

Fターム[5F110AA01]の下位に属するFターム

寄生容量低減 (412)

電極、配線の低抵抗化 (732)

Fターム[5F110AA01]に分類される特許

2,001 - 2,020 / 2,473

薄膜トランジスタ及びゲート絶縁膜

【課題】ゲート絶縁膜のコストを低減、製造工程の簡略化を図り、移動度及びオンオフ電流比の高い性能に優れた薄膜トランジスタを提供する。

【解決手段】基板上に、ゲート電極及びゲート絶縁膜が形成されている薄膜トランジスタであって、上記ゲート絶縁膜が、下記の一般式(1)で表わされる構造を有し、R11〜R1nの内少なくとも1つがHである少なくとも1種のシリコン含有ポリマー(A1)と、活性光線もしくは放射線の照射により、酸または塩基を発生する化合物とを含むシリコン含有感光性組成物を用いて形成される。 (もっと読む)

(もっと読む)

pチャネル型薄膜トランジスタ、pチャネル型薄膜トランジスタの製造方法および表示装置

【課題】より高い電子(又は正孔)の移動度を有するTFTを製造することができる薄膜トランジスタ、薄膜トランジスタの製造方法、表示装置を提供すること。

【解決手段】横方向に結晶成長された半導体薄膜4aにソース領域S、チャネル領域C、およびドレイン領域Dを有し、前記チャネル領域C上部にゲート絶縁膜11およびゲート電極12を有する薄膜トランジスタ1であって、前記ドレイン領域Dの前記チャネル領域C側のドレイン端10は前記結晶成長の終了位置8付近に位置するように形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース電極、ドレイン電極の高さを低減して、ソース電極、ドレイン電極との接触領域でチャネル層を形成するもので、導体もしくは半導体からなる微粒子とこの微粒子と結合した有機半導体分子とによって形成される層が断切れを生じさせないようにして、トランジスタ特性の向上を図る。

【解決手段】基体11上に電極(ソース電極、ドレイン電極)15を有し、電極15上および電極15上間の前記基体11上に導体もしくは半導体からなる微粒子とこの微粒子と結合した有機半導体分子とによって形成された導電膜を備えた半導体装置であって、電極(ソース電極、ドレイン電極)15の基体11上の厚さは、電極(ソース電極、ドレイン電極)15が電極として使用できる抵抗率以下となる厚さ以上、25nm以下である。

(もっと読む)

pチャネル型薄膜トランジスタ、pチャネル型薄膜トランジスタの製造方法および表示装置

【課題】より高い電子(又は正孔)の移動度を有するTFTを製造することができる薄膜トランジスタ、薄膜トランジスタの製造方法、表示装置を提供すること。

【解決手段】横方向に結晶成長された半導体薄膜4aにソース領域S、チャネル領域C、およびドレイン領域Dを有し、前記チャネル領域C上部にゲート絶縁膜11およびゲート電極12を有する薄膜トランジスタ1であって、前記ドレイン領域Dの前記チャネル領域C側のドレイン端10は前記結晶成長の終了位置8付近に位置するように形成する。

(もっと読む)

平板表示装置及びその製造方法

【課題】薄膜トランジスタの特性が向上した平板表示装置及びその製造方法を提供する。

【解決手段】本発明の平板表示装置は、絶縁基板;絶縁基板上に離隔して形成されてチャネル領域を規定するソース電極及びドレイン電極;電極それぞれの少なくとも一領域とチャネル領域上に形成されている有機半導体層;有機半導体層と電極との間に位置し、電極と有機半導体層との間の接触抵抗を減少させる自己組立単層膜を含むことを特徴とする。平板表示装置の製造方法は、絶縁基板を準備し;前記絶縁基板上に離隔して形成されてチャネル領域を規定するソース電極及びドレイン電極を形成し;前記ソース電極と前記ドレイン電極上に自己組立単層膜物質を加え、前記ソース電極及び前記ドレイン電極と化学的に結合する自己組立単層膜を形成し;前記自己組立単層膜の少なくとも一領域と前記チャネル領域に有機半導体層を形成する工程を含むことを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 電界効果型トランジスタが形成される半導体層の結晶性の劣化を抑制しつつ、電界効果型トランジスタが形成される半導体層下にバックゲート電極を配置し、電界効果型トランジスタの高速化と低消費電力化の両立を図る。

【解決手段】 バックゲート電極3には膜厚が互いに異なる部分を設け、バックゲート電極3の膜厚の厚い部分に対応して、埋め込み絶縁層2を厚膜化するとともに、バックゲート電極3の膜厚の薄い部分に対応して、埋め込み絶縁層2を薄膜化し、半導体層4に形成されるチャネル領域は、薄膜化された埋め込み絶縁層2上にくるように配置するとともに、半導体層4に形成されたソース層8aおよびドレイン層8bは厚膜化された埋め込み絶縁層2上にくるように配置する。

(もっと読む)

nチャネル型薄膜トランジスタ、nチャネル型薄膜トランジスタの製造方法および表示装置

【課題】より高い電子(又は正孔)の移動度を有するTFTを製造することができる薄膜トランジスタ、薄膜トランジスタの製造方法、表示装置を提供すること。

【解決手段】横方向に結晶成長された半導体薄膜4aにソース領域S、チャネル領域C、およびドレイン領域Dを有し、前記チャネル領域C上部にゲート絶縁膜11およびゲート電極12を有する薄膜トランジスタ1であって、前記ドレイン領域Dの前記チャネル領域C側のドレイン端10は前記結晶成長の終了位置8付近に位置するように形成する。

(もっと読む)

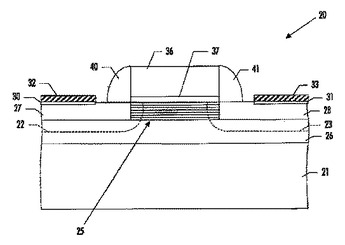

応力MOSデバイスの製造方法

応力がかけられたMOSデバイス(30)を製造する方法が提供されている。該方法は、半導体基板(36)とその上に複数の並列のMOSトランジスタを形成するステップを含む。この並列のMOSトランジスタは、共通のソース(92)領域、共通のドレイン(94)領域、および共通のゲート電極(66)を有する。第1トレンチ(82)は、共通のソース(92)領域の基板にエッチングされ、第2トレンチ(84)は共通のドレイン(94)領域の基板にエッチングされる。結晶格子が半導体基板と一致しない応力誘起半導体材料(90)は、第1トレンチ(82)および第2トレンチ(84)に選択的に成長される。応力誘起材料(90)が成長することで、PチャネルMOSトランジスタの駆動電流を増加するMOSデバイスチャネル(50)に圧縮した縦方向の応力と横方向の引張応力の両方が生じる。圧縮した応力コンポーネントがもたらすNチャネルMOSトランジスタの駆動電流の減少は、引張応力コンポーネントによってオフセットされる。  (もっと読む)

(もっと読む)

薄膜トランジスタとその製造方法、及び表示装置

【課題】 高く安定したトランジスタ特性を有する薄膜トランジスタを提供する。

【解決手段】 ソース領域12及びドレイン領域13のいずれか一方のみに対応して、ゲート絶縁層に比して高い熱伝導率を有する伝熱部材3aが、ゲート電極3に少なくとも熱的に連結して設けられた構成とする。

(もっと読む)

薄膜トランジスター基板と薄膜トランジスター基板の製造方法

【課題】薄膜トランジスターの特性が向上した薄膜トランジスター基板を提供する。

【解決手段】薄膜トランジスター基板は、絶縁基板と、絶縁基板上に形成されているゲート配線と、ゲート配線上に形成されていて、ゲート配線の少なくとも一部を露出させる第1絶縁膜接触口が形成されている無機物質の第1ゲート絶縁膜と、第1ゲート絶縁膜上に形成されていて、第1絶縁膜接触口に対応する第2絶縁膜接触口が形成されている有機物質の第2ゲート絶縁膜と、第2ゲート絶縁膜上にチャネル領域を定義するために互いに離間して形成されるソース電極及びドレイン電極と、チャネル領域に形成されている有機半導体層とを含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 電界効果型トランジスタが形成される半導体層の支持強度を向上させつつ、半導体層下にエアギャップ層を形成する。

【解決手段】 半導体基板1上にエアギャップ層3を介して半導体層5を形成し、半導体基板1上で半導体層5を支持する支持体9をエアギャップ層3の側面に接するように形成し、支持体9は半導体層5の側壁を介して半導体層5下に回り込むように配置する。

(もっと読む)

直接チャネル応力

【課題】移動度の向上したMOSトランジスタを提供する。

【解決手段】半導体装置に伸張性のチャネル領域を形成する工程を包含する。一形態において、製造の中間段階において半導体装置のアモルファス部分を覆う応力層を歪ませる工程を包含する。上記半導体装置はマスクされており、応力層の一部における歪みは緩和される。製造途中の半導体装置のアモルファス部分を再結晶化することによって、応力層からの歪みを基板に伝達する。歪みの少なくとも一部は、装置の製造工程の間、基板に残存する。その結果、完成した装置の性能を向上させることができる。他の形態において、伸張性の応力層は、上記装置の第1部分を覆うよう形成され、圧縮性の応力層は、上記装置の第2部分を覆うよう形成される。伸張性の応力層は、PMOS装置において圧縮性のチャネルを形成し、圧縮性の応力層は、NMOS装置において伸張性のチャネルを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 セルフヒート効果を低減することができ、基板浮遊効果も解消できるようにした半導体装置及びその製造方法を提供する。

【解決手段】 Si基板1上のSi層10にゲート酸化膜21を介して形成されたゲート電極23と、ゲート電極23を挟んでSi層10に形成されたソース層27a及びドレイン層27bと、を含んで構成されるSDONトランジスタ100を有し、ソース層27aとSi基板1との間及び、ドレイン層27bとSi基板1との間にはそれぞれ空洞部15が存在し、且つゲート電極23下のSi層10とSi基板1との間には空洞部が存在していないことを特徴とするものである。ゲート電極23下のSi層10がSi基板1とつながっているので、SONトランジスタと比べて、セルフヒート効果を低減することが可能である。また、ボディ電位はSi基板1に固定されるので、基板浮遊効果を解消することができる。

(もっと読む)

有機半導体材料、有機半導体膜、有機半導体デバイス及び有機薄膜トランジスタ

【課題】 簡単なプロセスで製造され、トランジスタとしての特性が良好であり、さらに経時劣化が抑えられた有機半導体材料、それを用いた有機半導体膜、有機半導体デバイス及び有機薄膜トランジスタを提供することである。

【解決手段】 シクロファン化合物を含有することを特徴とする有機半導体材料。

(もっと読む)

代替活性エリア材料の集積回路への組み込みのための解決策

結晶半導体基板上に代替材料のエリアを形成する方法、並びにこの方法により形成された構造。このような代替材料のエリアは、MOSFET又は電子デバイス若しくは光電子デバイスにおける活性エリアとしての使用に適している。  (もっと読む)

(もっと読む)

半導体装置

【課題】 CMOS回路における動作速度を同じくするためには、そのキャリア移動度の違いから、p型MOSトランジスタとn型MOSトランジスタの面積を異ならせる必要がある。この面積のアンバランスにより半導体装置の集積度向上が妨げられていた。

【解決手段】 SOI基板上に設けた半導体層(SOI層)と、前記SOI層上に設けられたゲート電極とを備え、前記ゲート電極と前記SOI層の仕事関数差による空乏層の厚さが前記SOI層の膜厚より大きくなるように、前記SOI層の膜厚を設定してノーマリオフとしたMOSトランジスタを少なくとも一種類、備える。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル層に応力が付加され、かつ高信頼なMOSFETを実現する。

【解決手段】半導体基板と、前記半導体基板の表面に対向して設けられ、単結晶または多結晶構造を有する一対のソース・ドレイン電極と、前記ソース・ドレイン電極の間の前記半導体基板の表面に形成された単結晶チャネル領域と、前記チャネル領域上にゲート絶縁膜を介して形成されたゲート電極と、前記ソース・ドレイン電極の上部に形成された金属化合物層と、前記ソース・ドレイン電極の下部に位置し、前記ソース・ドレイン電極を構成する物質の固有の格子間隔とは異なる格子間隔を保持した結晶構造を有する応力付与層と、前記応力付与層の下部に位置する第1の絶縁層とを具備する。

(もっと読む)

ドミノCMOS論理回路

【課題】 ドミノCMOS論理回路の動作速度を向上させる。

【解決手段】 プリチャージ動作時にオン状態となって内部ノードN1を電源電位VDDに充電するPMOS1と、論理動作時にオン状態となって内部ノードN2を接地電位GNDに接続するNMOS2と、複数の入力信号INa,INbに従って内部ノードN1,N2間をオン/オフ制御する論理回路網10Aと、この内部ノードN1のレベルを反転して出力信号OUTを出力するインバータ3Aを備えたドミノCMOS論理回路において、論理回路網10Aを複数のDMOS11d,12dで構成し、インバータ3AをNMOS3nとPDMOS3dで構成すると共に、回路全体をSOI基板上に形成する。

(もっと読む)

有機半導体材料、有機半導体膜、有機半導体デバイス及び有機薄膜トランジスタ

【課題】トランジスタとしての特性が良好であり、さらに経時劣化が抑えられた有機半導体材料、それを用いた有機半導体膜、有機半導体デバイス及び有機薄膜トランジスタを提供する。

【解決手段】下記一般式(1)で表される化合物を含有することを特徴とする有機半導体材料。 一般式(1) A1−L1−(A2)n[式中、A1、A2は、各々3環以上が縮合した、芳香族炭化水素環または芳香族複素環から導出される基を表し、L1は、アルキレン基、シクロアルキレン基、オキシアルキレン基、チオアルキレン基、アルキルイミノ基及びシロキサン結合を有する基からなる連結基群から選択される少なくとも一つを有する、(n+1)価の連結基を表し、nは1〜3の整数を表す。]

(もっと読む)

非半導体モノレイヤーを有するチャネルを含む半導体デバイス、及びその製造方法

半導体デバイスは、半導体基板及びその上の少なくとも1つのMOSFETを含んでいる。このMOSFETは、空間的に隔てられたソース領域及びドレイン領域、ソース領域とドレイン領域との間のチャネル、及びチャネルの上に位置しチャネルとの界面を画成するゲートを含んでいる。ゲートは、チャネルの上に位置するゲート誘電体と、ゲート誘電体の上に位置するゲート電極とを含んでいる。また、このチャネルは、積層された複数のベース半導体モノレイヤーと、隣接し合うベース半導体モノレイヤーの結晶格子内に拘束された少なくとも1つの非半導体モノレイヤーとを含んでいる。上記少なくとも1つの非半導体モノレイヤーは、チャネルとゲート誘電体との間の界面に対しておよそ4−100モノレイヤーの深さに位置付けられている。  (もっと読む)

(もっと読む)

2,001 - 2,020 / 2,473

[ Back to top ]