Fターム[5F110AA01]の内容

Fターム[5F110AA01]の下位に属するFターム

寄生容量低減 (412)

電極、配線の低抵抗化 (732)

Fターム[5F110AA01]に分類される特許

2,461 - 2,473 / 2,473

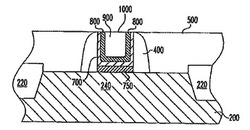

集積回路のトランジスタにおける金属ゲート構造および形成方法(高性能デバイスの金属置換ゲートのための構造および方法)

【課題】 高性能デバイスの金属置換ゲートのための構造および形成方法を提供する。

【解決手段】 まず、半導体基板(240)上に設けたエッチ・ストップ層(250)上に、犠牲ゲート構造(260)を形成する。犠牲ゲート構造(300)の側壁上に、1対のスペーサ(400)を設ける。次いで、犠牲ゲート構造(300)を除去して、開口(600)を形成する。続けて、スペーサ(400)間の開口(600)内に、タングステン等の金属の第1の層(700)、窒化チタン等の拡散バリア層(800)、およびタングステン等の金属の第2の層(900)を含む金属ゲート(1000)を形成する。

(もっと読む)

高解像度構造を有する有機電子部品及びその生産方法

【課題】本発明は、高解像度構造を有する有機電子部品、特に低ソースドレーン間の距離を有する有機電界効果トランジスタ(OFET)及びその生産方法に関する。

【解決手段】有機電子部品は、生産中レーザーを用いて作られた凹部及び/又は修正された区域を有し、その中には、例えば、金属の導体トラック/電極が配置される。

(もっと読む)

フィン型電界効果トランジスタを有する半導体装置

n型電界効果トランジスタおよびp型電界効果トランジスタとを含む半導体装置であって、n型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{100}面であり、p型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{110}面である、という条件を満足する半導体装置とする。 (もっと読む)

ナノワイヤ複合体およびこれらに由来する電子基板を作製するためのシステムおよび方法

本発明は、ナノワイヤ−材料複合体を生成するシステムおよび処理に関わる。ナノワイヤ(606)が少なくとも一つの表面の一部分(604)に取り付けられた基板が提供される。ナノワイヤ−材料複合体を生成するよう、当該部分上に材料が堆積される。処理は、独立したナノワイヤ−材料複合体を生成するよう基板からナノワイヤ−材料複合体を分離することを必要に応じて含む。独立したナノワイヤ−材料複合体は、必要に応じて、電子基板に更に処理される。様々な電子基板は本明細書記載の方法を用いて形成される。例えば、多色発光ダイオードは、それぞれの複合体層が異なる波長で光を発するナノワイヤ−材料複合体の多数の積層された層から形成され得る。  (もっと読む)

(もっと読む)

格子不整合のソースおよびドレイン領域を有する歪み半導体CMOSトランジスタを有する集積回路および製作方法

【課題】 p型電界効果トランジスタ(PFET)およびn型電界効果トランジスタ(NFET)を有する集積回路を提供することにある。

【解決手段】 第1の歪みは、NFETではなくPFETのみのソースおよびドレイン領域内に配置されたシリコン・ゲルマニウムなどの格子不整合半導体層を介してNFETではなくPFETのチャネル領域に加えられる。PFETおよびNFETを形成するプロセスが提供される。PFETのソースおよびドレイン領域になるためのエリア内にトレンチがエッチングされ、それに隣接するPFETのチャネル領域に歪みを加えるために、格子不整合シリコン・ゲルマニウム層をそこにエピタキシャル成長させる。シリコン・ゲルマニウム層の上にシリコンの層を成長させ、シリコンの層からサリサイドを形成して、低抵抗ソースおよびドレイン領域を提供することができる。

(もっと読む)

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

ポリマーデバイスの製造

(i)ポリマーまたはオリゴマーおよび架橋部分を含む溶液を基板上に成膜して層を形成する工程、および(ii)不溶性架橋化ポリマーを形成する条件下で工程(i)で形成された層を硬化する工程を備え、架橋部分が溶液中のポリマーまたはオリゴマーおよび架橋部分の繰返し単位のモル総数に対して0.05から5モル%の範囲の量で工程(i)に存在することを特徴とする、ポリマーデバイスを形成する方法。 (もっと読む)

自己組織化単分子層を含む電子デバイスおよびこれを製造する方法

【課題】 電子特性が向上した分子層を有する電子デバイスを提供すること。

【解決手段】 電子デバイスは、ソース領域およびドレイン領域と、ソース領域およびドレイン領域に隣接して配置され、少なくとも1つの共役分子を含む自己組織化単分子層と、自己組織化単分子層に隣接した導電性基板と、を含む。

(もっと読む)

有機薄膜トランジスタ

【課題】特殊な技術を要せず、簡単な製造方法でキャリア移動度が高い有機薄膜トランジスタを提供すること。

【解決手段】有機半導体層に重量平均分子量2000以上のπ共役系ポリマー及び分子量2000以下のπ共役系オリゴマーを含有することを特徴とする有機薄膜トランジスタ。

(もっと読む)

絶縁ゲート型電界効果トランジスタを含む半導体装置及びその製造方法

【課題】シリコン基板上のSi1−xGex層を用いた素子構造において、電流駆動能力の高いMISFETを含む半導体装置及びその製造方法を提供することにある。

【解決手段】シリコン基板101上に、Si1−xGex層103を形成し、このSi1−xGex層103にMISFETを形成する。ソース層及びドレイン領域106,107の接合深さを、前記Si1−xGex層103とシリコン層とが接する面を越えないようにする。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】 電気特性の優れた多結晶TFTを提供する。

【解決手段】多結晶膜3を堆積させる工程、堆積した多結晶膜のうち所望の位置4のみを残すようにエッチングする工程、残された部分的な多結晶膜の中で所望の結晶方位の結晶粒5だけを、しかも所望の結晶面(ファセット)6を出した状態になるように異方性エッチングする工程、さらに、こうして得られた結晶核の上に膜を堆積し結晶化させる工程を用いる。

(もっと読む)

薄膜トランジスタアレイ及びその製造方法、液晶表示装置及びその製造方法とエレクトロルミネッセンス表示装置及びその製造方法

【課題】 本発明は薄膜トランジスタアレイ及びその製造方法と液晶表示装置及びその製造方法とエレクトロルミネッセンス表示装置及びその製造方法に関するものであり、均一性と性能に優れた薄膜トランジスタ及びその製造方法を生産性が高く低コストで提供することを目的とする。

【解決手段】 ゲート電極側面に側壁を形成することによって、自己整合的にLDDまたはオフセット領域を形成し、また、層間絶縁膜を複数の層で形成し、これら複数の層間絶縁膜上にソース・ドレイン電極とソースバス配線と画素電極を一括して形成する。

(もっと読む)

半導体膜形成方法及び薄膜半導体装置の製造方法

【課題】 本発明の目的は、基板上に高品質な半導体膜を形成するための半導体膜形成方法を提供することにある。

【解決手段】 本発明は、バイアス触媒CVD,高密度バイアス触媒CVD,バイアス減圧CVD,バイアス常圧CVDを利用して、基板に半導体膜を形成する半導体膜形成方法である。真空容器1に原料ガスを供給し、真空容器1中に配置された基板10と電極3aとの間にグロー放電開始電圧以下の電界を印加して、基板10上に、少なくとも錫、ゲルマニウム、鉛のいずれか一つ以上を含有する半導体膜と、絶縁膜と、を形成することを含む工程と、この半導体膜および絶縁膜にレーザーを照射してアニールする工程と、このアニールする工程の後工程であって、水蒸気でアニールを行う工程と、を備える。

(もっと読む)

2,461 - 2,473 / 2,473

[ Back to top ]