Fターム[5F110BB03]の内容

Fターム[5F110BB03]の下位に属するFターム

CMOS回路 (2,569)

Fターム[5F110BB03]に分類される特許

81 - 100 / 665

半導体装置

【課題】動作速度の低下を抑制しつつ、消費電力を低減する。

【解決手段】第1の半導体領域の上に絶縁領域を有し、且つ絶縁領域の上に第2の半導体領域を有する基板に設けられた第1の電界効果トランジスタと、基板の上に設けられた絶縁層と、絶縁層の一平面に設けられ、酸化物半導体層を含む第2の電界効果トランジスタと、第2の電界効果トランジスタのソース及びドレインと同一工程により形成され、第1の電界効果トランジスタの閾値電圧を制御するための電圧が供給される制御端子と、を備える。

(もっと読む)

回路及び回路の駆動方法

【課題】消費電力を低減する。

【解決手段】入力信号を元に論理演算処理を行い、論理演算処理の結果に応じて設定される電位を記憶データとして保持し、記憶データに応じた値の信号を出力信号として出力する機能を有する演算回路を具備し、演算回路は、論理演算処理を行う演算部と、記憶データの電位を、論理演算処理の結果に応じた電位に設定するか否かを制御する第1の電界効果トランジスタと、記憶データの電位を、基準電位に設定するか否かを制御する第2の電界効果トランジスタと、記憶データに応じた値の信号を出力信号として出力するか否かを制御する第3の電界効果トランジスタと、を備える。

(もっと読む)

半導体装置

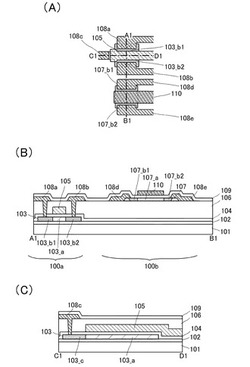

【課題】トランジスタの損傷、破壊の発生を抑制することができる半導体装置を提供する。

【解決手段】第1の基板11上の第1の絶縁層12と、第1の絶縁層上のトランジスタ13と、トランジスタ上の第2の絶縁層14と、第2の絶縁層14に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に接続された第1の導電層15〜18と、第1の導電層上の第3の絶縁層38と、第3の絶縁層38上の第2の基板19と、を有し、トランジスタは、半導体層20と、第2の導電層22と、半導体層20と第2の導電層22の間に設けられた第4の絶縁層21とを有し、第1の絶縁層12、第2の絶縁層14、第3の絶縁層38及び第4の絶縁層21から選択された一つ又は複数は、トランジスタと重ならないように設けられた段差部を有する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体装置

【課題】ラッチ型メモリが搭載されたCPUを動作させるに際して、処理内容に応じて常時記憶方式と終了時記憶方式のいずれかを選択し、ラッチ型メモリが搭載されたCPUの消費電力を低減する。

【解決手段】ラッチ型メモリが搭載されたCPUを動作させるに際して、電源のオンオフの繰り返し動作が多い場合には常時記憶方式とし、電源のオンオフの繰り返し動作が少ない場合には終了時記憶方式とする。常時記憶方式と終了時記憶方式のどちらを選択するかは、消費電力に応じて決定したしきい値をもとにして決定する。

(もっと読む)

半導体装置

【課題】チャネル形成領域の空乏化領域を増やし、電流駆動能力の高い半導体装置を提供する。

【解決手段】島状の半導体領域308と、前記島状の半導体領域308の側面及び上面を覆って設けられたゲート絶縁膜310と、前記ゲート絶縁膜310を介して前記島状の半導体領域308の前記側面及び前記上面を覆って設けられたゲート電極とを有し、前記島状の半導体領域308の前記側面及び前記上面はチャネル形成領域として機能する半導体装置である。

(もっと読む)

半導体装置

【課題】容易に共振周波数の設定を行う。

【解決手段】コイルとしての機能を有するアンテナと、アンテナと並列接続で電気的に接続される容量素子と、アンテナ及び容量素子と並列接続で電気的に接続されることにより、アンテナ及び容量素子と共振回路を構成する受動素子と、受動素子とアンテナ及び容量素子を並列接続で電気的に接続するか否かを制御する第1の電界効果トランジスタと、記憶回路と、を備え、記憶回路は、チャネルが形成される酸化物半導体層を含み、ソース及びドレインの一方にデータ信号が入力され、ソース及びドレインの他方の電圧に応じて第1の電界効果トランジスタのゲートの電圧が設定される第2の電界効果トランジスタを備える。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

半導体装置

【課題】占有面積が小さく、冗長性があり、かつリーク電流の小さい保護回路を提供する。

【解決手段】保護回路は、複数の非線形素子が重畳するように積層され、かつ該非線形素子が電気的に直列接続されている構成であり、該保護回路に含まれる少なくとも一つの非線形素子は、チャネル形成領域に酸化物半導体を用いたトランジスタをダイオード接続した素子であり、他の非線形素子は、チャネル形成領域にシリコンを用いたトランジスタをダイオード接続した素子、または、接合領域にシリコンを用いたダイオードとする。

(もっと読む)

記憶回路

【課題】消費電力を抑えることができる記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性のメモリに相当する記憶部に記憶されていたデータを、不揮発性のメモリに相当する記憶部に設けられた容量素子によって保持する記憶回路である。不揮発性記憶部では、酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、容量素子に保持された信号は長期間にわたり保持することができる。こうして、記憶回路は電源の供給が停止している間も論理状態(データ信号)を保持することが可能である。また酸化物半導体層にチャネルが形成されるトランジスタのゲートに印加する電位を、電源電位を供給する配線と前記トランジスタのゲートとの間に設けられた昇圧回路によって高くすることで、1つの電源電位であっても誤動作なくデータ信号の保持を行うことが可能である。

(もっと読む)

半導体装置

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタがオン・オフするのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。また、トランジスタの微細化を進めて集積化を図っても、メモリ容量を増加させるためには、半導体装置の面積が大きくなるといった問題があった。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。また、トレンチ構造の酸化物半導体を有するトランジスタにより、半導体装置の記憶素子を構成し、該記憶素子を複数積層することで、半導体装置の回路面積を縮小することができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

半導体集積回路

【課題】半導体集積回路における消費電力を低減すること。また、半導体集積回路における動作の遅延を低減すること。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

半導体装置

【課題】半導体装置を小型化する。また、メモリセルを有する半導体装置の駆動回路の面積を縮小する。

【解決手段】少なくとも第1の半導体素子を有する素子形成層と、素子形成層上に設けられた第1の配線と、第1の配線上に設けられた層間膜と、層間膜を介して第1の配線と重畳する第2の配線と、を有し、第1の配線と、層間膜と、第2の配線と、は、第2の半導体素子を構成し、第1の配線と、第2の配線と、は、同電位が供給される配線である半導体装置である。

(もっと読む)

半導体装置とその動作方法

【課題】半導体装置において、消費電力を低減する。また、スタンバイ回路を少ない素子で構成し、半導体装置の回路面積の増大を防ぐ。

【解決手段】半導体装置に備えるスタンバイ回路をトランジスタ一つのみで構成し、該トランジスタに供給する電圧を切り替えることで、半導体装置の出力電流を制御する。これにより、スタンバイ状態での半導体装置の出力電流をほぼゼロにすることができるため、消費電力の低減が可能になる。なお、トランジスタの半導体層に酸化物半導体を用いることで、リーク電流を極小に抑えることができる。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】酸化物半導体膜を含むトランジスタにおいて、酸化物半導体膜に接し、且つ

ソース電極及びドレイン電極を覆う帯電防止機能を有する金属酸化膜を形成し、加熱処理

を行う。この加熱工程によって、水素、水分、水酸基又は水素化物などの不純物を酸化物

半導体膜より意図的に排除し、酸化物半導体膜を高純度化する。また、金属酸化膜を設け

ることで、トランジスタにおいて酸化物半導体膜のバックチャネル側に寄生チャネルが発

生するのを防止する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料を用いたトランジスタと、第1の半導体材料とは異なる第2の半導体材料を用いたトランジスタと、容量素子とを有する複数のメモリセルを有し、書き込み期間にソース線に電源電位を供給する機能を有する電位切り替え回路を備えた半導体装置とする。これにより、半導体装置の消費電力を十分に抑えることができる。

(もっと読む)

半導体装置

【課題】処理実行中に電源をオフしてもデータが保持され、且つ従来よりも占有面積が小さいDフリップフロップ回路を有する半導体装置を提供する。

【解決手段】入力端子が、第1のトランスミッションゲートの第1の端子に電気的に接続され、第1のトランスミッションゲートの第2の端子が、第1のインバータの第1の端子及び機能回路の第2の端子に電気的に接続され、第1のインバータの第2の端子及び機能回路の第1の端子が、第2のトランスミッションゲートの第1の端子に電気的に接続され、第2のトランスミッションゲートの第2の端子が第2のインバータの第1の端子及びクロックドインバータの第2の端子に電気的に接続され、第2のインバータの第2の端子及びクロックドインバータの第1の端子は出力端子に電気的に接続されており、機能回路にはオフ電流が小さいトランジスタと容量素子との間にデータ保持部を有する半導体装置とする。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を用いたnチャネルTFTのみを用いてバッファ回路やインバータ回路などを構成することを課題の一つとする。

【解決手段】ソース電極及びドレイン電極の両方がゲート電極に重なる第1のトランジスタと、ソース電極はゲート電極と重ね、且つ、ドレイン電極はゲート電極と重ならない第2のトランジスタとを組み合わせてバッファ回路やインバータ回路などを構成する。第2のトランジスタをこのような構造とすることによって、容量Cpを小さくし、電位差VDD−VSSが小さい場合でもVA’が大きくとれるようになる。

(もっと読む)

半導体装置

【課題】開示する発明の一態様は、安定して動作することが可能なパルス信号出力回路及

びそれを含むシフトレジスタを提供することを課題の一とする。

【解決手段】開示する発明の一態様のパルス信号出力回路は、第1乃至第10のトランジ

スタを有し、第1のトランジスタおよび第3のトランジスタのチャネル長Lに対するチャ

ネル幅Wの比W/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタ

のW/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは

、第7のトランジスタのW/Lと等しく、第3のトランジスタのW/Lは、第4のトラン

ジスタのW/Lよりも大きくする。これによって、安定して動作することが可能なパルス

信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

81 - 100 / 665

[ Back to top ]