Fターム[5F110BB03]の内容

Fターム[5F110BB03]の下位に属するFターム

CMOS回路 (2,569)

Fターム[5F110BB03]に分類される特許

141 - 160 / 665

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】酸化物半導体膜を用いたトランジスタに安定した電気特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】n型酸化物半導体膜中にp型酸化物半導体材料を含ませることで酸化物半導体膜中に意図せずに生じるキャリアを低減することができる。これは、n型酸化物半導体膜中の意図せずに生じた電子が、p型酸化物半導体材料中に生じたホールと再結合することにより、消滅するためである。従って、酸化物半導体膜中に意図せずに生じるキャリアを低減することができる。

(もっと読む)

半導体装置

【課題】簡素でかつ占有面積の小さな駆動回路を提供すること。

【解決手段】本発明のシフトレジスタ回路は、複数のレジスタ回路を有している。各レジスタ回路は、クロックドインバータ回路およびインバータ回路を有している。クロックドインバータ回路の出力信号がインバータ回路の入力信号となるよう両者が直列に接続されている。さらに、レジスタ回路は、インバータ回路の出力信号が伝達される信号線を有している。該信号線には接続されている素子が多く寄生容量が大きいため高負荷である。本発明のシフトレジスタ回路は、信号線の寄生容量が大きいために高負荷であることを用いている。

(もっと読む)

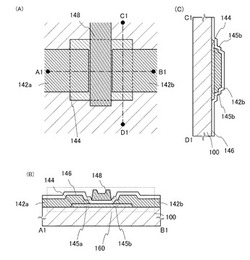

半導体装置の作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。酸化物半導体層の側壁はサイドウォール絶縁層により覆われている。なお、該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

記憶素子、記憶装置、信号処理回路、記憶素子の駆動方法

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶素子を提供する。消費電力の低減可能な信号処理回路を提供する。

【解決手段】クロック信号に同期してデータを保持する記憶素子において、酸化物半導体層にチャネルが形成されるトランジスタ及び容量素子を用いることより、電源電圧の供給が停止した間もデータ保持ができる。ここで、電源電圧の供給を停止する前に、クロック信号のレベルを一定に保った状態で当該トランジスタをオフ状態とすることにより、データを正確に容量素子に保持させることができる。また、このような記憶素子を、CPU、メモリ、及び周辺制御装置のそれぞれに用いることによって、CPUを用いたシステム全体で、電源電圧の供給停止を可能とし、当該システム全体の消費電力を削減することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】基板上に第1の酸化絶縁膜を形成し、該第1の酸化絶縁膜上に第1の酸化物半導体膜を形成した後、加熱処理を行い、第1の酸化物半導体膜に含まれる水素を脱離させつつ、第1の酸化絶縁膜に含まれる酸素の一部を第1の酸化物半導体膜に拡散させ、水素濃度及び酸素欠陥を低減させた第2の酸化物半導体膜を形成する。次に、第2の酸化物半導体膜を選択的にエッチングして、第3の酸化物半導体膜を形成した後、第2の酸化絶縁膜を形成して、当該第2の酸化絶縁膜を選択的にエッチングして、第3の酸化物半導体膜の端部を覆う保護膜を形成する。この後、第3の酸化物半導体膜及び保護膜上に一対の電極、ゲート絶縁膜、及びゲート電極を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

半導体装置及び電子機器

【課題】薄膜の応力を用いてしきい値電圧を制御する。

【解決手段】第1の半導体層に設けられた第1のゲート電極と、第2の半導体層に設けられた第2のゲート電極と、第1の半導体層と第2の半導体層に接して設けられた第1の絶縁層と、第1の絶縁層が設けられた第1の半導体層の一方の面の反対側に設けられた第2の絶縁層と、第1の絶縁層が設けられた第2の半導体層の一方の面の反対側に設けられた第2の絶縁層及び第3の絶縁層と、を有し、第1の半導体層には第2の絶縁層により応力が加わり、第2の半導体層には第2の絶縁層と第3の絶縁層により応力が加わることで、第1の半導体層及び第2の半導体層に加わる応力が異なる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供すること。

【解決手段】トランジスタと、容量素子と、を有し、トランジスタは、第1の酸化物半導体層と、第1の酸化物半導体層と接するソース電極およびドレイン電極と、第1の酸化物半導体層と重なるゲート電極と、第1の酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、容量素子は、ソース電極またはドレイン電極と、ソース電極またはドレイン電極と接する第2の酸化物半導体層と、第2の酸化物半導体層と接する容量素子電極と、を有する半導体装置である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】高速動作可能な半導体装置を提供する。また、短チャネル効果による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】トランジスタの半導体層に結晶性を有する酸化物半導体を用い、該半導体層にチャネル形成領域とソース領域とドレイン領域を形成する。ソース領域及びドレイン領域は、ゲート電極をマスクとして、半導体層に第15族元素のうち一種類または複数種類の元素を添加する自己整合プロセスにより形成する。ソース領域及びドレイン領域に、ウルツ鉱型の結晶構造を付与することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、窒素、リン、又は砒素など15族元素のいずれか一以上の元素が添加されている。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、水素または希ガスのいずれかの元素が添加されている。

(もっと読む)

半導体記憶装置

【課題】動作速度の向上と面積の縮小を図る。

【解決手段】半導体記憶装置は、半導体基板100と、前記半導体基板上に形成され、データを記憶する複数のメモリセルが配置されたメモリセルアレイ部Aと、前記メモリセルアレイ部上に絶縁層を介して形成され、かつ、前記絶縁層および前記メモリセルアレイ部を貫通する孔106内に形成されて前記半導体基板に接続された単結晶半導体層109と、前記単結晶半導体層上に形成された回路部Bと、を具備し、前記メモリセルアレイ部上における前記単結晶半導体層の下部側は、上部側よりもGe濃度が高い。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

半導体装置

【課題】短チャネルでもオフ特性の優れたトランジスタ等の半導体装置を提供する。

【解決手段】ソース102aの周囲をエクステンション領域103aおよびハロー領域105a、ドレイン102bの周囲をエクステンション領域103bおよびハロー領域105bで取り囲むように配置し、また、不純物濃度の低い基板101がソース102a、ドレイン102bと接しない構造とする。さらに、ゲート絶縁物109を介して高仕事関数電極104を設け、基板101の表面近傍にエクステンション領域103aおよびエクステンション領域103bより侵入する電子を排除する。このような構造とすることにより、短チャネルでもチャネル領域の不純物濃度を低下させることができ、良好なトランジスタ特性を得ることができる。

(もっと読む)

高周波スイッチ

【課題】挿入損失特性および高調波特性が共に良好な高周波スイッチを実現することを目的とする。

【解決手段】アンテナへ送信信号が出力される共通ポートと、送信信号が入力される送信ポートと、複数の前記送信ポートと前記共通ポートとの間にそれぞれ接続され、各送信ポートと前記共通ポートとを導通または遮断する複数のスイッチ部と、を有し、前記スイッチ部は、シリコン基板に形成され直列に接続された複数のMOSFETを有し、前記複数のMOSFETはボディコンタクト型FETおよびフローティングボディ型FETのいずれかであって、各スイッチ部はボディコンタクト型FETおよびフローティングボディ型FETの両方を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置

【課題】低消費電力で高速シリアル伝送が可能な半導体装置を提供する。

【解決手段】実施形態によれば、インタフェース部と、駆動回路部と、スイッチ部と、電源回路部と、を備えた半導体装置が提供される。前記インタフェース部は、フローティング状態のバックゲートを有しSOI基板上に設けられた第1のMOSFETを含み、入力したシリアルデータの端子切替信号をパラレルデータに変換する。前記電源回路部は、ソースに接続されたバックゲートを有し前記SOI基板上に設けられた第2のMOSFETを含み、前記インタフェース部に供給される電源の電位よりも高いオン電位を生成する。前記駆動回路部は、ソースに接続されたバックゲートを有し前記SOI基板上に設けられた第3のMOSFETを含み、前記パラレルデータに応じて、前記オン電位をハイレベルとする制御信号を出力する。前記スイッチ部は、前記SOI基板上に設けられ、前記制御信号を入力して端子間の接続を切り替える。

(もっと読む)

半導体デバイス及びその駆動方法

【課題】半導体デバイスの小面積化を実現する。

【解決手段】電極と、第1絶縁体と、バンドギャップが2eV以上の第1半導体と、第2絶縁体と、第2半導体とが積層されており、第1半導体に接する1つ以上の電極と、第2半導体に接する2つ以上の電極とを少なくとも備えることを特徴とする半導体デバイス。

(もっと読む)

半導体薄膜、薄膜トランジスタ及びその製造方法

【課題】耐還元性に優れた半導体薄膜及びその製造方法、チャネル層上に酸素透過性膜等のバッファー層を設けなくても安定したTFT特性が得られる薄膜トランジスタ及びその製造方法を提供する。

【解決手段】1種以上のアモルファス金属酸化物を含有し、前記金属酸化物の少なくとも一部の金属原子にOH基が結合している半導体薄膜。

(もっと読む)

141 - 160 / 665

[ Back to top ]