Fターム[5F110BB03]の内容

Fターム[5F110BB03]の下位に属するFターム

CMOS回路 (2,569)

Fターム[5F110BB03]に分類される特許

161 - 180 / 665

半導体装置

【課題】電界効果型トランジスタのLSI製造後にしきい電圧の制御が可能で、かつ、回路面積を増大させず、かつ信頼性に優れるという特徴を有する技術を提供する。

【解決手段】シリコン半導体支持基板1の上面に設けられた積層膜(3nm以上4nm以下の第1のシリコン酸化膜2/0.3nm以上2nm以下のシリコン窒化膜3/5nm以上10nm以下の第2のシリコン酸化膜4/3nm以上20nm以下の膜厚)を有するSOI層5と、上記構造に所定の間隔を介して互いに対向して設けられたソース・ドレイン拡散層6と、当該ソース拡散層とドレイン拡散層の間の上記半導体基板の表面上に形成されたゲート絶縁膜7と、上記ゲート絶縁膜の上に形成されたゲート電極8を具備してなる電界効果型半導体装置において、シリコン支持基板1から電圧を印加することにより、直接トンネル効果によって電荷をシリコン窒化膜3に一定時間保持してしきい電圧を調整する。

(もっと読む)

EL表示装置及びその作製方法

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピング法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

半導体装置

【課題】半導体装置を小型化することを課題の一とする。また、記憶素子を有する半導体装置の駆動回路の面積を縮小することを課題の一とする。

【解決手段】入力端子と出力端子の位置が固定された複数のセルを第1の方向に配置し、各セルの入力端子および出力端子とそれぞれ電気的に接続される配線を複数のセル上に積層させ、且つ、その配線の延在方向をセルが並べられた第1の方向と同方向とすることで、駆動回路の小型化を図った半導体装置を提供する。

(もっと読む)

半導体記憶装置

【課題】メモリデータを外部回路を用いずに、コピーを行う半導体記憶装置を提供することを課題とする。

【解決手段】複数のメモリセルの第一端子が共通接続されたビット線と、ビット線に接続され、読み出し時にビット線を特定の電位にプリチャージするプリチャージ回路と、メモリセルから読み出したデータ、もしくはメモリセルへの書き込みデータを一時的に保持する容量素子を有するデータ保持回路と、データ保持回路で保持しているデータの反転データをビット線に出力する反転データ出力回路とを有し、反転データ出力回路は、データ保持回路で保持しているデータの反転データの出力を制御する手段を有する構成とする。

(もっと読む)

半導体装置および携帯電話機

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】RXスルートランジスタ群TH(RX)は、互いに直列に接続されたMISFETQ1〜Q5において、それぞれのMISFETのボディ領域と、隣接するMISFETのソース領域あるいはドレイン領域とを、それぞれ、ダイオード(整流素子)を介して接続する。そして、特に、nチャネル型MISFETの場合、MISFETのボディ領域から隣接するMISFETのソース領域あるいはドレイン領域へ向う向きが順方向となるようにダイオードを接続する。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】複数の基準電位を要する半導体装置、及び半導体装置の駆動において、より消費電力を軽減する。

【解決手段】電源線に直列に接続された複数の抵抗素子により、電源線に供給された電位を抵抗分割し、電源線と電気的に接続するスイッチトランジスタを介して所望の分割された電位を出力する電位分割回路を有する半導体装置であり、スイッチトランジスタのドレイン端子は出力側の回路に設けられたトランジスタのゲート端子(又は容量素子の一方の端子)と電気的に接続しノードを構成する。

(もっと読む)

半導体装置

【課題】メモリセルの保持データが多値化された場合であっても正確なデータを保持することが可能なメモリセルを有する半導体装置を供給すること。

【解決手段】半導体装置に、酸化物半導体によってチャネル領域が形成されるトランジスタのソース及びドレインの一方が電気的に接続されたノードにおいてデータの保持を行うメモリセルを設ける。なお、当該トランジスタのオフ電流(リーク電流)の値は、極めて低い。そのため、当該ノードの電位を所望の値に設定後、当該トランジスタをオフ状態とすることで当該電位を一定又はほぼ一定に維持することが可能である。これにより、当該メモリセルにおいて、正確なデータの保持が可能となる。

(もっと読む)

記憶装置、半導体装置

【課題】長い期間においてデータの保持が可能な記憶装置を提供する。

【解決手段】記憶素子と、上記記憶素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタとを有する。上記トランジスタは、通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられており、また、活性層に酸化物半導体を含むためにオフ電流が極めて低い。上記記憶装置では、絶縁膜に囲まれたフローティングゲートに高電圧で電荷を注入するのではなく、オフ電流の極めて低いトランジスタを介して記憶素子の電荷量を制御することで、データの記憶を行う。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

多結晶シリコン半導体素子及びその製造方法

【課題】多結晶シリコン半導体素子及びその製造方法を提供する。

【解決手段】ゲート共通化ラインに存在するシリコン物質層による寄生キャパシタンスを減少させるために、製造工程中にゲート以外の他の部分の不要なシリコン物質を除去する。シリコン物質層は、ゲートの下部のみに局地的に存在し、したがって、寄生キャパシタンスの減少によって信号遅延が抑制されて良好な電気的特性を有する薄膜トランジスタの多結晶シリコン半導体素子が得られる。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】半導体材料として特定の有機複素環化合物を用いて、実用的な印刷適性を有し、さらにキャリア移動度、ヒステリシスや閾値安定性などの優れた半導体特性を有し、産業上実用的な特定のトップゲート構造の電界効果トランジスタを提供する。

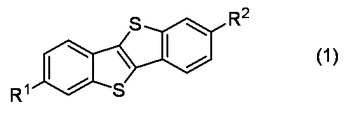

【解決手段】半導体材料として下記式(1)で表される化合物を含有し、特定のトップゲート−ボトムコンタクト構造を有することを特徴とする電界効果トランジスタ。

(式(1)中、R1及びR2はそれぞれ独立に無置換またはハロゲノ置換C1−C36脂肪族炭化水素基を表す。)

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ソース線と、ビット線と、信号線と、ワード線と、ソース線とビット線との間に、並列に接続されたメモリセル1100と、ソース線及びビット線とスイッチング素子を介して電気的に接続された第1の駆動回路1111と、ソース線とスイッチング素子を介して電気的に接続された第2の駆動回路1112と、信号線と電気的に接続された第3の駆動回路1113と、ワード線と電気的に接続された第4の駆動回路1114と、を有し、メモリセルは、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、容量素子と、を有し、第2のトランジスタは、酸化物半導体材料を含む。

(もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【課題】自己整列リセス・ゲート構造及び形成方法の提供。

【解決手段】最初に,絶縁用のフィールド酸化物領域20を半導体基板10内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタと第2のトランジスタを有し、第1のトランジスタと第2のトランジスタとは少なくとも一部が重畳する第1のメモリセルと、第3のトランジスタと第4のトランジスタを有し、第3のトランジスタと第4のトランジスタとは少なくとも一部が重畳する第2のメモリセルと、駆動回路と、を有し、第2のメモリセルは、第1のメモリセル上に設けられ、第1のトランジスタは、第1の半導体材料を含んで構成され、第2のトランジスタ、第3のトランジスタ、および第4のトランジスタ、は、第2の半導体材料を含んで構成される半導体装置である。

(もっと読む)

電界効果トランジスタ

【課題】インジウムを主要成分とし、金属半導体接合を用いた電界効果トランジスタのオフ電流を低減せしめる構造を提供する。

【解決手段】インジウムを主要成分とする、厚さ0.1〜100nmの第1の酸化物半導体(例えば、酸化インジウム)よりなる第1の半導体層1の一方の面に絶縁膜4を設け、他の面に接して、I型の第2の酸化物半導体(例えば、酸化ガリウム)よりなる第2の半導体層2を設ける。第2の酸化物半導体の真空準位からフェルミレベルまでのエネルギー差は第1の酸化物半導体のものよりも大きい。上記の条件を満たす第2の酸化物半導体との接触面近傍においては、極めてキャリア濃度の低い領域(準I型領域)となるので、その部分をチャネルとすることにより、オフ電流が低減できる。また、FETのドレイン電流は移動度の高い第1の酸化物半導体を流れるので、大電流を取り出せる。

(もっと読む)

半導体装置

【課題】低電位領域と高電位の配線が交差することの無い優れた耐圧性能を示す半導体装置を提供することを課題とする。

【解決手段】本発明の半導体装置は、ロジック回路(501)と、ロジック回路からの制御信号に従い低電位側パワー素子を駆動する低電位側駆動回路(502)と、ロジック回路からの制御信号がレベルシフト回路を介して入力され、高電位側パワー素子(506)を駆動する高電位側駆動回路(505)と、複数に重なったトレンチ分離領域により、前記高電位側パワー素子を含む高電位島を分離する多重トレンチ分離領域(508)と、を有する。

(もっと読む)

DCDCコンバータ、電源回路及び半導体装置

【課題】電力変換効率の向上を実現するDCDCコンバータの提供を目的の一とする。

【解決手段】出力電力を制御するためのスイッチング素子として機能するトランジスタが、通常のゲート電極に加えて、閾値電圧を制御するためのバックゲート電極を備える。そして、DCDCコンバータから出力される出力電力の大きさに従って、バックゲート電極に与える電位の高さを制御するための、バックゲート制御回路を備える。バックゲート制御回路により、バックゲート電極に与える電位を制御することで、出力電力が大きい場合にはオン抵抗が下がるように閾値電圧を調整し、出力電力が小さい場合にはオフ電流が下がるように閾値電圧を調整することができる。さらに、スイッチング素子として機能するトランジスタが、オフ電流の極めて小さい絶縁ゲート電界効果型トランジスタである。

(もっと読む)

電界効果トランジスタの製造方法、電界効果トランジスタおよび半導体酸化グラフェンの製造方法

【課題】オン/オフ比が高く、しかも構造も簡単な、半導体酸化グラフェンを用いた電界効果トランジスタを低コストかつ高い歩留まりで製造することができる電界効果トランジスタの製造方法を提供する。

【解決手段】基板11上に形成された絶縁膜12上にアミノ基を有する分子からなる分子層13を形成した後、この分子層13上に酸化グラフェン14を形成する。酸化グラフェン14を熱的または化学的に還元することにより半導体酸化グラフェン15を形成する。半導体酸化グラフェン15をチャネル層に用いて電界効果トランジスタを製造する。酸化グラフェン14を熱的に還元する際の雰囲気としては例えば大気を用いる。

(もっと読む)

半導体デバイスの動作方法

【課題】高いバイアス電圧を必要とせずに、メモリセルとして動作可能なマルチゲート半導体デバイスを提供する。

【解決手段】マルチゲートMOSFETをベースとした、比較的低いバイアス電圧を要するキャパシタレスのメモリデバイス。充分な本体係数を用意し、VTフィードバックループを導入することによって、閾値電圧をゲート−本体間電圧を関連させる蓄積層を用いて、ヒステリシスウインドウ(H)を導入できる。MOSFETは、「1」値または「0」値を保存することができ(54,51)、(プログラムウインドウPWの範囲内で)保存した値を読み出し、ホールドする(50)。デバイスは、1.5Vなどの比較的低い動作電圧、1016動作サイクルなどの高い信頼性、〜5秒などの長い保持時間で動作する。

(もっと読む)

161 - 180 / 665

[ Back to top ]