Fターム[5F110BB05]の内容

Fターム[5F110BB05]の下位に属するFターム

Fターム[5F110BB05]に分類される特許

201 - 220 / 737

トランジスタおよびメモリアレイ

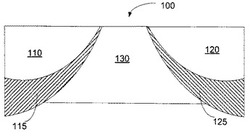

【課題】大きな順方向−逆方向電流比を有するスイッチングデバイスを提供する。

【解決手段】トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

(もっと読む)

半導体記憶装置

【課題】単位面積あたりのメモリモジュールの記憶容量を増加させる。また、消費電力の小さなメモリモジュールを提供する。

【解決手段】DRAMに、高純度化された、バンドギャップが2.5eV以上の酸化物半導体膜、炭化シリコン膜および窒化ガリウム膜などでなるトランジスタを用いることで、キャパシタの電位の保持期間が延びる。また、メモリセルが容量の異なるn個のキャパシタを有し、n個のキャパシタとそれぞれ異なるn本のデータ線を接続することによって保持容量を様々にとることができる。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

錫を含む非晶質酸化物薄膜、及び薄膜トランジスタ

【課題】トランジスタ特性が良好で、ディスプレイパネルに適した電界効果トランジスタを提供する。

【解決手段】少なくとも錫(Sn)を含み、SnOとSnO2の合計を100モル%としたときのSnOの割合が30モル%未満である非晶質酸化物薄膜。

(もっと読む)

ペロブスカイト型の複合酸化物をチャンネル層とする電界効果トランジスタ及びその製造方法と、これを利用したメモリ素子

【課題】電気二重層法を用いてチャンネルに高濃度の電荷注入を行うことで抵抗を変化させる電界効果トランジスタと、該電界効果トランジスタをスイッチング素子として利用したメモリ素子を提供する。

【解決手段】化学式がCa1−xCexMnO3(但し、xは0≦x<1を満たす実数である)で表される複合酸化物からなる単結晶膜をチャンネル層として、電界効果トランジスタを構成する。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】データの保持期間を長くする半導体装置又は半導体記憶装置を提供する。

【解決手段】一対の不純物領域を有する第1の半導体層152aと、第1の半導体層と同じ材料であり、第1の半導体層と離間する第2の半導体層152bと、第1、第2の半導体層の上に設けられた第1の絶縁層153と、第1の絶縁層153を介して第1の半導体層に重畳する第1の導電層154と、第1の絶縁層153を介して第1の導電層に重畳し、第1の半導体層と異なる材料である第3の半導体層156と、第1の導電層及び第3の半導体層に電気的に接続される第2の導電層157bと、第3の半導体層156に電気的に接続され、第2の導電層と同じ材料である第3の導電層157aと、第3の半導体層、第2の導電層、及び第3の導電層の上に設けられた第2の絶縁層158と、第2の絶縁層を介して第3の半導体層に重畳する第4の導電層159と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】溝型の素子間分離部により囲まれた活性領域に形成される電界効果トランジスタにおいて、所望する動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部SIOを、溝型素子分離膜6L,6Sと、溝型素子分離膜6L,6Sの上面に形成されたシリコン膜またはシリコン酸化膜からなる厚さ10〜20nmの拡散防止膜20と、拡散防止膜20の上面に形成された厚さ0.5〜2nmのシリコン酸化膜21L,21Sとから構成し、拡散防止膜20の組成をSiOx(0≦x<2)とし、溝型素子分離膜6L,6Sおよびシリコン酸化膜21L,21Sの組成をSiO2とする。

(もっと読む)

半導体薄膜、薄膜トランジスタ及びその製造方法

【課題】耐還元性に優れた半導体薄膜及びその製造方法、チャネル層上に酸素透過性膜等のバッファー層を設けなくても安定したTFT特性が得られる薄膜トランジスタ及びその製造方法を提供する。

【解決手段】1種以上のアモルファス金属酸化物を含有し、前記金属酸化物の少なくとも一部の金属原子にOH基が結合している半導体薄膜。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】 水分に起因するTFT特性の変化を抑制した薄膜トランジスタおよびその製造方法を提供する。

【解決手段】 本発明の薄膜トランジスタは、基板上に、少なくともゲート電極、ゲート絶縁膜、活性層、ソース電極、およびドレイン電極が設けられ、活性層上にソース電極およびドレイン電極が設けられたものである。活性層は、アモルファス酸化物半導体により構成されており、ゲート絶縁膜内に存在する第1の水分量が活性層に存在する第2の水分量よりも少ない。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込みワード線に電気的に接続する容量素子またはノイズ除去回路を設けることで、駆動回路等からメモリセルに入力されうる制御信号とは異なる短パルスやノイズ等の信号を低減または除去することができる。これにより、メモリセルが有するトランジスタが瞬間的にオンすることでメモリセルに書き込まれたデータが消失してしまう誤動作を防ぐことが可能である。

(もっと読む)

結晶性酸化物半導体膜の作製方法

【課題】優れた結晶性を有する酸化物半導体膜を作製する。

【解決手段】酸化物半導体の膜を形成するに際し、基板を第1の温度以上第2の温度未満に加熱しつつ、基板の、典型的な長さが1nm乃至1μmの部分だけ、第2の温度以上の温度に加熱する。ここで、第1の温度とは、何らかの刺激があれば結晶化する温度であり、第2の温度とは、刺激がなくとも自発的に結晶化する温度である。また、典型的な長さとは、その部分の面積を円周率で除したものの平方根である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体膜を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体用ターゲットに含まれる複数種の原子の原子量の違いを利用し、原子量の小さい亜鉛を優先的に酸化物絶縁膜に堆積させ、亜鉛を含む種結晶を形成すると共に、種結晶上に原子量の大きいスズ、インジウム等を結晶成長させつつ堆積させることで、複数の工程を経ずとも、結晶性酸化物半導体膜を形成することを要旨とする。さらには、種結晶として、六方晶構造の亜鉛を含む結晶を有する種結晶を核として、結晶成長させて結晶性酸化物半導体膜を形成することで、単結晶、または実質的に単結晶である結晶性酸化物半導体膜を形成することを要旨とする。

(もっと読む)

半導体装置の作製方法

【課題】高性能、高信頼性のトランジスタを有する半導体装置を作製する技術を提供する。

【解決手段】配線層を導電層から形成する際に酸化物半導体層を保護するための保護導電膜を酸化物半導体層と導電層との間に形成して、2段階のエッチングを行う。第1のエッチング工程には、保護導電膜は導電層よりエッチングされにくく、導電層と保護導電膜とのエッチング選択比が高い条件で行うエッチング方法を採用し、第2のエッチング工程には、保護導電膜は酸化物半導体層よりエッチングされやすく、保護導電膜と酸化物半導体層とのエッチング選択比が高い条件で行うエッチング方法を採用する。

(もっと読む)

半導体記憶装置

【課題】メモリデータを外部回路を用いずに、コピーを行う半導体記憶装置を提供することを課題とする。

【解決手段】複数のメモリセルの第一端子が共通接続されたビット線と、ビット線に接続され、読み出し時にビット線を特定の電位にプリチャージするプリチャージ回路と、メモリセルから読み出したデータ、もしくはメモリセルへの書き込みデータを一時的に保持する容量素子を有するデータ保持回路と、データ保持回路で保持しているデータの反転データをビット線に出力する反転データ出力回路とを有し、反転データ出力回路は、データ保持回路で保持しているデータの反転データの出力を制御する手段を有する構成とする。

(もっと読む)

半導体装置

【課題】半導体装置を小型化することを課題の一とする。また、記憶素子を有する半導体装置の駆動回路の面積を縮小することを課題の一とする。

【解決手段】入力端子と出力端子の位置が固定された複数のセルを第1の方向に配置し、各セルの入力端子および出力端子とそれぞれ電気的に接続される配線を複数のセル上に積層させ、且つ、その配線の延在方向をセルが並べられた第1の方向と同方向とすることで、駆動回路の小型化を図った半導体装置を提供する。

(もっと読む)

トランジスタ、液晶表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】島状半導体層を形成するための工程を省略し、ゲート電極を形成する工程(同一層で形成される配線を含む)、ソース電極及びドレイン電極を形成する工程(同一層で形成される配線を含む)、コンタクトホールを形成する(コンタクトホール以外の絶縁層等の除去を含む)工程、画素電極(同一層で形成される配線を含む)を形成する工程の4つのフォトリソグラフィ工程で液晶表示装置を作製する。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。配線の形状及び電位を工夫することで、寄生チャネルの形成を防ぐ。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板901上に画素と不揮発性メモリとを備え、不揮発性メモリは、基板901上に形成される半導体活性層と、半導体活性層上に形成される絶縁膜923と、絶縁膜923上に形成されるフローティングゲイト電極907と、フローティングゲイト電極907を酸化して得られる酸化膜908,915,922と、酸化膜908,915,922に接して形成されるコントロールゲイト電極929と、を備え、画素と不揮発性メモリとは、基板901上に一体形成される。

(もっと読む)

201 - 220 / 737

[ Back to top ]