Fターム[5F110BB05]の内容

Fターム[5F110BB05]の下位に属するFターム

Fターム[5F110BB05]に分類される特許

141 - 160 / 737

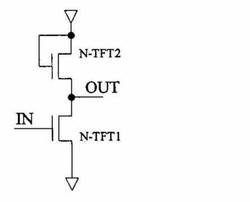

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

記憶素子および信号処理回路

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路を提供する。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、アモルファスシリコン、ポリシリコン、微結晶シリコン、あるいは酸化物半導体等の化合物半導体をチャネル形成領域に含み、そのチャネル長が最小加工線幅の10倍以上あるいは、1μm以上であるトランジスタを用いる。上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接する、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタを有し、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第1の酸化絶縁膜上に位置する。

(もっと読む)

半導体装置

【課題】カラーフィルタに含まれる不純物による汚染の問題を解決する。

【解決手段】薄膜トランジスタと、薄膜トランジスタに電気的に接続されるソース電極及

びドレイン電極と、薄膜トランジスタ、ソース電極及びドレイン電極上の第1の絶縁膜と

、第1の絶縁膜上のカラーフィルタと、カラーフィルタ上の第2の絶縁膜と、第2の絶縁

膜上の画素電極とを有し、第1の絶縁膜は窒化シリコンを有し、カラーフィルタは第1の

開口部を有し、第2の絶縁膜は第2の開口部を有し、第2の開口部は第1の開口部の内側

に設けられ、画素電極は、第1の開口部及び第2の開口部を介してソース電極及びドレイ

ン電極の一方に電気的に接続され、カラーフィルタは、画素電極、ソース電極及びドレイ

ン電極に接触しない。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】トランジスタの作製工程において、酸化物半導体層、ソース電極層、ドレイン電極層、ゲート絶縁膜、ゲート電極層、酸化アルミニウム膜を順に作成した後、酸化物半導体層および酸化アルミニウム膜に対して熱処理を行うことで、水素原子を含む不純物が除去され、かつ、化学量論比を超える酸素を含む領域を有する酸化物半導体層を形成する。また、酸化アルミニウム膜を形成することにより、該トランジスタを有する半導体装置や電子機器の作製工程での熱処理でも大気から水や水素が酸化物半導体層に侵入し、拡散することを防止することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置

【課題】金属酸化物中の酸素欠損を低減し、電気的特性の安定した半導体装置を提供することを目的の一とする。

【解決手段】ゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の金属酸化物膜と、第1の金属酸化物膜に接して設けられたソース電極及びドレイン電極と、ソース電極及びドレイン電極上に設けられたパッシベーション膜と、を有し、パッシベーション膜は、第1の絶縁膜と、第2の金属酸化物膜と、第2の絶縁膜とが順に積層された半導体装置である。

(もっと読む)

電界効果トランジスタおよびそれを用いたメモリおよび半導体回路

【課題】微細化した半導体集積回路において用いられる、オフ電流の小さな電界効果トランジスタ(FET)を提供する。

【解決手段】絶縁表面に略垂直に形成された厚さが1nm以上30nm以下の薄片状の酸化物半導体と、前記酸化物半導体を覆って形成されたゲート絶縁膜と、前記ゲート絶縁膜を覆って形成されたストライプ状の幅10nm以上100nm以下のゲートを有する電界効果トランジスタ。この構成では、薄片状の酸化物半導体の三方の面をゲートが覆うこととなるため、ソース、ドレインから注入される電子を効率的に排除し、ソースとドレインの間をほぼ空乏化領域とでき、オフ電流を低減できる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を用いた半導体装置であるトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させる。具体的には、酸化物半導体膜を用いたトランジスタの下地膜または保護膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

(もっと読む)

記憶回路、記憶装置、信号処理回路

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶回路の提供、消費電力の低減可能な信号処理回路を提供する。

【解決手段】記憶回路は、トランジスタと、容量素子と、第1の演算回路と、第2の演算回路と、第3の演算回路と、スイッチと、を有し、第1の演算回路の出力端子は、第2の演算回路の入力端子と電気的に接続され、第2の演算回路の入力端子は、スイッチを介して第3の演算回路の出力端子と電気的に接続され、第2の演算回路の出力端子は、第1の演算回路の入力端子と電気的に接続され、第1の演算回路の入力端子は、トランジスタのソース及びドレインの一方と電気的に接続され、トランジスタのソース及びドレインの他方は、容量素子の一対の電極のうちの一方、及び第3の演算回路の入力端子と電気的に接続され、トランジスタのチャネルは酸化物半導体層に形成される。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、ゲート電極を形成後、インライン装置にて、酸化アルミニウム膜と酸化シリコン膜と酸化物半導体膜を大気暴露することなく連続的に形成し、さらに同インライン装置にて加熱および酸素添加処理を行い、他の酸化アルミニウム膜でトランジスタを覆った後、熱処理を行うことで、水素原子を含む不純物が除去され、且つ、化学量論比を超える酸素を含む領域を有する酸化物半導体膜を形成する。該酸化物半導体膜を用いたトランジスタは、バイアス−熱ストレス試験(BT)試験前後においてもトランジスタのしきい値電圧の変化量が低減されており、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置および該半導体装置の作製方法

【課題】良好な電気特性を有する半導体装置および該半導体装置の作製方法を提供する。

【解決手段】ゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に水素透過膜を形成し、水素透過膜上に水素捕縛膜を形成し、加熱処理を行って、酸化物半導体膜から水素を脱離させ、酸化物半導体膜の一部に接するソース電極およびドレイン電極を形成し、水素捕縛膜の露出されている部分を除去して、水素透過膜のチャネル保護膜を形成する半導体装置の作製方法である。また、該作製方法で作製された半導体装置である。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜と接して形成される絶縁膜へのインジウムの拡散を抑え、また、酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜と接する絶縁膜との界面特性を良好にし、安定した電気的特性を有し、信頼性の高い半導体装置を提供する。

【解決手段】インジウムを含む酸化物半導体膜において、表面のインジウム濃度を低減させることによって、酸化物半導体膜の上に接して形成される絶縁膜へのインジウムの拡散を防ぐ。また、さらに酸化物半導体膜表面のインジウム濃度を低減させることによって、表面にインジウムを実質的に含まない層を形成することができ、この層を絶縁膜の一部とすることにより、酸化物半導体膜と、該酸化物半導体膜と接する絶縁膜との界面特性を良好にする。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、少なくとも酸化物半導体膜中に希ガスイオンを注入する注入工程を行い、減圧下、窒素雰囲気下、又は希ガス雰囲気下において、希ガスイオンを注入した酸化物半導体膜に加熱工程を行って希ガスイオンを注入した酸化物半導体膜中に含まれる水素若しくは水を放出させ、酸化物半導体膜を高純度化する。

(もっと読む)

微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子

【課題】10nm程度の溝を有する微細構造物を安価で簡便かつ高精度に作製可能な微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子を提供すること。

【解決手段】本発明の微細構造物の製造方法は、トップダウン形成法により、基板上に少なくとも2つの凸状の形状からなる第1の構造体を形成する第1の構造体形成工程と、ボトムアップ形成法により、前記第1の構造体が形成された基板上に形成材料を堆積させ、隣接する前記第1の構造体の中間位置に凹状の溝を有する第2の構造体を形成する第2の構造体形成工程と、を含むことを特徴とする。

(もっと読む)

スパッタリングターゲット、酸化物半導体薄膜及びそれらの製造方法

【課題】スパッタリング法を用いて酸化物半導体膜を成膜する際に発生する異常放電を抑制し、酸化物半導体膜を安定かつ再現性よく得ることができるスパッタリングターゲットを提供する。

【解決手段】In、Ga、及びAlの割合が下記式(1)及び(2)の原子比となるように原料化合物を混合後、成形体とする工程、及び、前記成形体を、800℃から焼結温度までの温度範囲を0.1℃/分〜2℃/分の昇温速度で昇温した後、1450℃〜1650℃に10〜50時間保持することにより焼結する工程を含むことを特徴とする焼結体の製造方法。

Ga/(In+Ga+Al)=0.01〜0.08 (1)

Al/(In+Ga+Al)=0.0001〜0.03 (2)

(もっと読む)

半導体装置

【課題】製造時以外にデータの追記が可能であり、書き換えによる偽造等を防止可能な不揮発の記憶装置及びそれを有する半導体装置を提供することを課題とする。また、信頼性が高く、安価な不揮発の記憶装置及び半導体装置の提供を課題とする。

【解決手段】絶縁表面上に形成される第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層に挟持される第1の絶縁層と、第1の導電層の一部を覆う第2の絶縁層とを有し、第1の絶縁層は第1の導電層の端部、絶縁表面、及び第2の絶縁層を覆うことを特徴とする記憶装置である。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

酸化物半導体膜、半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を活性層に用いるトランジスタにおいて、チャネル領域と隣接するソース領域およびドレイン領域に微小な空洞を設ける。酸化物半導体膜に形成されるソース領域およびドレイン領域に微小な空洞を設けることによって、微小な空洞に酸化物半導体膜のチャネル領域に含まれる水素を捕獲させることができる。

(もっと読む)

記憶装置及び電子機器

【課題】メモリセル毎に選択動作を行う。

【解決手段】装置は、第1のメモリセルと、第1のメモリセルと同じ行に設けられた第2のメモリセルと、を具備し、前記第1及び第2のメモリセルのそれぞれは、第1のゲート及び第2のゲートを有し、オン状態又はオフ状態になることにより、メモリセルにおける少なくともデータの書き込み及びデータの保持を制御する電界効果トランジスタを備え、前記第1のメモリセル及び前記第2のメモリセルが備える前記電界効果トランジスタの前記第1のゲートのそれぞれに電気的に接続される行選択線と、前記第1のメモリセルが備える前記電界効果トランジスタの前記第2のゲートに電気的に接続される第1の列選択線と、前記第2のメモリセルが備える前記電界効果トランジスタの前記第2のゲートに電気的に接続される第2の列選択線と、をさらに具備する。

(もっと読む)

141 - 160 / 737

[ Back to top ]