Fターム[5F110BB05]の内容

Fターム[5F110BB05]の下位に属するFターム

Fターム[5F110BB05]に分類される特許

721 - 737 / 737

結晶化装置、結晶化方法、回折格子型の位相シフタおよび反射回折格子型の位相シフタ

【課題】 比較的安価に製造が可能で且つ色収差が実質的に発生することのない位相シフタ。

【解決手段】 位相シフタ(1)は、第1の格子ピッチ(p)を有する一群の反射型回折格子(10)と、これらの一群の反射型回折格子の中に形成されて第1の格子ピッチと異なる第2の格子ピッチ(p’)を有する1つの反射型回折格子(11)とを備えている。第2の格子ピッチは第1の格子ピッチの約半分に設定され、回折格子はブレーズド格子である。また、位相シフタは、たとえばレプリカ生成技術により形成されている。

(もっと読む)

埋め込み酸化物層の圧縮材料に導入される伸張性のストレインシリコンを備えた半導体デバイス

シリコンゲルマニウム層の形成を必要としないで、高速性のシリコンオンインシュレータ(SOI)とストレインドシリコン技術を備えた半導体デバイスが提供される。圧縮材料(22)層はSOI半導体基板(20)に形成され、上部のシリコン層(21)の歪みをもたらす。圧縮材料層には、酸窒化シリコン、リン、窒化シリコン、及びホウ素/リンドープの石英ガラスが含まれる。  (もっと読む)

(もっと読む)

成膜方法、無機物膜、電子部品および電子機器

【課題】本発明の目的は、特性に優れる無機物膜を形成し得る成膜方法、かかる成膜方法により形成された無機物膜、この無機物膜を備える電子部品および電子機器を提供すること。

【解決手段】本発明の成膜方法は、基材5上に、無機物膜8の構成材料である膜材料81’と膜材料以外の部分とで構成される化合物を膜材料前駆体80として用いて、化学的気相成膜法により無機物膜8を形成する成膜方法であり、膜材料前駆体80を収納した収納部7と、基材5とを空間を介して対向させた状態で、膜材料前駆体80をガス状またはミスト状として、基材5に向かって供給し、前記空間において、ガス状またはミスト状の膜材料前駆体81を加熱して、基材5に到達する前に、その少なくとも一部を熱分解させて、膜材料以外の部分を分解・除去することにより、膜材料81’を前記基材に到達させて無機物膜8を形成させるものである。

(もっと読む)

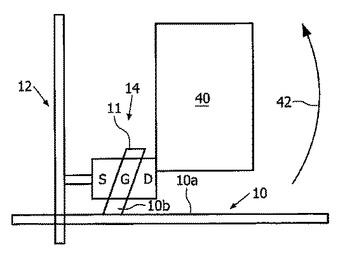

可撓性基板を有するアクティブマトリクスアレー装置

アクティブマトリクスアレー装置は、行列状の装置素子の配列を有する。各行導体(10)は、細長い行ライン(10a)と、該行ラインから延伸する複数の突出部(10b)とを有し、各突出部(10b)は、それぞれの装置素子の薄膜トランジスタ(11)のゲート導体を定形する部分を有する。装置は、少なくとも前記行ライン(10a)と平行な軸の周囲で変形できるように適合され、各ゲート突出部の前記部分は、前記行ライン方向に対して非垂直な方向に延伸する。この非垂直な方向により、装置の変形によって生じるTFT特性の変化が抑制される。  (もっと読む)

(もっと読む)

電界効果トランジスタ

電界効果トランジスタは、50nm以下の膜厚を有し、0℃以上で強磁性を示すBa系Mn酸化物からなる強磁性層と、誘電体または強誘電体からなる誘電体層とが接合されてなっている。これにより、0℃以上で、磁性、電気輸送特性および/または磁気抵抗効果を制御することができる。  (もっと読む)

(もっと読む)

2つの制御領域を有する集積された電界効果トランジスタ、その使用、およびその製造方法

本発明は、特に、SOI技術およびサリサイド技術により、ダブルゲート・トランジスタ(10)として生成される、電界効果トランジスタ(10)に関する。トランジスタ(10)は、5ボルトよりも高いまたは9ボルトよりもさらに高いターンオン電圧に適し、非常に小さなチップ表面のみを必要とする。トランジスタ(10)は基板領域(14)を有する。基板領域(14)は、2つの電極領域(16、18)と、2つの電気的に絶縁性の絶縁層(100、102)であって、基板領域(14)の対向する面に配置され、制御領域(20、22)に隣接する、絶縁層と、少なくとも1つの電気的に絶縁性の領域(12、110)と、導電性の接続領域(28)、または、1つの電極領域(16)と該基板領域(14)との間の導電性の接続領域の部分(230)とに囲まれる。  (もっと読む)

(もっと読む)

分離トレンチ

分離トレンチ(209)をウェハ(201)に形成するプロセスである。このプロセスでは、(例えば、異方性堆積法により)第1誘電体材料(307)をトレンチ(209)の中に堆積させ、次に第2誘電体材料(309)を(例えば、異方性堆積法により)トレンチ(209)内の第1誘電体材料(307)を覆うように堆積させる。第3材料(501)をトレンチ(209)内に、かつ第2誘電体材料(309)の上に堆積させる。第2材料(309)及び第3材料(501)の内の一方の材料は、他方の材料をエッチングしないように選択的にエッチングすることができる。一の例では、第1材料(307)は第2材料(309)よりも小さい誘電率を有する。  (もっと読む)

(もっと読む)

金属トランジスターデバイス

本発明はトランジスターデバイスのチャネル領域の絶縁基板上に形成される金属薄膜あるいは複合金属層が含まれるデプレッションあるいはエンハンスメントモードの金属トランジスターに関する。

(もっと読む)

(もっと読む)

アレイ状に配置された垂直型カーボン・ナノチューブ電界効果トランジスタを製造する方法、並びに、それによって形成された電界効果トランジスタ及びアレイ

【課題】 カーボン・ナノチューブ電界効果トランジスタと、カーボン・ナノチューブ電界効果トランジスタのアレイと、デバイス構造体とを製造するための方法、及び、該方法によって形成されたデバイス構造体のアレイを提供する。

【解決手段】 本方法は、ゲート電極層と、各々がソース/ドレイン・コンタクトと電気的に結合された触媒パッドとを含む積層構造体を形成することを含む。ゲート電極層は多数のゲート電極に分割され、少なくとも1つの半導体カーボン・ナノチューブが、化学気相堆積プロセスによって触媒パッドの各々の上に合成される。完成したデバイス構造体は、ゲート誘電体によって覆われた側壁を有するゲート電極と、該ゲート電極の該側壁に隣接する少なくとも1つの半導体カーボン・ナノチューブとを含む。ソース/ドレイン・コンタクトを半導体カーボン・ナノチューブの両端と電気的に結合することによって、デバイス構造体が完成する。多数のデバイス構造体は、メモリ回路又は論理回路のいずれかとして構成することができる。

(もっと読む)

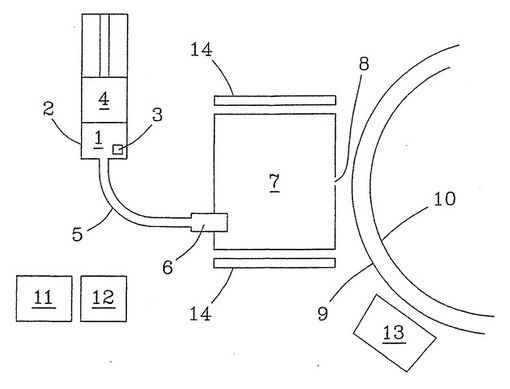

連続供給機能を有する流体源から基板上に有機薄膜をコーティングする方法および装置

非重合化合物と流体担体の混合物を得ることによって基板上に非重合化合物の薄膜をコーティングする方法。この混合物(1)は次いで、非重合化合物および流体担体の実質的に全部をガス状に転換するのに十分な内部温度を有する加熱された蒸発ボックス(7)の内部につぎ込まれる。非重合化合物と流体担体は次いで、蒸発ボックス内の出口スリット(8)を介して蒸発ボックスから取り出される。非重合化合物が凝縮する基板が、出口スリットに隣接して、真空状態に維持されている。基板(10)は、たとえばウェブ・ローラ上を移動し、それによって非重合化合物の連続的なコーティングを基板にコーティングするのが可能になる。

(もっと読む)

(もっと読む)

絶縁構造部上の半導体チャンネル

半導体装置基板上に貫通誘電体層を形成するステップと、貫通誘電体層の上部にトレンチ誘電体層を形成するステップと、貫通誘電体層を露出させるため、トレンチ誘電体層を貫通する溝を形成するステップと、基板を露出させるため、前記溝内の貫通誘電体層に貫通孔を形成するステップと、溝内および前記貫通孔内に半導体材料を形成するステップと、を有する方法を示した。装置基板と、該装置基板の表面に形成された誘電体層と、誘電体層上に形成された、装置基板と相間する結晶構造を有する装置基部と、を有する装置を示した。  (もっと読む)

(もっと読む)

縦型ナノトランジスタおよび該トランジスタの製造方法ならびにメモリ装置

本発明の課題は、機械的応力に対し良好な耐性をもち、その製造が公知の従来技術よりも煩雑でない縦型ナノトランジスタを提供することである。本発明によればこの課題は、以下の特徴を備えた縦型ナノトランジスタによって解決される。すなわちソースコンタクトと、ドレインコンタクトと、ゲート領域と、ソースコンタクトとドレインコンタクトの間に配置され半導体特性をもつ円筒状のチャネル領域が設けられており、この円筒状チャネル領域は絶縁性フレキシブル基板に埋め込まれており、この領域は、ゲート領域とチャネル領域上部が同軸構造を成すよう、フレキシブル基板上およびチャネル領域上部の金属層により形成されたゲート領域により取り囲まれている。さらにソースコンタクトと半導体特性をもつチャネル領域とドレインコンタクトは縦方向に配置されていて、ソースコンタクトとドレインコンタクトと半導体特性をもつチャネル領域に対向するゲート領域と、基板の上側および下側は電気的に絶縁性の部材を有している。メモリ装置は多数のこの種の縦型ナノトランジスタから成る。本発明はこの種のトランジスタの製造方法にも関する。  (もっと読む)

(もっと読む)

アセン−チオフェン半導体

有機半導体として有用であるアセン−チオフェン化合物が開示されている。有機薄膜トランジスタ中の半導体層として本化合物を用いた時、本化合物は、ペンタセンに匹敵する電荷キャリア移動度および電流オン/オフ比のようなデバイス特性を示す。本発明の少なくとも1種の化合物を含む半導体デバイスならびに薄膜トランジスタまたはトランジスタアレーおよびエレクトロルミネセントランプなどの半導体デバイスを含む物品も記載されている。  (もっと読む)

(もっと読む)

薄膜トランジスタの封止方法

ゲート電極と、ゲート誘電体と、ソースおよびドレイン電極と、半導体層とを含む薄膜トランジスタを提供する工程と、封止材料をアパーチャマスクのパターンを通して前記半導体層の少なくとも一部の上に蒸着する工程とを含む、薄膜トランジスタの封止方法。  (もっと読む)

(もっと読む)

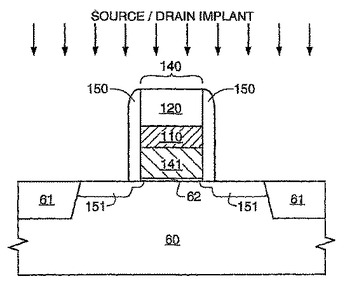

集積化金属珪化物ゲート電極を有するトランジスタの形成方法

集積化した金属珪化物トランジスタゲート電極を有するトランジスタを半導体アセンブリ内に形成する方法を提供する。トランジスタゲートは部分的に、金属を溝内に存在させた状態でエピタキシャルシリコンと反応させることにより製造する。前記溝内で前記金属珪化物上にトランジスタゲート分離キャップ層を形成する。任意ではあるが溝スペーサを設けて所定の製造処理の臨界的な寸法上の制約を低減させ、従って、形状寸法が臨界的な寸法よりも小さいトランジスタを形成しうるようにすることができる。  (もっと読む)

(もっと読む)

自己組織化単分子層を含む電子デバイスおよびこれを製造する方法

【課題】 電子特性が向上した分子層を有する電子デバイスを提供すること。

【解決手段】 電子デバイスは、ソース領域およびドレイン領域と、ソース領域およびドレイン領域に隣接して配置され、少なくとも1つの共役分子を含む自己組織化単分子層と、自己組織化単分子層に隣接した導電性基板と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 より優れたソフトエラー耐性を有するSOI基板を用いた高信頼性のCMOS・SRAMセルを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 SOI基板の表面半導体層上にゲート絶縁膜を介して形成されたゲート電極と、該ゲート電極の両側の表面半導体層に形成された第1導電型ソース/ドレイン領域とから構成される半導体装置であって、前記第1導電型ソース/ドレイン領域の双方又は一方に接して第2導電型引出拡散層が形成され、少なくとも前記第1導電型ソース/ドレイン領域上から第2導電型引出拡散層上にわたってシリサイド層が形成されており、シリサイド層に接地電位が与えられてなる半導体装置。

(もっと読む)

721 - 737 / 737

[ Back to top ]