Fターム[5F110DD06]の内容

Fターム[5F110DD06]の下位に属するFターム

Fターム[5F110DD06]に分類される特許

281 - 298 / 298

半導体装置およびその作製方法

【課題】液晶表示装置やEL発光装置などの半導体装置において、今後のさらなる高精細化(画素数の増大)、小型化に伴う各表示画素ピッチの微細化、及び画素部を駆動する駆動回路の集積化を進められるように、複数の素子を限られた面積に形成し、素子が占める面積を縮小して集積することを課題とする。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して複雑なゲート電極を形成する。また、マスクを変更するだけで、工程数を増やすことなく、同一基板上に上記マルチゲート構造であるトップゲート型TFTとシングルゲート構造であるトップゲート型TFTを形成することができる。

(もっと読む)

薄膜トランジスタ搭載パネル及びその製造方法

【課題】 レーザーアニールによる熱によっても、プラスチック基板上に形成された薄膜トランジスタが、そのプラスチック基板から剥離し難い構造からなる薄膜トランジスタ搭載パネル及びその製造方法を提供する。

【解決手段】 プラスチック基板上に形成されたアモルファスシリコンをレーザーアニールしてポリシリコン薄膜を形成し、そのポリシリコン薄膜の所定領域に不純物イオンを添加した後にレーザーアニールによって熱活性化してなる薄膜トランジスタ搭載パネルであって、プラスチック基板とポリシリコン薄膜との間に、レーザーアニール時にプラスチック基板側に伝わる熱を緩衝する熱緩衝膜を形成する。その熱緩衝膜の厚さをT(μm)、熱緩衝膜の材料の比熱をC(J/(g・K))、熱緩衝膜の材料の比重をρ(g/cm3)、熱緩衝膜の材料の熱伝導率をκ(W/(m・K))としたとき、T≧1.02×κ/(C×ρ)の関係を満たす。

(もっと読む)

薄膜トランジスタの作製方法及び薄膜トランジスタ

【課題】実質的なチャネル長の長さを短くし、半導体装置を微細化することができる半導体装置及びその作製方法を提供する。また、実質的なチャネル長の長さを短くすることによってゲート容量を減少させることができ、半導体装置の高速動作及び高性能化を実現できる半導体装置及び、その作製方法を提供する。また、製造工程を簡略化することができる作製方法を提供することを課題とする。

【解決手段】絶縁表面を有する基板上に形成されたる島状半導体膜と、島状半導体膜上に形成されたゲート電極とを有する半導体装置であって、ゲート電極は高密度プラズマにより表面を酸化されることによって、スリミング化し、実質的なチャネル長を短くしている。

(もっと読む)

結晶性Si層形成基板の製造方法、結晶性Si層形成基板及び結晶性Siデバイス

プラスチック基板上にアモルファスSi層を形成し、前記アモルファスSi層をレーザ照射により結晶化して得られる結晶性Si層形成基板の製造方法において、前記レーザの発振波長の光に対する前記プラスチック基板の透過率が30〜100%であることを特徴とする方法。 (もっと読む)

感熱性材料を基材に転写するための方法およびドナー要素

基材と、誘電体を伴う半導体材料の転写層とを含んでなる熱画像形成可能なドナー要素を加熱するステップを含んでなる、熱的方法によってパターン形成された半導体−誘電材料を基材上に形成せしめる方法が開示される。このドナーは、受容体上に形成されるべき所望のパターンのポジ画像で露光され、それによって半導体および誘電材料の層の露光部分が同時に転写されて、半導体および誘電材料の所望のパターンが受容体上に形成される。半導体材料をパターン形成せしめて薄膜トランジスタを形成せしめることができる。この方法は、発光ポリマーまたは小分子と電荷注入層とのパターン形成に使用して、光電性有機電子デバイスの発光ディスプレイを形成せしめることもできる。この方法に使用されるドナー要素も開示される。薄膜トランジスタおよびこの方法に使用されるドナー要素の形成方法も開示される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】閾値のばらつきが低減された絶縁ゲート電界効果型トランジスタをより簡易な工程で製造できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、絶縁ゲート電界効果型トランジスタ20の第1の不純物領域26aを貫通し、前記支持基板6に到達する第1コンタクト層36と、該絶縁ゲート電界効果型トランジスタ20の第2不純物領域29bに到達する第2コンタクト層38と、を形成すること、を含み、前記第1コンタクト層36および前記第2コンタクト層38の形成は、前記層間絶縁層30の上方に、第1開口52と該第1開口52と比して小さい第2開口54とを有するマスク層50を形成すること、前記マスク層50をマスクとして第1のエッチングと、該第1のエッチングとは条件が異なる第2のエッチングとを行うこと、を含む。

(もっと読む)

有機薄膜トランジスタ、それを備えた表示装置および有機薄膜トランジスタの製造方法。

【課題】 電極用のシャドウマスクの位置合わせが容易な構造からなる有機薄膜トランジスタを提供する。

【解決手段】 有機薄膜トランジスタ10は、基板1と、ゲート電極2と、ゲート絶縁膜3と、有機半導体膜4と、ソース電極5と、ドレイン電極6とを備える。基板1は、その表面が凹凸化されており、平面1A,1Bを有する。平面1A,1Bは、基板1の法線方向において相互に異なる位置に配置される。ゲート電極2は、基板1の裏面に形成される。ゲート絶縁膜3は、基板1の平面1A,1B上に形成される。ソース電極5は、ゲート絶縁膜3を介して基板1の平面1A上に形成される。ドレイン電極6は、ゲート絶縁膜3を介して基板1の平面1B上に形成される。そして、ソース電極5およびドレイン電極6は、相互に異なる材料からなる。

(もっと読む)

転写方法、転写物の製造方法、回路基板の製造方法、電気光学装置及び電子機器

【課題】 転写不良を低減し、製品歩留まりを向上させることが可能な転写技術を提供する。

【解決手段】 1以上の被転写体10が形成されている第1基材1上の転写対象領域を取り囲む囲み手段13を形成する工程と、第1基材1と第2基材2とを、囲み手段13により取り囲まれた転写対象領域に接着剤を充填することにより形成される接着層3を介して接合する工程と、囲み手段13を除去する工程と、第1基材1と第2基材2とを離隔して、接着層3により第2基材2に接着された被転写体10を当該第2基材2に転写する工程と、を備えた被転写体10の転写方法により上記課題を解決する。

(もっと読む)

ナノチューブ/ナノワイヤFETのための自己整合プロセス

【課題】 ナノチューブ及びナノワイヤのような一次元ナノ構造体を含むCMOSデバイスを製造するための自己整合プロセスを提供すること。

【解決手段】 半導体構造体は、少なくとも1つのゲート領域が上に配置され、少なくとも1つのゲート領域が少なくとも1つの一次元ナノ構造体の層を含む、基板と、基板の表面上に配置され、少なくとも1つの一次元ナノ構造体の層の縁と整合される、金属カーバイド・コンタクトと、を含む。

(もっと読む)

半導体装置の作製方法

【課題】水分や酸素の透過による劣化を抑えることが可能な半導体装置、例えば、プラスチック基板上に形成された有機発光素子を有する発光装置、プラスチック基板を用いた液晶表示装置の提供を課題とする。

【解決手段】本発明は、ガラス基板または石英基板上に形成した素子(TFTや、有機化合物を含む発光素子や、液晶を有する素子や、メモリー素子や、薄膜ダイオードや、シリコンのPIN接合からなる光電変換素子や、シリコン抵抗素子など)を含む被剥離層12を基板から剥離した後、熱伝導性の高いプラスチック基板10に転写する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】 ソース・ドレインの界面形状とショットキー障壁高さ、電極比抵抗を同時に制御可能なショットキートランジスタを提供する。

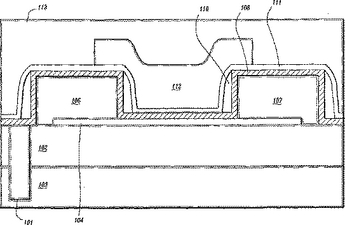

【解決手段】 チャネル領域を構成する半導体領域112と、半導体領域112上にゲート絶縁膜113を介して形成されたゲート電極114と、ゲート電極114に対応して半導体領域112の両側に形成されたソース・ドレイン電極とを備えたMIS型電界効果トランジスタにおいて、ソース・ドレイン電極は、半導体領域112を挟んで形成され、且つキャリアがトンネル可能な厚さに形成されたトンネル絶縁膜116と、トンネル絶縁膜に接して形成された第1の金属層117と、第1の金属層117に接して形成され、第1の金属層117よりも小さい比抵抗を持つ第2の金属層118と、をチャネル長方向に積層してなる。

(もっと読む)

アクティブマトリクス基板の製造方法,アクティブマトリクス基板および液晶表示装置

【課題】 本発明の目的の一つは、新規な薄膜デバイスの転写技術を用いてアクティブマトリクス基板を形成する際に、問題となる製造上の不都合を排して、アクティブマトリクス基板の現実の製造を可能とすることである。

【解決手段】 転写元の基板上に薄膜トランジスタならびに画素電極を形成するに際し、薄膜トランジスタを形成する前に、画素電極(7000)を形成しておく。これにより、デバイスを転写体(7700)に転写した後、転写元基板を離脱させると、画素電極(7000)の表面が自動的に露出することになる。この部分(7000)が液晶(460)への電圧印加を可能とする。

(もっと読む)

液晶パネル用基板及び液晶パネル

【課題】アモルファスシリコンTFTを用いた画素領域に、多結晶シリコンTFTを用いたドライバ領域とを一枚の基板に形成することができる液晶パネル用基板及び液晶パネル並びにその製造方法を提供する。

【解決手段】第1の基板10上の画素領域12に、アモルファスシリコンTFT30を形成し、端子となる部分を露出させて第1の電極露出部22とする。第2の基板100を用いて、駆動回路14,16の能動素子である多結晶シリコンTFTと、それに接続された第2の電極配線群を含む被転写層140を形成し、端子となる部分を露出させて第2の電極露出部141とする。この第1,第2の電極露出部22,141が導通する位置関係にて、第1の基板10上に被転写層140を接合した後、被転写層140より第2の基板100を除去する。

(もっと読む)

自己整合型ナノチューブ電界効果トランジスタおよびこれを製造する方法

【課題】 自己整合型カーボン・ナノチューブ電界効果トランジスタ半導体デバイスを提供する。

【解決手段】 基板(102)上に堆積したカーボン・ナノチューブ(104)と、カーボン・ナノチューブ(104)の第1の端部および第2の端部にそれぞれ形成されたソースおよびドレイン(106〜107)と、誘電体膜(111)によってカーボン・ナノチューブから分離された、実質的にカーボン・ナノチューブ(104)の一部の上に形成されたゲート(112)とを備える。  (もっと読む)

(もっと読む)

イオン注入および熱アニーリングによるシリコンまたはシリコン・オン・インシュレータ基板上の緩和SiGe層

【課題】Siまたはシリコン・オン・インシュレータ(SOI)基板上に、薄い(300nm未満)歪み緩和Si1-xGexバッファ層を形成する方法を提供する。

【解決手段】これらのバッファ層は、歪みを緩和し、著しく平坦な表面を有し、貫通転位(TD)密度が低い、すなわち106cm-2未満である、一様な分布の不整合転位を有する。この手法は、擬似格子整合またはほぼ擬似格子整合したSi1-xGex層すなわち不整合転位が存在しない層を成長させることから開始し、次いでHeまたは他の軽元素を注入し、続いてアニーリングを行って、実質的な歪み緩和を得る。この方法によって機能する極めて有効な歪み緩和機構は、Si/Si1-xGex界面の下に、Si(001)表面に平行な、Heが誘導した小板(泡でない)における転位核化である。  (もっと読む)

(もっと読む)

集積半導体構造の形成方法(二重SIMOXハイブリッド配向技術(HOT)基板)

【課題】異なる配向の結晶を有する平坦なハイブリッド配向半導体オン・インシュレータ(SOI)基板の形成に、酸素注入(SIMOX)法による分離を提供することにより、最適の性能をもたらす配向の結晶上にデバイスを製造する方法を提供する。

【解決手段】薄い絶縁層によって第2の結晶配向を有する上部半導体層から分離された、第1の結晶配向を有する下部半導体層を有する基板を選択する工程と、選択された領域の上部半導体層を、第1の結晶配向を有するエピタキシャル成長半導体で置換する工程と、次いでイオン注入およびアニーリング法を用いて、(i)エピタキシャル成長半導体材料内に埋め込み絶縁領域を形成し、(ii)上部半導体層の下にある絶縁層を厚くする工程と、これにより、異なる結晶配向を有する2つの半導体材料が、実質的に同一厚みを有し両方とも共通の埋め込み絶縁体層上に配置されたハイブリッド配向基板を形成する工程と、を含む。

(もっと読む)

可撓性基板を有するアクティブマトリクスアレー装置

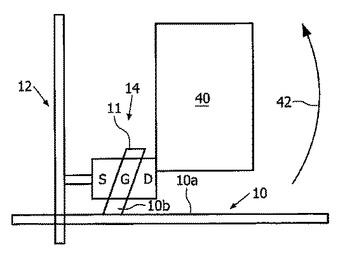

アクティブマトリクスアレー装置は、行列状の装置素子の配列を有する。各行導体(10)は、細長い行ライン(10a)と、該行ラインから延伸する複数の突出部(10b)とを有し、各突出部(10b)は、それぞれの装置素子の薄膜トランジスタ(11)のゲート導体を定形する部分を有する。装置は、少なくとも前記行ライン(10a)と平行な軸の周囲で変形できるように適合され、各ゲート突出部の前記部分は、前記行ライン方向に対して非垂直な方向に延伸する。この非垂直な方向により、装置の変形によって生じるTFT特性の変化が抑制される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 SOI基板を用いてより高性能なMISFETを実現する。

【解決手段】 SOI基板を用いた半導体装置であって、第1の絶縁膜11上に形成された第1の半導体層12と、第1の半導体層12の主面上の一部に第2の絶縁膜13を介して形成された、第1の半導体層12とは面方位が異なる第2の半導体層14と、第1の半導体層12の主面に形成された第1導電型のMISFETと、第2の半導体層14の主面に形成された第2導電型のMISFETとを備えた。

(もっと読む)

281 - 298 / 298

[ Back to top ]