Fターム[5F110DD06]の内容

Fターム[5F110DD06]の下位に属するFターム

Fターム[5F110DD06]に分類される特許

121 - 140 / 298

薄膜トランジスタ及びその製造方法並びに表示基板

【課題】本発明の一つの目的は、金属イオンの拡散によって半導体パターンの長さが短くなることを防止する薄膜トランジスタ及びその製造方法並びに表示基板を提供する。

【解決手段】薄膜トランジスタは、ソース領域、ドレーン領域、チャンネル領域及び拡散抑制部を含む半導体パターンと、半導体パターン上に形成された第1絶縁膜パターンと、半導体パターンに対応して第1絶縁膜パターン上に形成されたゲート電極と、ゲート電極上に形成された第2絶縁膜パターンと、第2絶縁膜パターン上に形成され、半導体パターンのソース領域及びドレーン領域がそれぞれ接続されるソース電極及びドレーン電極とが設けられ、拡散抑制部はソース電極又はドレーン電極からチャンネル領域へ金属イオンが拡散することを抑制する。

(もっと読む)

微結晶半導体膜及び薄膜トランジスタの作製方法

【課題】結晶性の高い微結晶半導体膜を作製する。また、電気特性が優れ、信頼性の高い薄膜トランジスタ、及びそれを有する表示装置を生産性高く作製する。

【解決手段】プラズマCVD装置の処理室に設けられた複数の凸部を備える電極から、シリコンまたはゲルマニウムを含む堆積性気体を導入し、高周波電力を供給し、グロー放電を発生させて、基板上に結晶粒子を形成し、該結晶粒子上にプラズマCVD法により微結晶半導体膜を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】画素部の開口率を高くしながら、駆動回路部の特性を向上させた半導体装置を提供することを課題とする。または、消費電力の低い半導体装置を提供することを課題とする。または、しきい値電圧を制御できる半導体装置を提供することを課題とする。

【解決手段】絶縁面を有する基板と、基板上に設けられた画素部と、画素部を駆動する駆動回路の少なくとも一部を有し、画素部を構成するトランジスタおよび駆動回路を構成するトランジスタは、トップゲートボトムコンタクト型のトランジスタであって、画素部においては、電極および半導体層が透光性を有し、駆動回路における電極は、画素部のトランジスタが有するいずれの電極よりも低抵抗である半導体装置である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上させる。

【解決手段】同一基板上に第1の薄膜トランジスタを有する駆動回路及び第2の薄膜トランジスタを有する画素を有し、前記第1の薄膜トランジスタは、第1のゲート電極層と、ゲート絶縁層と、第1の酸化物半導体層と、第1の酸化物導電層及び第2の酸化物導電層と、前記第1の酸化物半導体層の一部に接し、且つ前記第1の酸化物導電層及び前記第2の酸化物導電層の周縁及び側面に接する酸化物絶縁層と、第1のソース電極層と、第1のドレイン電極層と、を有し、前記第2の薄膜トランジスタは、第2のゲート電極層と、第2の酸化物半導体層と、透光性を有する材料により構成された第2のソース電極層及び第2のドレイン電極層と、を有する。

(もっと読む)

有機トランジスタ

【課題】

高い移動度、大きな電流オン/オフ比を有し、保存安定性に優れた有機トランジスタを提供する。

【解決手段】

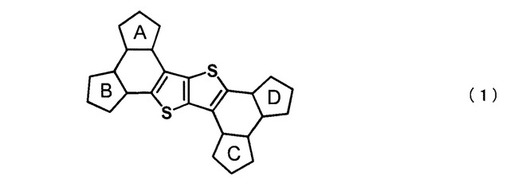

有機半導体層を有する有機トランジスタにおいて、該有機半導体層に一般式(1)で表される少なくとも1種の化合物を含有してなる有機トランジスタ。

(式中、環A〜環Dは、それぞれ独立に、置換または未置換のチオフェン環を表す。)

(もっと読む)

有機半導体トランジスタ

【課題】13,6−N−サルフィニルアセトアミドペンタセンに比べ、電荷移動度の低下が少ない有機半導体トランジスタを提供すること。

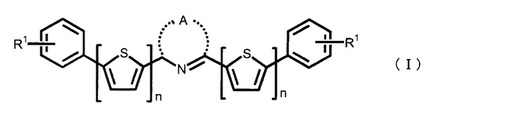

【解決手段】複数の電極と、下記一般式(I)で表される化合物を少なくとも1種含有する有機半導体層と、を備える有機半導体トランジスタ。一般式(I)中、R1は、水素原子、置換若しくは未置換の炭素数1以上20以下のアルキル基、又は置換若しくは未置換の炭素数1以上20以下のアルコキシ基を表し、Aは芳香族複素六員環を形成するための少なくとも1個の窒素原子を含む複素環残基を表し、nは1以上3以下の整数を表す。

(もっと読む)

(もっと読む)

有機半導体トランジスタ

【課題】13,6−N−サルフィニルアセトアミドペンタセンを用いた有機半導体層を備える有機半導体トランジスタに比べ、電荷移動度の低下が抑制された有機半導体トランジスタを提供する。

【解決手段】複数の電極と、下記一般式(I)で示されるフルオレン化合物を少なくとも1種含有する有機半導体層と、を備える有機半導体トランジスタ。一般式(I)中、R1は、炭素数1から6までのアルキル基を表す。R2は、炭素数1から8までのアルキル基、又は炭素数1から8までのアルコキシ基を表す。nは1から2までの整数を表す。 (もっと読む)

(もっと読む)

半導体基板の作製方法および半導体装置

【課題】炭化シリコンを含む半導体基板の新たな作製方法を提供することを目的の一とする。または、炭化シリコンを用いた半導体装置を提供することを目的の一とする。

【解決手段】炭化シリコン基板にイオンを添加することにより、炭化シリコン基板中に脆化領域を形成し、炭化シリコン基板とベース基板とを絶縁層を介して貼り合わせ、炭化シリコン基板を加熱して、脆化領域において炭化シリコン基板を分離することにより、ベース基板上に絶縁層を介して炭化シリコン層を形成し、炭化シリコン層を1000℃〜1300℃の温度で熱処理して、炭化シリコン層の欠陥を低減することにより半導体基板を作製する。または、上述のようにして形成された半導体基板を用いて半導体装置を作製する。

(もっと読む)

半導体装置、電気光学装置、電子機器

【課題】ある応力がかかっても回路全体としての動作特性が変化しない薄膜の半導体素子を実現し、これによって、動作マージンが広く大型化が容易なフレキシブルな半導体装置、電気光学装置、電子機器を提供する。

【解決手段】本発明の半導体装置は、基板100上に薄膜トランジスタ8を有し、この薄膜トランジスタ8は、基板100の湾曲に対してチャネル内のキャリアの移動度が相補的に変化する第1のチャネル領域1cおよび第2のチャネル領域1cを有している。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

背面放熱を伴う絶縁体上半導体

本発明の実施形態は、絶縁体上半導体(SOI)構造からの熱の放散を提供する。一実施形態では、集積回路を製造する方法が開示される。第1のステップでは、アクティブ回路が、SOIウエハのアクティブ層内に形成される。第2のステップでは、基板材料が、SOIウエハの背面上に配置された基板層から除去される。第3のステップでは、絶縁材料が、SOIウエハの背面から除去されて掘られた絶縁体領域を形成する。第4のステップでは、放熱層が、前記掘られた絶縁層上に堆積される。放熱層は、熱的に伝導性があり、かつ電気的に絶縁する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法並びに表示装置

【課題】非晶質シリコン薄膜をレーザーアニールして結晶性シリコン薄膜を形成する場合であっても、歩留まりやスループットの低下を抑制することができる半導体装置及びその製造方法並びに表示装置を提供する。

【解決手段】半導体装置は、絶縁性の基板11の一面側に、結晶性のシリコンからなる半導体層15を有する薄膜トランジスタTFTと、金属配線12からなる配線層LNと、が同層に設けられている。薄膜トランジスタTFTの半導体層15は、基板11の一面側に成膜された非晶質シリコン薄膜15xに対して、チャネル層となる領域上にのみ光熱変換層22をパターニング形成した後、レーザー光BMを走査して基板11全域に照射し、熱アニールを施すことにより、非晶質シリコン薄膜15xが結晶化されて形成される。

(もっと読む)

薄膜トランジスタ搭載基板、その製造方法及び画像表示装置

【課題】活性層として用いた酸化物薄膜の安定化と高品質化を実現した薄膜トランジスタをプラスチック基板上に搭載した薄膜トランジスタ搭載基板の製造方法を提供する。

【解決手段】プラスチック基板10の上又はその上方に活性層となるアモルファス酸化物薄膜13を形成する工程と、少なくとも活性層となる部分のアモルファス酸化物薄膜13に向けてパルスレーザー20を照射する工程とを少なくとも有する。パルスレーザー20の照射工程は、プラスチック基板10に該プラスチック基板のガラス転移温度以上の温度を一定時間加えず、且つアモルファス酸化物薄膜13をアモルファス相のままで所定の比抵抗に制御する工程である。

(もっと読む)

薄膜トランジスタ製造装置、酸化物半導体薄膜の製造方法、薄膜トランジスタの製造方法、酸化物半導体薄膜、薄膜トランジスタ及び発光デバイス

【課題】酸化物半導体薄膜の酸素量を精度良く制御する。

【解決手段】大気と遮断された酸化物半導体薄膜形成室20内で、基板36上に、酸化物半導体の薄膜、すなわち活性層106を形成する薄膜形成工程と、前記薄膜形成工程の中で前記薄膜を加熱する加熱工程と、前記酸化物半導体薄膜形成室20と接続され、前記大気と遮断された輸送室14内で、前記基板36上に形成した薄膜を、前記加熱工程により加熱された温度から急速冷却する冷却工程と、を有する。

(もっと読む)

薄膜トランジスタ及びその製造方法、電気光学装置、並びにセンサー

【課題】オン電流が高く、特性シフトが低減された薄膜トランジスタを提供する。

【解決手段】基板上に、活性層としてのIn、Ga、及びZnを含む酸化物半導体膜と、ゲート電極と、ゲート絶縁膜と、ソース電極と、ドレイン電極と、を有し、

前記酸化物半導体膜のモル比〔In:Ga:Zn〕を2.0−x:x:y(但し、0.0<x<2.0、0.0<y)で表したとき、前記酸化物半導体膜の膜厚方向についての前記yの分布において、前記基板に近い側の膜面、及び、前記基板から離れた側の膜面よりも、前記yが大きい領域が存在する。

(もっと読む)

新規な縮合芳香環化合物及びそれを用いた有機薄膜トランジスタ

【課題】容易に合成可能であり、酸化安定性に優れる有機化合物並びにそれを利用した有機薄膜トランジスタ及び有機薄膜発光トランジスタを提供する。

【解決手段】下記式(1)で表わされる有機薄膜トランジスタ用化合物。

[式中、R1〜R4は、それぞれ独立に、水素原子等であり、Xは、それぞれS、O、Se及びTeから選択されるいずれかの原子であり、Yは、それぞれN又はC−R5(R5は前記R1〜R4と同様の基を表す。)である。R1〜R5の隣接する2つの基は互いに連結し、炭素数6〜60の芳香族炭化水素基、又は炭素数1〜60の芳香族複素環基を形成してもよく、また、R5同士で互いに連結し、炭素数6〜60の芳香族炭化水素基、又は炭素数1〜60の芳香族複素環基を形成してもよい。]

(もっと読む)

フレキシブル半導体デバイスを高温で提供する方法およびそのフレキシブル半導体デバイス

いくつかの実施例は、半導体デバイスを提供する方法を含む。当該方法は、

(a)フレキシブル基板を提供する段階、(b)フレキシブル基板上に少なくとも1つの材料層を堆積させる段階であって、そのフレキシブル基板上の少なくとも1つの材料層の堆積は、少なくとも180℃の温度で生じる、段階、および(c)金属層とa−Si層との間に拡散バリアを提供する段階を含む。他の実施例も本願において開示される。  (もっと読む)

(もっと読む)

電界効果型トランジスタの製造方法、電界効果型トランジスタ、及び表示装置の製造方法

【課題】電界効果型トランジスタの製造工程の簡略化が図れる電界効果型トランジスタの製造方法、電界効果型トランジスタ、及び表示装置の製造方法を提供する。

【解決手段】本実施の形態のトップコンタクト型の電界効果型トランジスタ10の製造方法によれば、半導体層形成工程で形成した活性層18上に、防護層22を形成した後に、該防護層22上にフォトレジスト膜を形成して露光工程においてパターン状に露光する。そして、次の現像工程において、アルカリ性現像液を用いて、上記露光工程を経たフォトレジスト膜30を現像してレジストパターン30B’を形成すると共に、防護層22における該レジストパターン30B’から露出している領域22Aを除去して防護層22のエッチングを行なう。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

121 - 140 / 298

[ Back to top ]