Fターム[5F110EE45]の内容

Fターム[5F110EE45]に分類される特許

1,801 - 1,820 / 2,010

半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 スループットの低下を抑制しつつ、組成の異なる半導体層の結晶品質を向上させる。

【解決手段】 成膜温度がH1に設定された状態で、Si2H6ガスおよびGeH4ガスをチャンバ内に導入し、SiGe層を半導体基板1上にエピタキシャル成長させる。そして、SiGe層の成膜が終了すると、Si2H6ガスを流したまま、GeH4ガスを遮断し、Si層の膜厚の一部をSiGe層上に成膜温度H1でエピタキシャル成長させる。そして、成膜温度H1でSi層の膜厚の一部がSiGe上に成膜されると、Si2H6ガスを遮断し、チャンバ内の温度を昇温させる。そして、成膜温度がH2に達すると、Si2H6ガスをチャンバに再び導入し、Si層をSiGe層上にエピタキシャル成長させる。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体層とゲート絶縁膜との熱的反応、並びに、ゲート電極とゲート絶縁膜との熱的反応を抑制し、リーク電流が少なく、かつ、EOTが低いゲート絶縁膜を備えた半導体装置を提供する。

【解決手段】 半導体装置の製造方法は、酸化物の生成自由エネルギーがΔGSである元素を含む半導体層10上に、酸化物の生成自由エネルギーがΔGIである元素を含むゲート絶縁膜用の第1の材料20を形成し、ΔGSがΔGI以上であるような温度範囲で、水素原子または重水素原子および酸素原子を含む雰囲気中において第1の材料を熱処理することを具備している。

(もっと読む)

プレーナ型ダブルゲートトランジスタを形成する方法

シリコン層が上部窒化シリコン層(SiN)(20)とシリコンゲルマニウム層(SiGe)(14)との間に設けられ、今度はシリコンゲルマニウム層が厚い酸化膜(BOX)の上に設けられる構成のシリコン層(16)が選択的にエッチングされて、ゲート長を設定する幅を持つ積層構造が残る。サイドウォール絶縁層(28)は、シリコン層(16)の側壁を露出させながらSiGe層(16)の上に形成される。シリコン(30,32)を露出シリコン側壁(16)からエピタキシャル成長させてin−situドープシリコンソース/ドレイン領域(30,32)を形成する。窒化膜層(20)は、ソース/ドレイン領域(30,32)を上部ゲート位置の境界として使用して除去される。ソース/ドレイン領域(30,32)は誘電体(36)によって被覆される。SiGe層(14)を除去して下部ゲート位置(46)を設ける。上部及び下部ゲート位置(46)の両方に金属を充填してトランジスタ(50)の上部及び下部ゲート(50)を形成する。  (もっと読む)

(もっと読む)

半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 SOI基板を用いることなく、絶縁体上の半導体層にトランジスタを安定して形成する。

【解決手段】 第1半導体層2および第2半導体層3を半導体基板1上に形成し、第2半導体層3および第1半導体層2を深さ方向に突き抜けて半導体基板1に達するように構成された素子分離酸化膜6を素子分離領域R2に選択的に形成し、第1半導体層5の一部を露出させる開口部7を酸化防止膜5および第2半導体層3に形成し、開口部7を介してエッチングガスまたはエッチング液を第1半導体層2に接触させることにより、半導体基板1と第2半導体層3との間に空洞部9を形成し、半導体基板1および第2半導体層3の熱酸化を行うことにより、空洞部9に酸化膜10を形成し、開口部7が配置されるように構成されたソース/ドレイン層25a、25bを第2半導体層3に形成する。

(もっと読む)

半導体装置の製造方法とそのような方法により得られる半導体装置

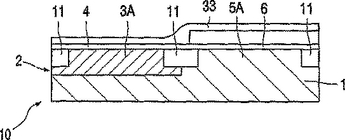

この発明は、基板(1)と半導体本体(2)とを有する半導体装置(10)であって、第一のチャネル領域(3A)と第一の導体を含み且つ誘電体層(4)によりチャネル領域から分離された第一のゲート電極(3B)とを有する第一の(NMOS)FET(3)を備え、そして、第二のチャネル領域(5A)と第一の導体とは異なる第二の導体を含み且つ誘電体層(4)によりチャネル領域(5A)から分離された第二のゲート電極(5B)とを有する第二の(PMOS)FET(5)を備え、第一及び第二のゲート電極(3B、5B)を形成するために、誘電体層(4)が備えられた半導体本体(2)上に第一の導体層(33)が堆積され、導体層(33)は、その後、第一のチャネル領域(3A)外部で除去され、その後、第二の導体層(55)が半導体本体(2)上に堆積され、そして、第一の導体層(33)が堆積される前に、誘電体層(4)上に中間層(6)が堆積される半導体装置の製造方法に関する。この発明によれば、中間層(6)のための材料として誘電体層(4)に対し選択的にエッチング可能な材料が選ばれ、そして、第一の導体層(33)が堆積される前に、第一のチャネル領域(3A)の位置で中間層(6)が除去され、そして、第一の導体層(33)が堆積され、第一のチャネル領域(3A)外部で除去された後に、そして、第二の導体層(55)が堆積される前に、第二のチャネル領域(5A)の位置で中間層(6)が除去される。従って、FETが、簡単な方法で、且つ、それらのゲート誘電体にダメージを与えずに得られる。好ましくは、中間層(6)に対して選択的にエッチング可能なさらなる中間層(8)が中間層(6)上に堆積される。  (もっと読む)

(もっと読む)

薄膜トランジスタアレイ基板及びその製造方法、並びに液晶ディスプレイパネル

【課題】 接合容量(Cgd)を減少し、フィードスルー効果、又は接合容量(Cgd)が大き過ぎることで生じる問題を改善できる薄膜トランジスタ構造を提供する。

【解決手段】 薄膜トランジスタアレイ基板は、基板300、前記基板300の上に形成されるゲート電極302、前記基板300と前記ゲート電極302を覆うゲート誘電体層308、前記ゲート誘電体層308の上に形成され、チャネル712を含む半導体層314、前記半導体層314における前記チャネル712の一方の側の部分と電気的に接続されたソース電極322、及び前記半導体層314における前記チャネル712の他方の側の部分と電気的に接続され、前記ゲート電極302に重ならないようにして配置されたドレイン電極324を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 SOI基板を用いることなく、絶縁体上の半導体層に形成されたトランジスタのゲート幅を広げる。

【解決手段】 選択エピタキシャル成長を行うことにより、第1半導体層2および第2半導体層3を半導体基板1上の素子領域R1に順次選択的に形成し、第2半導体層3が覆われるようにして半導体基板1上に支持体絶縁膜5を形成し、第1半導体層2の一部を露出させる開口部7を支持体絶縁膜5、第2半導体層3および第1半導体層2に形成し、開口部7を介してエッチングガスまたはエッチング液を第1半導体層2に接触させることにより、半導体基板1と第2半導体層3との間に空洞部9を形成し、半導体基板1および第2半導体層3の熱酸化を行うことにより、空洞部9に酸化膜10を形成し、開口部7が配置されるように構成されたソース/ドレイン層25a、25bを第2半導体層3に形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 異なるゲート長またはゲート幅を有し、フルシリサイド化されたゲート電極を備えた半導体装置を提供する。

【解決手段】 半導体装置100は、半導体基板5と、半導体基板上に形成された第1のゲート絶縁膜51と、半導体基板上に形成された第2のゲート絶縁膜52と、第1のゲート絶縁膜上に形成され、フルシリサイド化された第1のゲート電極11と、第2のゲート絶縁膜上に形成され、フルシリサイド化された第2のゲート電極12であって、半導体基板の表面を占める面積が第1のゲート電極よりも大きく、なおかつ、第1のゲート電極よりも厚みが薄い第2のゲート電極12とを備えている。

(もっと読む)

半導体装置

【課題】リーダ/ライタから送られてくる電磁波の減少を防ぎ、また磁界の変化に伴う素子形成層の発熱を防止することが可能である半導体装置を提供することを課題とする。

【解決手段】基板上に設けられた素子形成層と、素子形成層に接続されたアンテナとを有し、素子形成層は少なくとも電源配線および接地配線等の配線とを有しており、当該電源配線および接地配線等の配線を非環状で設ける。なお、素子形成層とアンテナとは少なくとも一部が重なるように設けてもよい。また、アンテナは、素子形成層の上方に設けてもよいし下方に設けてもよい。

(もっと読む)

CMOSFET内の歪みを最適化するための構造体及び方法

【課題】 CMOSFET内の歪みを最適化するための構造体及び方法を提供すること。

【解決手段】 MOSFET内の歪みを最適化し、より具体的には、1つの種類(P又はN)のMOSFET内の歪みを最大にし、かつ、別の種類(N又はP)のMOSFET内の歪みを最小にし緩和する、PMOSFET及びNMOSFETの両方を含む歪みMOSFETの半導体構造体、及び歪みMOSFETを製造する方法が開示される。元の完全な厚さを有する歪み誘起CA窒化物コーティングが、PMOSFET及びNMOSFETの両方の上に形成され、この歪み誘起コーティングは、1つの種類の半導体デバイス内に最適化された十分な歪みをもたらし、別の種類の半導体デバイスの性能を劣化させる。歪み誘起CA窒化物コーティングは、別の種類の半導体デバイスの上で減少した厚さまでエッチングされ、減少した厚さの歪み誘起コーティングは、他方のMOSFET内でより少ない歪みを緩和し、他方のMOSFET内により少ない歪みをもたらす。

(もっと読む)

半導体装置の製造方法とその方法で製造した半導体装置

【課題】 半導体装置の製造方法とその方法で製造した半導体装置に関し、微細な素子であるフィン型チャネルFETを含む半導体装置を高い精度で製造でき、しかも、安価に提供することが可能な製造工程設計(プロセスインテグレーション)及び素子構造を開示しようとする。

【解決手段】 SOI基板1のシリコン層上に細線状の多結晶シリコン膜を形成し、全面にSiN膜を形成し、SiN膜を異方性エッチングして細線状の多結晶シリコン膜の側面にサイドウォール14Wを形成し、サイドウォール14Wをマスクとして下地である前記シリコン層をエッチングして正確な間隔をおいて相対向するフィン型チャネル層を形成する。

(もっと読む)

半導体装置、及びその作製方法

【課題】不揮発性メモリにおいて、印加電圧が高いという問題があった。これは、絶縁膜を介して、フローティングゲートにキャリアをトンネル効果により注入する必要があるからである。またこのようなキャリアの注入を行うことにより、絶縁膜の劣化が懸念される。そこで印加電圧を低くし、絶縁膜の劣化を防止したメモリを提供することを課題とする。

【解決手段】メモリのフローティングゲートとして機能するものとして、電荷移動錯体を有する無機化合物、及び有機化合物が混在された層を用いることを特徴とする。具体的には、絶縁層間に挟まれた、電荷移動錯体を有する無機化合物、及び有機化合物が混在された層をフローティングゲートとして用いたトランジスタ構造を有する素子である。

(もっと読む)

半導体装置とその製造方法

【課題】

フィン型構造を持つ電界効果トランジスタのソース/ドレインのコンタクト抵抗を低減する。

【解決手段】

半導体装置は、絶縁性表面を有する支持基板上に形成され、ほぼ垂直な一対の側面および前記両側面を接続する上面を有し、第1導電型を有するフィン型半導体領域と、前記フィン型半導体領域の中間部を横断して形成され、フィン型半導体領域の側面に倣う側壁を有する絶縁ゲート電極構造と、ゲート電極両側のフィン型半導体層に形成された、第1導電型と逆の第2導電型を有するソース/ドレイン領域と、導電性ゲート電極の側壁上に形成された部分を含み、ソース/ドレイン領域上において、前記フィン型半導体領域の側面の上端から下端に達する開口を有するサイドウォール絶縁膜と、サイドウォール絶縁膜の開口内に露出されたソース/ドレイン領域の表面に形成されたシリサイド層と、シリサイド層にコンタクトするソース/ドレイン電極と、を有する。

(もっと読む)

細線状MOSFETを含む半導体装置

【課題】 簡単な構成を採ることで、細線状素子領域に於けるソース領域及びドレイン領域からチャネル領域に向かって機械的な応力を効率良く印加し、キャリヤ移動度を向上させようとする。

【解決手段】 細線状チャネル領域4を挟んで細線状ソース領域8及び細線状ドレイン領域9が配設された細線状素子領域と、細線状ソース領域8及び細線状ドレイン領域9それぞれの少なくとも側面を覆う圧縮或いは引張の応力を発生する応力発生膜11或いは12とを備える。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】 印刷法により形成される薄膜トランジスタにおいて、ソース・ドレイン電極及びゲート電極などの各種電極が微細かつ高い位置精度によって形成された薄膜トランジスタを提供する。

【解決手段】 本発明の薄膜トランジスタは、多孔質層が片面または両面に形成されたゲート絶縁膜と、該ゲート絶縁膜の一方に形成されたゲート電極と、前記ゲート絶縁膜の他方に形成されたソース・ドレイン電極とを有し、少なくとも、ゲート電極またはソース・ドレイン電極のいずれかが前記多孔質膜上に形成されている。

(もっと読む)

半導体装置とその製造方法

【課題】

フィン型構造を持つ電界効果トランジスタのソース/ドレインのコンタクト抵抗を低減する。

【解決手段】

半導体装置の製造方法は、第1の高さのフィン型半導体領域うえに、第1の高さより高い第2の高さの絶縁ゲート電極構造を形成し、サイドウォール絶縁膜をフィン型半導体領域の側面からは完全に異方性エッチングで除去し、フィン型半導体領域近傍のゲート電極両側面ではフィン型半導体領域の上面、側面をサイドウォール絶縁膜が囲むように、ゲート電極両側面上下部を残して上部上からエッチング除去し、フィン型半導体領域の少なくとも露出している両側面に上端から下端までシリサイド層を形成する。層間絶縁膜形成後、フィン型半導体領域の両側面のシリサイド層を露出するコンタクトホールを形成し、導電性プラグを埋め込む。

(もっと読む)

電界効果トランジスタ及びその製造方法

本発明は、微細加工プロセスを経ずゲート・チャネル間距離を短く微細化した構造を有し、ゲート容量が大きく、ゲートによるチャネル電流の制御を低電圧で行うことができる高性能な縦型の電界効果トランジスタ、及び該電界効果トランジスタを微細加工プロセス等の複雑なプロセスを経ず簡便かつ効率的に製造可能な方法を提供することを目的とする。本発明の電界効果トランジスタは、第一の電極と、該第一の電極に対し電気的に絶縁された状態で配置された第二の電極と、該第一の電極及び該第二の電極の少なくとも一方を貫通しかつ該第一の電極及び該第二の電極を露出させるホールの内壁に沿って設けられ、かつ該第一の電極と該第二の電極とを接続する半導体性棒状体と、少なくとも一部が前記ホール内に挿入され、かつ前記半導体性棒状体に対して絶縁層を介して対向した状態で配置された第三の電極とを有する。絶縁層の厚みが50nm以下である態様、半導体性棒状体が単層カーボンナノチューブである態様等が好ましい。  (もっと読む)

(もっと読む)

半導体装置およびその作製方法

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶装置および半導体装置を安価で提供することを課題とする。

【解決手段】基板上に設けられた、第1のトランジスタと第2のトランジスタとを含む素子形成層と、素子形成層上に設けられた記憶素子と、記憶素子の上方に設けられたセンサ部とを有し、記憶素子は、第1の導電層と有機化合物層と第2の導電層との積層構造を有し、第1の導電層と第1のトランジスタとが電気的に接続され、センサ部と第2のトランジスタが電気的に接続されるように設ける。

(もっと読む)

半導体装置およびその製造方法

本発明に係る半導体装置は、第1の絶縁層(11)と、第1の絶縁層上に形成された島状の半導体からなる第1の本体部(13)と、第1の絶縁層上に形成された島状の半導体からなる第2の本体部(14)と、第1の絶縁層上に第1の本体部と第2の本体部とを連結するように形成されたリッジ状の連結部(15)と、連結部の長さ方向における少なくとも一部からなるチャネル領域(15a)と、チャネル領域の外周を第2の絶縁層(17)を介して覆うように形成されたゲート電極(18)と、第1の本体部と、連結部の、該第1の本体部とチャネル領域との間の部分とに渡るように形成されたソース領域と、第2の本体部と、連結部の、該第2の本体部とチャネル領域との間の部分とに渡るように形成されたドレイン領域と、を備え、チャネル領域を構成する半導体が格子歪みを有している。  (もっと読む)

(もっと読む)

高い誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法

【課題】

高誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法を提供する。

【解決手段】

本発明の金属化合物は、TiCを含み、約4.75乃至約5.3eV、望ましくは、約5eVの仕事関数を有し且つ高誘電率の誘電体および界面層を含むゲート積層体上で熱的に安定する。更に、そのTiC金属化合物は、非常に意欲的な等価酸化膜厚(EOT)およびp型金属酸化物半導体(pMOS)装置における14Åよりも小さい反転層厚へのスケーリングを可能にする1000℃においても非常に効率的な酸素拡散バリアである。

(もっと読む)

1,801 - 1,820 / 2,010

[ Back to top ]