Fターム[5F110EE45]の内容

Fターム[5F110EE45]に分類される特許

1,861 - 1,880 / 2,010

半導体装置及びその製造方法

nMOS構造の半導体装置において、不純物拡散層(21)を形成するに際して、エクステンション領域(13)及びポケット領域(11)の形成、更にエクステンション領域(13)の不純物拡散を抑制する目的に用いる最適な不純物の組み合わせを考察し、エクステンション領域(13)の不純物に少なくともリン(P)を、ポケット領域(11)の不純物に少なくともインジウム(In)を用い、更に拡散抑制物質として炭素(C)を用いる。これにより、特にnMOS構造の半導体装置において、閾値電圧のロールオフ特性及び電流駆動能力を向上させ、ドレインリーク電流の低減を図りつつも、素子の微細化・高集積化を容易且つ確実に実現し、特にCMOS構造の半導体装置の最適設計を可能としてデバイス性能の向上及び低消費電力化を実現する。  (もっと読む)

(もっと読む)

電子デバイス、電子デバイスの製造方法および電子機器

【課題】特性に優れ、かつ、特性の経時劣化を防止し得る電子デバイス、かかる電子デバイスを用いた表示装置、および、電子機器を提供すること。

【解決手段】薄膜トランジスタ1は、互いに分離して設けられたソース電極20aおよびドレイン電極20bと、ソース電極20aおよびドレイン電極20bの表面に形成された有機膜60と、ソース電極20aおよびドレイン電極20bを覆い、かつ、有機膜60と接触するように設けられた有機半導体層30と、有機半導体層30上に設けられたゲート絶縁層40と、ゲート絶縁層40上に設けられたゲート電極60とを有する。有機膜60は、好ましくは一般式:CF3(CF2)m(CH2)nSH(ただし、mは1〜35の整数を示し、nは2〜33の整数を示す。)で表される非共役系有機化合物を含む有機化合物を、ソース電極20aおよびドレイン電極20bの表面に結合させてなるものである。

(もっと読む)

配線の作製方法

スピン塗布によりレジストの被膜を形成する場合、無駄となってしまうレジスト材料が存在し、さらに、必要に応じて端面洗浄の工程が増えてしまう。また、真空装置を用いて、基板上に薄膜を成膜する際には、チャンバー内を真空にする特別な装置や設備が必要で、製造コストが高くなってしまう。本発明は、絶縁表面を有する基板上に、CVD法、蒸着法又はスパッタ法により選択的に導電層を形成するステップと、前記導電層に接するように、組成物を吐出してレジストマスクを形成するステップと、前記レジストマスクを用いて、大気圧又は大気圧近傍下で、プラズマ発生手段により前記導電層をエッチングするステップと、大気圧又は大気圧近傍下で、前記プラズマ発生手段により前記レジストマスクをアッシングするステップを有することを特徴とする。上記特徴により、材料の利用効率を向上させて、製造コストの低減を実現する。  (もっと読む)

(もっと読む)

半導体装置

【課題】低抵抗、且つ高耐熱性を有するゲート電極またはゲート配線を備えた高性能な半導体装置を実現する。

【解決手段】ゲート電極またはゲート配線を三層以上の積層構造とし、例えば、第1の導電層106a/第2の導電層106b/第3の導電層106cを形成する。さらに、第2の導電層の幅は、第1の導電層及び第3の導電層の幅よりも狭いことを特徴とする。そして第1の導電層及び第3の導電層は高融点金属でなる。これにより高性能な半導体装置を実現できる。

(もっと読む)

ニッケルシリサイド膜の形成方法、半導体装置の製造方法およびニッケルシリサイド膜のエッチング方法

基板シリコン中のシリコン原子の消費量をできるだけ少なくして、なおかつ十分な厚さをもった低抵抗のニッケルシリサイド膜の形成方法、半導体装置の製造方法およびニッケルシリサイド膜のエッチング方法を提供する。表面に半導体領域および絶縁膜領域を有する基板上に、シリサイド反応を起こさない第1の基板温度で少なくとも各1層よりなるニッケル層とシリコン層を交互に積層する積層膜形成工程と、その積層膜をニッケルモノシリサイドが生成する第2の基板温度で熱処理するシリサイド反応工程と、ウェットエッチングによって絶縁膜上に形成された膜を除去する工程とを含む半導体装置の製造方法であって、積層膜形成工程において、積層膜全体のシリコン原子数に対するニッケル原子数の比を1または1より大きくすることによって、上記課題を解決した。  (もっと読む)

(もっと読む)

薄膜蝕刻方法及びこれを用いた液晶表示装置の製造方法

【課題】フェムト秒レーザーを用いて薄膜を蝕刻することによって工程の単純化及び生産性の向上が図られる薄膜蝕刻方法及びこれを用いた液晶表示装置の製造方法を提供する。

【解決手段】基板上に薄膜を形成する段階と、この薄膜上部にパターン形状が定義されたマスクを整列する段階と、このマスクに定義されたパターン形状を有するように前面にフェムト秒レーザーを照射して薄膜を選択的に除去する段階とを備える。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。また、それらの表示装置を構成する配線等を、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】導電層を有する基板に対して裏面からの光照射によって、選択的に基板表面を改質し、ぬれ性を制御する。改質された表面上に、導電性材料又は絶縁性材料を吐出(噴出なども含む)などによって、付着させ、導電層、絶縁層を形成する。また、光触媒物質の光吸収、エネルギー放射作用によって、光による処理効率を向上させることができる。また、導電層上にも選択的にマスク層を形成し、非照射領域である導電層上の領域のぬれ性も制御する。

(もっと読む)

半導体基板、半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】SIMOX法を用いることなく、膜厚が互いに異なるBOX層を同一基板に形成する。

【解決手段】支持体絶縁膜5に形成された開口面を介してエッチングガスまたはエッチング液を第1半導体層および第2半導体層3に接触させることにより、第1半導体層3をエッチング除去し、半導体基板1と第2半導体層3との間に空洞部6を形成するとともに、第2半導体層3の両端部を薄膜化し、半導体基板1および第2半導体層3の熱酸化を行うことにより、半導体基板1と第2半導体層3との間の空洞部6が埋め込まれるように半導体基板1上に酸化膜を形成する。

(もっと読む)

表示装置の作製方法

【課題】本発明は、しきい値のずれが生じにくく、高速動作が可能な逆スタガ型TFTを有する表示装置の作製方法を提供する。また、スイッチング特性が高く、コントラストがすぐれた表示が可能な表示装置の作製方法を提供する。

【解決手段】 本発明は、耐熱性の高い材料でゲート電極を形成した後、非晶質半導体膜の結晶化を促進する触媒元素を有する層、非晶質半導体膜、及びドナー型元素又は希ガス元素を有する層を形成し加熱して、非晶質半導体膜を結晶化すると共に触媒元素を結晶性半導体膜から除いた後、該結晶性半導体膜の一部を用いて半導体領域を形成し、該半導体領域に電気的に接するソース電極及びドレイン電極を形成し、ゲート電極に接続するゲート配線を形成して、逆スタガ型TFTを形成する。

(もっと読む)

表示装置の作製方法

【課題】本発明は、しきい値のずれが生じにくく、高速動作が可能な逆スタガ型TFTを有する表示装置の作製方法を提供する。また、スイッチング特性が高く、コントラストがすぐれた表示が可能な表示装置の作製方法を提供する。更には、少ない原料でコスト削減が可能であり、且つ歩留まりが高い表示装置の作製方法を提供する。

【解決手段】 本発明は、耐熱性の高い材料でゲート電極を形成した後、非晶質半導体膜の結晶化を促進する触媒元素を有する層、非晶質半導体膜、及びドナー型元素又は希ガス元素を有する層を形成し加熱して、非晶質半導体膜を結晶化すると共に触媒元素を結晶性半導体膜から除いた後、該結晶性半導体膜の一部を用いて半導体領域を形成し、該半導体領域に電気的に接するソース電極及びドレイン電極を形成し、ゲート電極に接続するゲート配線を形成して、逆スタガ型TFTを形成する。

(もっと読む)

液晶表示装置の作製方法

【課題】本発明は、しきい値のずれが生じにくく、高速動作が可能な逆スタガ型TFTを有する半導体装置の作製方法を提供する。また、スイッチング特性が高く、コントラストがすぐれた表示が可能な表示装置の作製方法を提供する。

【解決手段】 本発明は、耐熱性の高い材料でゲート電極を形成した後、非晶質半導体膜の結晶化を促進する触媒金属層、非晶質半導体膜、及びドナー型元素又は希ガス元素を有する層を形成し加熱して、非晶質半導体膜を結晶化すると共に触媒元素を結晶性半導体膜から除いた後、該結晶性半導体膜の一部を用いて半導体領域を形成し、該半導体領域に電気的に接するソース電極及びドレイン電極を形成し、ゲート電極に接続するゲート配線を形成して、逆スタガ型TFTを形成する。

(もっと読む)

半導体装置及びその作製方法、並びに電子機器

【課題】複数の機能を有する半導体装置及びその作製方法を提供することを課題とする。

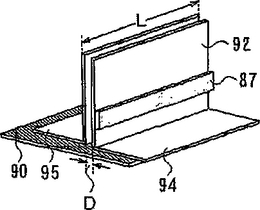

【解決手段】 本発明は、薄膜集積回路と、センサ又はアンテナを有する第1の基板と、アンテナを有する第2の基板を有し、センサ又はアンテナを有する第1の基板とアンテナを有する第2の基板とは、薄膜集積回路を挟持している半導体装置である。複数のアンテナを有し、且つ通信する周波数帯が異なる場合、複数の周波数帯を受信することが可能であるため、リーダライタの選択幅が広がる。また、センサとアンテナを有する場合、センサで検知した情報を信号化し、アンテナを介して該信号をリーダライタに出力することが可能である。このため、従来の無線チップ等の半導体装置より、高付加価値を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ソースドレインエクステンションからゲート絶縁膜へのボロンの拡散が抑制された信頼性の高い半導体装置およびその製造方法を得ること。

【解決手段】半導体基板と、前記半導体基板の上層部に所定の間隔で形成された一対のソースドレインエクステンションと、前記半導体基板上の前記一対のソースドレインエクステンションに挟まれた領域に前記ソースドレインエクステンションとオーバーラップする領域を有して形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、を備え、前記ゲート絶縁膜は、前記ゲート電極と前記ソースドレインエクステンションとのオーバーラップ領域に対応する領域のみが、窒素が導入された窒素導入領域とされている。

(もっと読む)

薄膜装置の製造方法、アクティブマトリクス基板、電気光学装置、電子機器

【課題】 材料の無駄を軽減しつつ、1回転写であって薄膜装置への配線工程を簡略化可能な薄膜装置の製造方法を提供する。

【解決手段】 転写元基板(100)上に、所定のエネルギ付与によって剥離する特性を有し、かつ、導電性を呈する剥離層(102)を形成する工程、剥離層上に薄膜装置を含む被転写層(110)を形成する工程、被転写層の一方の面に接着層(120)を介して転写先基板(122)を接合する工程、剥離層(102)にエネルギを付与して転写元基板(100)と剥離層(102)との間に剥離を生じさせ、剥離層とともに被転写層を転写先基板(122)に転写する工程、及び転写先基板に転写されて露出した剥離層(102)をパターニングして、薄膜装置と電気的に接続された配線層(102a〜d)を形成する工程を備える。

(もっと読む)

異なるように歪ませた歪みチャネル領域を有する半導体領域を含む、半導体デバイスおよびその製造方法

インレイド技術により形成されたトランジスタ構成のゲート電極構造を横方向に取り囲む絶縁層の固有の応力を部分的に修正することによって、異なるトランジスタ素子の荷電キャリア移動度を個別に調整する。特に、インレイド・ゲート構造トランジスタ構造において、NMOSトランジスタおよびPMOSトランジスタは、それぞれ、引っ張り応力と圧縮応力を受け取り得る。  (もっと読む)

(もっと読む)

半導体装置の作製方法、半導体装置及び電子機器

【課題】 半導体装置の製造を容易にすることを課題とする。また、コストを低減した半導体装置を提供することを課題とする。

【解決手段】 本発明は、剥離層を除去した後に、基板と下地絶縁層が密着した領域を設けることで、下地絶縁層の上方に設けられた薄膜集積回路の飛散を防止することができる。従って、薄膜集積回路を含む半導体装置の製造を容易にすることができる。また、本発明は、シリコン基板以外の基板を用いて半導体装置を製造するため、大量の半導体装置を一度に形成することが可能となり、コストを低減した半導体装置を提供することができる。

(もっと読む)

半導体ウエハ、半導体装置および半導体装置の製造方法

【課題】前工程後の半導体デバイスの高周波特性と後工程後の半導体デバイスの高周波特性との差を減少することができると共に、完成品の電気特性等の信頼性を維持することができる半導体ウエハ等を提供する。

【解決手段】半導体ウエハは、スクライブライン領域60により区画された素子形成領域50を有している。そして、TEGとして利用可能な素子およびTEG用パッド8は、素子形成領域50内に形成されている。

(もっと読む)

薄膜装置の製造方法、電気光学装置、及び電子機器

【課題】 転写技術を利用して高密度実装及び薄型化が可能な薄膜装置の製造方法を提供する。

【解決手段】 転写元基板(100)上に、所定のエネルギ付与によって剥離する第1剥離層(102)を介して薄膜装置を含む被転写層(110)を形成する工程、被転写層を仮転写基板(116)に接合する工程、エネルギを付与して第1剥離層(102)に界面剥離及び/又は層内剥離を生じさせることにより転写元基板(100)を被転写層(110)から剥離する工程により、仮転写基板(116)に被転写層(110)が接合された積層構造を一対形成し、転写先基板(120)の両面に、一対の積層構造の被転写層(110)をそれぞれ接着する工程、及び被転写層の各々から仮転写基板(116)を分離する工程を備えることにより、転写先基板(120)の両面に各被転写層(110)を転写する。

(もっと読む)

アライメント方法、薄膜形成基板の製造方法、半導体装置の製造方法、及び電子機器の製造方法

【課題】 液相プロセスを用いてデバイスを製造する際に好適なアライメント方法を提供する。

【解決手段】 液相法を用いて基板10上に機能膜12を形成する工程を含むデバイスの製造過程において、前記機能膜12が形成される基板10に、前記機能膜12以降に形成される膜13に対して形状が現れるようなアライメントマークAM1を形成し、該アライメントマークAM1を用いて前記機能膜12以降の膜13のアライメントを行なう。

(もっと読む)

有機電界効果トランジスタの製造方法及びその有機電界効果トランジスタ

【課題】有機電界効果トランジスタの製造方法において、有機半導体層にダメージを与えることなく、かつ通常のリソグラフィプロセスを行わずに、有機半導体層のパターニングを行うことができる有機電界効果トランジスタの製造方法及びその有機電界効果トランジスタを提供する。

【解決手段】基板1上にゲート電極2を形成し、その上にゲート絶縁膜3を形成し、このゲート絶縁膜3上に形成された少なくともソース・ドレイン電極8,9間を含む部位に有機半導体層10を積層する有機電界効果トランジスタの製造方法において、前記有機半導体層10に照射光を部分的に遮るマスクを介して直接光照射を行うことにより、二次元的な有機半導体層のパターン形成を行う。

(もっと読む)

1,861 - 1,880 / 2,010

[ Back to top ]