Fターム[5F110EE45]の内容

Fターム[5F110EE45]に分類される特許

1,901 - 1,920 / 2,010

薄膜半導体装置、電気光学装置、電子機器、薄膜半導体装置の製造方法、及び薄膜電子装置

【課題】 例えばTFT等の薄膜半導体装置において、耐電圧性を高め、オフリーク電流を低減する。

【解決手段】 チャネル領域と不純物がドープされたソース領域及びドレイン領域とを含むと共に島状の平面パターンを有する半導体膜と、チャネル領域にゲート絶縁膜を介して対向配置されたゲート電極とを備える。ソース領域及びドレイン領域の夫々における、島状の平面パターンの周辺領域のうち少なくともチャネル領域に隣接する第1部分は、周辺領域を除くと共にチャネル領域に沿ってチャネル領域に隣接する第2部分を除く中央領域と比べて、不純物の濃度が低い。

(もっと読む)

半導体基板、半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 絶縁体上に形成される半導体層の配置位置に制約を伴うことなく、信頼性の高い半導体層を安価に絶縁体上に形成する。

【解決手段】 第1半導体層2上に第2半導体層3を形成し、開口部8を介してエッチングガスまたはエッチング液を第1半導体層2に接触させることにより、第1半導体層2の一部をエッチング除去し、半導体基板1と第2半導体層3との間に空洞部9を形成した後、化学気相成長法により酸化膜を堆積することにより、空洞部9内に酸化膜10を形成する。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 高い電子移動度、低いスレショルド電圧および漏れ電流が少ないなどの特性を有するTFTの製造方法を提供する。

【解決手段】 基板上に非晶質シリコン層30を形成する段階、非晶質シリコン層をパターニングしてソース領域32、ドレイン領域34およびそれらの間に介在される複数のチャンネル36を形成する段階、複数のチャンネルをアニーリングする段階、複数のチャンネル上にゲート酸化膜40およびゲート電極50を順次に形成する段階、ソース領域およびドレイン領域に導電性不純物をドーピングする段階を含むTFTの製造方法。

(もっと読む)

半導体装置およびその作製方法

【課題】レーザビームが照射された領域全体に占める微結晶が形成される領域の割合を減らし、半導体膜に対して良好にレーザ照射を行うことができるレーザ照射装置を提供すること、およびレーザ照射方法を提供すること。

【解決手段】レーザ発振器101から出射したレーザ光104をスリット102を通過させることによって強度の弱い部分を遮断した後にミラー103で偏向させ、このレーザ光を凸型シリンドリカルレンズ105,106または凸型球面レンズを用いて任意の大きさにビームの整形をした後に照射面に照射する。

(もっと読む)

半導体装置

【課題】 半導体装置に於いて、高い短チャネル効果耐性並びに高い電流駆動能力を保ちつつ、ゲート絶縁膜中の電場の緩和を図る。その結果として高電流駆動能力且つ高信頼性の、高性能な微細半導体装置を提供する。

【解決手段】 チャネルの形成される領域が稜を持つ電界効果トランジスターに於いて、稜の近傍に於いてはゲート絶縁膜が他の領域よりも厚く形成されている、ないしゲート絶縁膜は積層であり、積層を形成する層の内で誘電率の低い層が稜の近傍に於いて他の領域よりも厚く形成されている。それ故、チャネル領域の電位に対するゲート電極の制御性は良好に保たれたままでゲート絶縁膜中に生ずる電場強度の緩和が図られ、その結果として高電流駆動能力且つ高信頼性の高性能微細半導体装置を実現する。

(もっと読む)

無線チップ及びその作製方法

【課題】本発明は、無線チップのコストを下げることを課題とする。また、無線チップの大量生産を可能として、無線チップのコストを下げることを課題とする。さらに、小型・軽量な無線チップを提供することを課題とする。

【解決手段】本発明は、ガラス基板や石英基板から剥離された薄膜集積回路が第1の基体と第2の基体に設けられた無線チップを提供する。本発明の無線チップは、シリコン基板からなる無線チップと比較して、小型、薄型、軽量を実現する。本発明の無線チップが含む薄膜集積回路は、少なくとも、LDD(Lightly Doped drain)構造のN型の薄膜トランジスタと、シングルドレイン構造のP型の薄膜トランジスタと、アンテナとして機能する導電層とを有することを特徴とする。

(もっと読む)

金属ゲート電極半導体デバイス

高誘電率ゲート誘電体を有するNMOS及びPMOSトランジスタを含む相補型金属酸化物半導体集積回路が半導体基板上に形成される。ゲート誘電体上に金属障壁層が形成される。金属障壁層上に仕事関数設定金属層が形成され、仕事関数設定金属層上にキャップ金属層が形成される。  (もっと読む)

(もっと読む)

有機半導体装置

【課題】素子特性を向上させることが可能な有機半導体装置を提供する。

【解決手段】この有機半導体装置は、SiO2基板1の主表面上に形成された第1ゲート電極2と、第1ゲート電極2の一部上に第1ゲート絶縁膜3を介して形成されたドレイン電極4と、ドレイン電極4上に第2ゲート絶縁膜5を介して形成された第2ゲート電極6と、少なくとも第2ゲート電極6上に形成されたソース電極10と、ドレイン電極4およびソース電極10に接触するように形成された有機半導体層9とを備える。

(もっと読む)

有機薄膜トランジスタ、有機薄膜トランジスタシート及びこれらの製造方法

【課題】 基板への接着性が良好で、且つ、良好に駆動可能な有機薄膜トランジスタ、該有機薄膜トランジスタを設けた有機薄膜トランジスタシート及びこれらの製造方法の提供。

【解決手段】 支持体と金属箔とをラミネートする接着層を支持体上に有し、前記支持体と前記金属箔とが前記接着層によりラミネートされ、前記支持体上にラミネートされた前記金属箔表面が研磨されたものであることを特徴とする有機薄膜トランジスタ。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 SOI基板を用いることなく、ボディの複数面にゲート電極が配されたSOIトランジスタを形成する。

【解決手段】 半導体基板1上に凸部3を設け、凸部3の側方から内側に向かって進入するように凸部3と半導体基板1との間に酸化膜2を形成し、ゲート絶縁膜4を介して凸部3に跨るように配置されたゲート電極5を半導体基板1上に形成することにより、凸部3上および左右の3面にゲート電極5を配するとともに、ゲート電極の側方にそれぞれ配置されたソース層6aおよびドレイン層6bを凸部3に形成する。

(もっと読む)

高移動性バルク・シリコンPFET

【課題】 従来のPFETに比べて減少されたシリコン面積および電力消費での高速のスイッチング速度をもつ改良されたPFETと、改良されたPFETと同時に製造されることができるNFETとの両方を提供すること。

【解決手段】 電界効果トランジスタ(100)及び電界効果トランジスタを製造する方法である。電界効果トランジスタは、ゲート誘電体層(155)の上面(170)に形成されたゲート電極(165)と、単結晶シリコン・チャネル領域(110)の上面(160)のゲート誘電体層と、Ge含有層(135)の上面の単結晶シリコン・チャネル領域と、単結晶シリコン基板(150)の上面のGe含有層と、単結晶シリコン基板の上面における第1誘電体層(215A)と第2誘電体層(215B)との間のGe含有層とを含む。

(もっと読む)

半導体装置及びその製造方法

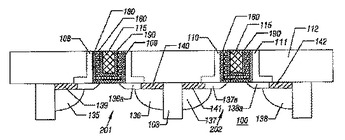

【課題】 本発明の目的は、ゲート長が高精度に制御され、かつ、ショートチャネル効果を抑制する半導体装置及びその製造方法を提供することである。

【解決手段】 第1のゲート電極膜17aと、第1のゲート電極膜17aのゲート長よりも長いゲート長を具備する第2のゲート電極膜20とを有する2段型ゲート電極20aを形成することにより、ゲート長が高精度に制御される。また、エクステンション領域21は第2のゲート電極膜20をマスクにして不純物導入がされるため、ショートチャネル効果を抑制することができる。

(もっと読む)

ポリシリコンゲルマニウムゲートスタック及びその形成方法

従来のCMOSゲートスタックと比べて反転キャパシタンスを増大させるCMOSゲートスタックが記載される。ゲート誘電体層に近い従来のポリSiゲートの代わりに、ポリSiGeゲートを用いて、活性化され得る埋込まれたドーパント量を増加させる。この増加は、従来のCMOSゲートスタックにおける反転キャパシタンスを制限するポリシリコンの枯渇を克服する。ポリSiGe層をゲートスタックに組込むために、ゲート誘電体層とポリSiGe層との間にSi薄層を堆積させる。適切なサリサイド形成を確実にするために、ポリSiGe層の上にポリSi層のキャップを被せる。ポリSiGeの上に微粒子のポリSiを得るために、ポリSi層とポリSiGe層の間に第2のSi層を堆積させる (もっと読む)

表示装置及びその作製方法、並びにテレビジョン装置

【課題】 本発明は、材料の利用効率を向上させ、少ないフォトマスク数で、しきい値のずれが生じにくく、高速動作が可能なTFTを有する表示装置の作製方法を提供する。

【解決手段】 本発明の表示装置の一は、絶縁表面上に設けられたゲート電極層及び画素電極層を有し、ゲート電極層上にゲート絶縁層を有し、ゲート絶縁層上に結晶性半導体層を有し、結晶性半導体層に接して一導電型を有する半導体層を有し、一導電性を有する半導体層に接してソース電極層及びドレイン電極層を有し、ソース電極層、ドレイン電極層及び画素電極層上に絶縁層を有し、絶縁層はソース電極層又はドレイン電極層に達する第1の開口部を有し、ゲート絶縁層及び絶縁層は画素電極層に達する第2の開口部を有し、第1の開口部及び第2の開口部に、ソース電極層又はドレイン電極層と画素電極層とが電気的に接続する配線層を有する。

(もっと読む)

両末端に脱離反応性の異なる異種官能基を有する有機化合物を用いた有機薄膜および該有機薄膜の製造方法

【課題】 膜厚が均一で、かつ分子配列の秩序性が高い単一単分子膜およびその累積膜、およびそれらの製造方法を提供すること。

【解決手段】 一般式;Si(A1)(A2)(A3)−B−Si(A4)(A5)(A6)(A1〜A6は水素原子、ハロゲン原子、アルコキシ基またはアルキル基であり、脱離反応性についてA1〜A3>A4〜A6の関係を満たす;Bは2価の有機基である)の有機化合物を用いた有機薄膜。上記有機化合物におけるA1〜A3を有するシリル基と基板表面とを反応させ、単一単分子膜を形成する工程、未反応の有機化合物を非水系溶媒を用いて洗浄除去する工程、および単分子膜の膜表面側に存在する未反応のシリル基を吸着反応のサイトとして、上記の有機化合物からなる単分子膜を累積させる工程を含む有機薄膜の製造方法。

(もっと読む)

半導体装置及びその作製方法、並びにテレビジョン

【課題】本発明は、しきい値のずれが生じにくく、高速動作が可能な逆スタガ型のTFTを有する半導体装置の作製方法を提供する。また、少ない原料でコスト削減が可能であり、且つ歩留まりが高い半導体装置の作製方法を提供する。

【解決手段】 本発明は、耐熱性の高い材料でゲート電極を形成した後、非晶質半導体膜を成膜し、該非晶質半導体膜に触媒元素を添加し加熱して結晶性半導体膜を形成し、該結晶性半導体膜上にドナー型元素又は希ガス元素を有する層を形成し加熱して触媒元素を結晶性半導体膜から除いた後、該結晶性半導体膜の一部を用いて半導体領域を形成し、該半導体領域に電気的に接するソース電極及びドレイン電極を形成し、ゲート電極に接続するゲート配線を形成して、逆スタガ型のTFTを形成して半導体装置を作製する。

(もっと読む)

電子装置及びその製造方法、並びに、半導体装置の製造方法

【課題】微粒子と有機半導体分子との結合によって構成される導電路を、一層簡素に、短時間にて形成する半導体装置の製造方法を提供する。

【解決手段】所謂ボトムゲート/ボトムコンタクト型の電界効果型トランジスタの製造方法、基体11上にゲート電極12を形成した後、基体11及びゲート電極12上にゲート絶縁層13を形成し、次いで、ゲート絶縁層13上にソース/ドレイン電極14を形成した後、ソース/ドレイン電極14間に、導電路23から成るチャネル形成領域15を形成する工程から成り、このチャネル形成領域15を形成する工程は、導体又は半導体から成る微粒子を含む溶液と有機半導体分子とを混合することによって、微粒子と有機半導体分子とが結合(反応)して成るクラスター20を得た後、該クラスター20をソース/ドレイン電極14の間のゲート絶縁層13の部分に配置する工程から成る。

(もっと読む)

有機薄膜トランジスタ用材料およびこれを用いた有機薄膜トランジスタ

【課題】

キャリア移動度の高い新規な有機薄膜トランジスタ用材料およびこれを用いた有機薄膜トランジスタを提供すること。

【解決手段】

下記一般式(1)で表されるホスフィンオキサイド化合物を含有することを特徴とする有機薄膜トランジスタ用材料。

【化1】

(ここでR1およびR2は同じでも異なっていてもよく、それぞれ、水素、アルキル基、シクロアルキル基、複素環基、アルケニル基、シクロアルケニル基、アルキニル基、アルコキシ基、アルキルチオ基、アリールエーテル基、アリールチオエーテル基、アリール基、ヘテロアリール基、シアノ基、カルボニル基、エステル基、カルバモイル基、アミノ基、シリル基、並びに隣接置換基との間に形成される縮合環の中から選ばれる。Ar1はアリール基またはヘテロアリール基を表す。)

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】 可撓性のあるフレキシブルな基板に形成されたトップコンタクト構造の高性能な電界効果トランジスタの製造方法を提供する。

【解決手段】 剛性の高い材料よりなる補助基板40上にソース電極28A及びドレイン電極28Bよりなる第1電極28を剥離可能に形成する工程と、第1電極を可撓性のある第1基板14に移転させる工程と、可撓性のある第2基板16上に、ゲート電極となる第2電極18とゲート絶縁膜20とパターン化された有機半導体膜22とを順次形成する工程と、ソース電極及びドレイン電極のそれぞれの一部が有機半導体膜上に位置するように第1電極と有機半導体膜とを対向させて第1基板と第2基板とを接合する工程とを有する。これにより、可撓性のあるフレキシブルな基板に形成されたトップコンタクト構造の高性能な電界効果トランジスタを形成する。

(もっと読む)

画素回路、発光装置、及び電子機器

【課題】 発光装置において、発光素子に電流を供給するTFTのしきい値が画素ごとにばらつくことによって生ずる輝度ムラが、発光装置の画質向上の足かせとなっていた。

【解決手段】 発光素子を制御する第1のトランジスタと、第1の電極が前記第1のトランジスタのゲートに接続され、前記第1のトランジスタのしきい値電圧に応じた電圧を保持する容量素子と、前記第1のトランジスタのゲートに対する電圧の供給を制御する第2のトランジスタと、配線から前記第1のトランジスタのソースまたはドレインの一方に対する電圧の供給を制御する第3のトランジスタと、前記容量素子の第2の電極に対する電圧の供給を制御する第4のトランジスタと、を有することを特徴とする。

(もっと読む)

1,901 - 1,920 / 2,010

[ Back to top ]