Fターム[5F110EE45]の内容

Fターム[5F110EE45]に分類される特許

1,981 - 2,000 / 2,010

金属からなるゲート電極を形成するための方法

一の実施形態では、ゲート誘電体層(18)を基板(10)の上に形成し、次に第1金属層(26)を、ゲート誘電体層(18)の内、第1素子タイプが形成される予定の部分の上に選択的に堆積させる。第1金属層(26)とは異なる第2金属層(28)は、ゲート誘電体層(18)の内、第2素子タイプが形成される予定の露出部分の上に選択的に形成される。第1及び第2素子タイプの各々は異なる仕事関数を有することになる、というのは、第1及び第2素子タイプの各々が、ゲート誘電体と直接コンタクトする異なる金属を含むことになるからである。一の実施形態では、第1金属層(26)の選択的堆積は、ALDにより、かつ阻止層(24)を使用することにより行なわれ、阻止層は、第1金属層(26)を、ゲート誘電体層(18)の内、阻止層(24)によって覆われない部分の上にのみ選択的に堆積させることができるようにゲート誘電体層(18)の上に選択的に形成される。 (もっと読む)

金属トランジスターデバイス

本発明はトランジスターデバイスのチャネル領域の絶縁基板上に形成される金属薄膜あるいは複合金属層が含まれるデプレッションあるいはエンハンスメントモードの金属トランジスターに関する。

(もっと読む)

(もっと読む)

適切なソース、ドレイン及びチャネル材料を有する電界効果トランジスタとそれを有する集積回路

ノーマリーオンのトランジスタはソース(10)、ドレイン(11)及びチャネル(7)を備える。ソース、ドレイン及びチャネル材料は、NMOS型トランジスタではドレイン材料の電子親和力Xdがチャネル材料の電子親和力Xcより低く、ソース材料の電子親和力Xsがチャネル材料の電子親和力Xcより高くなるように(Xd<Xc<Xs)選択される。さらに、PMOS型トランジスタではドレイン材料の価電子帯の上限Edがチャネル材料の価電子帯の上限Ecより高く、ソース材料の価電子帯の上限Esがチャネル材料の価電子帯の上限Ecより低くなるように(Es<Ec<Ed)材料が選択される。  (もっと読む)

(もっと読む)

ダイアモンド状のカーボンチャネルを有する電界効果トランジスタの製造方法、及び該製造方法により製造されるトランジスタ

ダイアモンド状のカーボンチャネルを有する電界効果トランジスタの製造方法、及び該製造方法により製造されるトランジスタ。

前記電界効果トランジスタは、ゲート絶縁膜(3)によりチャネル(7)から分離されたゲート電極(5)により制御されるチャネル(7)により接続されるソース(10)及びドレイン(11)を含む。前記チャネル(7)はダイアモンド状のカーボン層により形成される。前記トランジスタの製造方法は、続いて、ダイアモンド状のカーボン層を基板上(2)に堆積させ、ゲート絶縁層(3)を堆積させ、そして、少なくとも1つの導電層(4)を堆積させることを含む。前記導電層(4)は前記ゲート電極(5)からエッチングされる。次に、側面の絶縁膜(6)を形成するために、前記ゲート電極(5)の側面に絶縁材料が堆積される。次に、前記ゲート絶縁層(3)がエッチングされ、そして、前記ダイアモンド状のカーボン層がチャネル(7)の輪郭を描くようにエッチングされる。次に、前記ソース(10)を形成するための半導体材料、及び前記ドレイン(11)を形成するための半導体材料がチャネル(7)の両側に堆積される。  (もっと読む)

(もっと読む)

可撓性有機電子装置およびその作製方法

本発明は、透明導電酸化物層を含む第1の電極、有機活性層、第2の電極、および高分子基板層を少なくとも含み、透明導電層が、少なくとも250℃の温度で、除去可能な基板層上、または除去可能な基板層上に事前に適用された一つまたは複数の透明層上に適用され、高分子基板層が適用されると、除去可能な担体が除去される、可撓性有機電子装置を作製するための方法を提供する。本発明は、この方法によって得られる可撓性有機電子装置をさらに提供する。 (もっと読む)

アレイ状に配置された垂直型カーボン・ナノチューブ電界効果トランジスタを製造する方法、並びに、それによって形成された電界効果トランジスタ及びアレイ

【課題】 カーボン・ナノチューブ電界効果トランジスタと、カーボン・ナノチューブ電界効果トランジスタのアレイと、デバイス構造体とを製造するための方法、及び、該方法によって形成されたデバイス構造体のアレイを提供する。

【解決手段】 本方法は、ゲート電極層と、各々がソース/ドレイン・コンタクトと電気的に結合された触媒パッドとを含む積層構造体を形成することを含む。ゲート電極層は多数のゲート電極に分割され、少なくとも1つの半導体カーボン・ナノチューブが、化学気相堆積プロセスによって触媒パッドの各々の上に合成される。完成したデバイス構造体は、ゲート誘電体によって覆われた側壁を有するゲート電極と、該ゲート電極の該側壁に隣接する少なくとも1つの半導体カーボン・ナノチューブとを含む。ソース/ドレイン・コンタクトを半導体カーボン・ナノチューブの両端と電気的に結合することによって、デバイス構造体が完成する。多数のデバイス構造体は、メモリ回路又は論理回路のいずれかとして構成することができる。

(もっと読む)

垂直型ナノチューブ半導体デバイス構造体及びその形成方法

【課題】 大量生産技術に対応した、チャネル領域として1つ又は複数の半導体カーボン・ナノチューブを組み込む垂直型FET構造体を提供する。

【解決手段】 少なくとも1つのナノチューブを組み組む垂直型デバイス構造体、及び、化学気相成長法によってこうしたデバイス構造体を製造する方法である。各々のナノチューブは、触媒パッドによって触媒作用が及ぼされる化学気相成長法によって成長され、誘電体材料のコーティング内に包み込まれる。包み込まれたナノチューブがゲート電極の厚さを通って垂直方向に延びるように、該包み込まれたナノチューブの周りにゲート電極を形成することによって、垂直型電界効果トランジスタを作ることができる。包み込まれたナノチューブ、及び、該包み込められたナノチューブを支持する対応する触媒パッドが1つのキャパシタ・プレートを形成するように、キャパシタを作ることができる。

(もっと読む)

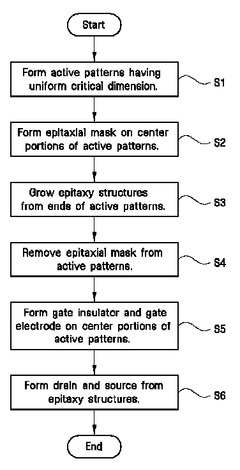

均一な臨界寸法のアクティブパターンで形成されたマルチゲートトランジスタ及びその製造方法

本発明は、均一な臨界寸法のアクティブパターンで構成されたマルチゲートトランジスタの製造方法を提供する。本発明はまた、均一な臨界寸法のアクティブパターンを具備するマルチゲートトランジスタを提供する。マルチゲートトランジスタの製造方法は先に少なくとも一つのアクティブパターンを形成する。以後、前記アクティブパターンの露出した領域から少なくとも一つのエピタキシ構造を成長させる。続いて、前記アクティブパターンの少なくとも2個の面にチャネル領域を形成する。  (もっと読む)

(もっと読む)

スペーサによって定められる通路内で成長した半導体ナノチューブを組み込んだ垂直型電界効果トランジスタ

【課題】 ICチップの大量生産技術に対応した、チャネル領域として1つ又は複数の半導体カーボン・ナノチューブを組み込んだ垂直型FET構造体を提供する。

【解決手段】 少なくとも1つの半導体ナノチューブによって定められたチャネル領域を有する垂直型電界効果トランジスタ、及び、こうした垂直型電界効果トランジスタを、スペーサによって定められるチャネルを用いて化学気相成長法によって製造する方法である。各々のナノチューブは、スペーサとゲート電極との間に定められる高アスペクト比通路の底部に位置決めされた触媒パッドにより触媒される化学気相成長法によって、成長する。各々のナノチューブは、スペーサによる境界の存在によって制限される垂直配向を持つ通路内で成長する。通路の開口部から離れたスペーサの底部に、隙間が設けられる。隙間を通って触媒パッドに流れる反応物質が、ナノチューブの成長に関与する。

(もっと読む)

歪みFINFETチャネルの製造方法

例示的実施形態はFinFETチャネル構造の形成法に関する。当該方法において、絶縁層(130)上に化合物半導体層(140)を提供し、化合物半導体層(140)上にトレンチ(142)を提供し、かつ、化合物半導体層(140)上およびトレンチ(142)内に歪み半導体層(144)を提供する。該方法において、さらに、化合物半導体層(140)上から歪み半導体層(144)を除去し、その結果、トレンチ(142)内に歪み半導体層(144)を残し、化合物半導体層(140)を除去して、歪み半導体層(144)を残し、かつ、フィン形のチャネル領域(152)を形成する。  (もっと読む)

(もっと読む)

直流ノード拡散領域の下に埋め込み酸化物を有さず、酸化物ホールを有する差別化SOI構造

直流ノード拡散領域の下に埋め込み酸化物を設けず、すべてのデバイスのための本体接触部を有する選択的SOI構造を提供する。印加電圧Vdd、接地GND、基準電圧Vrefおよびその他の類似DCノードなどのDCノード拡散領域の直下に存在する埋め込み酸化物を設けずに、すべてのデバイスのための本体接触部を有する選択的SOI構造を提供する。本発明の選択的SOI構造をIC中に用いて回路の性能を改善することができる。本発明の選択的SOI構造は、上に配置された複数のSOIデバイスを有する上部Si含有層を備える絶縁体上シリコン(SOI)基板材料を含む。本SOIデバイスは、本体接触部領域を介して下地のSi含有基板と接触する。下地の埋め込み酸化物領域を備えないDCノード拡散領域がSOIデバイスの一つに隣接する。

(もっと読む)

(もっと読む)

ヘテロ接合を備える半導体デバイス

ヘテロ接合を有する半導体デバイス。このデバイスは、基板と少なくとも1つのナノ構造とを備える。この基板とナノ構造とは、異なる材料から成る。この基板は、例えばIV族半導体材料から成ることがあるのに対して、このナノ構造は、III−V族半導体材料から成ることもある。このナノ構造は、この基板によって支持され、この基板とエピタキシャルな関係にある。ナノ構造は、ゲートアラウンドトランジスタデバイスなどの電子デバイスの機能コンポーネントになる可能性がある。ゲートアラウンドトランジスタの一実施形態においては、ナノワイヤ(51)が、基板(50)によって支持され、この基板はドレインであり、このナノワイヤは電流チャネルであり、上部金属コンタクト(59)はソースである。薄いゲート絶縁膜(54)が、このナノワイヤとこのゲート電極(55A、55B)とを絶縁している。  (もっと読む)

(もっと読む)

乱数生成素子

【課題】 増幅回路を用いなくても1Mbit/s以上の乱数生成レートが可能となるような物理現象中のランダムノイズを利用した乱数生成素子を提供することを目的とする。

【解決手段】 半導体表面との間で非常に薄いトンネル絶縁膜を介して電子の充放電が可能な導電性微粒子をチャネル上に設け、チャネル幅Wを狭く、かつ導電性微粒子の面密度Ddotを多く、かつチャネル〜導電性微粒子間のトンネル抵抗を小さくする。例えば、膜厚0.8nmのシリコン窒化膜をトンネル絶縁膜とするバルク基盤上の素子の場合、チャネル幅W=0.1μm、平均粒径d=8nm程度のSi微結晶粒子群を1.7×1012cm−2程度の面密度で形成すると、1MHzのノイズ成分を0.1%にできる。

(もっと読む)

FETゲート電極用のCVDタンタル化合物(TaおよびNを含む化合物の化学的気相堆積方法および半導体電界効果デバイス)

【課題】電界効果デバイスのゲート材料を提供すること。

【解決手段】電界効果デバイスのゲート材料として用いられるTaおよびNの化合物であって、さらに別の元素を含む可能性があり、約20mΩcmより小さな比抵抗を有し、約0.9より大きなN対Taの元素比を有する化合物が開示される。そのような化合物の代表的な実施態様であるTaSiNは、誘電体層および高k誘電体層を含むSiO2上の一般的なCMOSプロセス温度で安定であり、n型Siの仕事関数に近い仕事関数を有する。第3アミルイミドトリス(ジメチルアミド)Ta(TAIMATA)などのアルキルイミドトリス(ジアルキルアミド)Ta化学種をTa前駆体として用いる化学的気相堆積方法によって、金属性Ta−N化合物を堆積する。この堆積は共形であり、これらのTa−N金属化合物のCMOSプロセスフローへの融通の利く導入を可能にする。TaNまたはTaSiNを用いて加工されたデバイスは、ほぼ理想的な特性を示す。

(もっと読む)

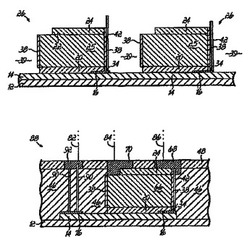

高さが異なる隆起したドレインおよびソース領域を有するトランジスタを形成するための先進技術

極めて小型の半導体デバイスにおけるエピタキシャル成長させた半導体領域の高さは、2つ以上のエピタキシャル成長を実行しうる異なるデバイス領域に対して、個別に調節することができる。エピタキシャル成長マスクは、特定のデバイス領域における半導体領域の形成を選択的に抑制する。他の実施形態において、2つ以上の異なるデバイス領域に対して、一般的なエピタキシャル成長プロセスを用いてもよく、選択されたエリアにあるすでにエピタキシャル成長させた半導体領域の高さを正確に低減するように、引き続き、選択されたデバイス領域に選択的酸化プロセスを実行することができる。  (もっと読む)

(もっと読む)

短チャネル効果を減少させる埋め込みチャネルフラッシュ構造

短チャネル効果を減少させたメモリセルを記載する。ソース領域(54)およびドレイン領域(56)を半導体ウェーハ(58)中に形成する。ソース領域(54)およびドレイン領域(58)の間にトレンチ領域(59)を形成する。このトレンチ領域、ソース領域およびドレイン領域の下に埋め込みチャネル領域(52)を形成する。半導体基板のトレンチ領域中にゲート絶縁層(60)を形成する。このゲート絶縁層は、埋め込みチャネル領域上に、およびソース領域とドレイン領域との間に形成される。埋め込みチャネル領域の上の半導体基板上に、制御ゲート層(70)を形成する。この制御ゲート層は、ゲート絶縁層によって埋め込みチャネルから分離される。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

全体的な設計目標を達成すべく、半導体デバイス中のキャリア移動度の可変な半導体デバイス

半導体デバイス(100)は、基板(110)、およびこの基板(110)上に形成される絶縁層(120)とを含む。第1デバイス(710)は第1フィン(130)を含む絶縁層(120)上に形成される。この第1フィン(130)は、絶縁層(120)上に形成され、第1アスペクト比を有する。第2デバイス(720)は、第2フィン(130)を含む絶縁層(120)上に形成される。この第2フィン(130)は、絶縁層(120)上に形成され、第1アスペクト比と異なる第2アスペクト比を有する。  (もっと読む)

(もっと読む)

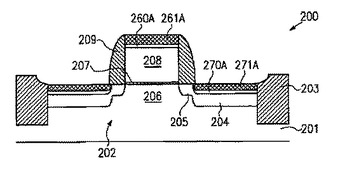

シリコン領域に形成されたニッケル/コバルトシリサイド領域を有する半導体デバイス

電界効果トランジスタのゲート電極などの、シリコン含有領域に、埋め込まれたニッケルシリサイド層(260A)、続いてコバルトシリサイド層(261A)を形成することによって、縮小されたシリコン回路構造のシート抵抗及び接触抵抗を過度に損なうことなく、デバイスを更に縮小することができるように、両シリサイドの優れた特性が組み合わせられる。  (もっと読む)

(もっと読む)

CMOS電界効果トランジスタを製造するための方法及び装置

【課題】 集積回路の製造におけるCMOS電界効果トランジスタを製造するための改善された方法、及び、トランジスタの金属ゲートの仕事関数を制御するための改善された方法を提供すること。

【解決手段】 トランジスタのゲート電極を含むポリシリコン材料を選択的にドープするステップと、完全にシリサイド化するステップとを含む、相補型金属酸化膜半導体(CMOS)電界効果トランジスタを製造する方法である。一実施形態において、シリサイド化する前に、ポリシリコンがアモルファス化される。更に別の実施形態において、シリサイド化が、低い基板温度で実行される。

(もっと読む)

1,981 - 2,000 / 2,010

[ Back to top ]