Fターム[5F110GG01]の内容

Fターム[5F110GG01]の下位に属するFターム

Fターム[5F110GG01]に分類される特許

2,001 - 2,020 / 3,651

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備えた保護回路等が必要となる。

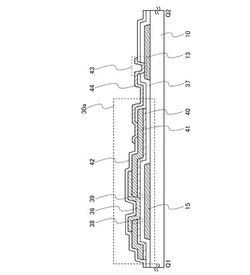

【解決手段】ゲート電極15を被覆するゲート絶縁層37と、ゲート絶縁層37上においてゲート電極15と端部が重畳し、第2酸化物半導体層40と導電層41が積層された一対の第1配線層38及び第2配線層39と、少なくともゲート電極15と重畳しゲート絶縁層37及び該第1配線層38及び該第2配線層39における導電層41の側面部及び上面部の一部と第2酸化物半導体層40の側面部と接する第1酸化物半導体層36とを有する非線形素子30aを用いて保護回路を構成する。

ゲート絶縁層37上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子30aの特性を向上させることができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産高く作製する方法を提案することを課題とする。

【解決手段】ゲート絶縁層上に、ドレイン電極層またはソース電極層を形成した後、低抵抗な酸化物半導体層をソース領域またはドレイン領域として形成し、その上に半導体層として酸化物半導体膜を形成することを要旨とする。好ましくは、半導体層として酸素過剰酸化物半導体層を用い、ソース領域及びドレイン領域として酸素欠乏酸化物半導体層を用いる。

(もっと読む)

電極の製造方法、これを用いた薄膜トランジスタ素子及び有機エレクトロルミネッセンス素子

【課題】透明導電性微粒子を含む流動性材料の塗布により、ゲート電極を形成する方法において、従来よりも低抵抗、かつ充分な表面平滑性をもった透明導電膜の製造方法を提供する。

【解決手段】ガラス基板106上に、金属酸化物微粒子(ITO)及び金属酸化物の前駆体を含む薄膜104”を塗布する。この薄膜にマイクロ波を照射することにより、前駆体が発熱体として作用し、焼成され、導電性薄膜を形成する。これをパターンニングしゲート電極104とする。ついで、ゲート絶縁膜105を形成し、半導体前駆体を塗布、乾燥し、半導体前駆体材料薄膜101’を得る。これにマイクロ波を照射することにより、ゲート電極が発熱し、この熱により半導体前駆体材料薄膜が加熱され、酸化物半導体膜に変換され半導体層101が形成される。マスクを介して金を蒸着し、ソース、ドレイン電極102,103を形成し、薄膜トランジスタとする。

(もっと読む)

電界効果型トランジスタ及びその製造方法

【課題】アモルファス酸化物を用いた薄膜トランジスタが、近紫外光がチャンネルに入射することで、TFTのトランジスタ特性(Id−Vg特性)が変動する場合に、TFT特性のばらつきを防止する、迷光の照射に伴う特性変動が小さい、酸化物からなる半導体膜をチャンネルに適用した電界効果型トランジスタ及びその製造方法を提供する。

【解決手段】酸化物半導体からなるチャンネル層11とオキシナイトライドからなるソース電極13及びドレイン電極14を有している。これにより、ソース電極13、ドレイン電極14から近紫外光がチャンネル層11に入りこむことがないため、光に対して比較的安定なTFTを実現できる。さらに、チャンネル層11とソース電極13、ドレイン電極14との間で、安定な電気接続が可能となり、素子の均一性、信頼性が向上する。

(もっと読む)

量子干渉トランジスタとその製造及び動作方法

【課題】量子干渉トランジスタとその製造及び動作方法を提供する。

【解決手段】量子干渉トランジスタとその製造及び動作方法について開示されている。該量子干渉トランジスタは、経路差を有する複数のチャンネルと、チャンネルのうち、少なくとも一つに設けられたゲートとを含む。該チャンネルは、グラフェンシートである。該経路差は、チャンネルを経由する電子の波動が、ドレインで相殺干渉または補強干渉を起こす経路差でありうる。

(もっと読む)

薄膜トランジスタおよびアクティブマトリクスディスプレイ

【課題】オン電流が高く、かつオフ電流が低い、つまり高いオンオフ比を持つ薄膜トランジスタを提供することを課題とする。

【解決手段】絶縁基板上に少なくともソース、ドレイン、ゲートの各電極と酸化物を含む半導体層とゲート絶縁層を有する薄膜トランジスタであって、該半導体層が第一の領域と、該第一の領域よりも該ゲート絶縁層に近い第二の領域を含み、且つ該第一の領域の導電率が、該第二の領域の導電率よりも低いことを特徴とする薄膜トランジスタとする。

(もっと読む)

インバータ及びその動作方法並びにインバータを含む論理回路

【課題】インバータ及びその動作方法並びにインバータを含む論理回路を提供する。

【解決手段】負荷トランジスタと駆動トランジスタとを含み、負荷トランジスタと駆動トランジスタとのうち、少なくとも一つは、ダブルゲート構造を有するインバータである。該ダブルゲート構造によって、負荷トランジスタまたは前記駆動トランジスタのスレショルド電圧が調節され、従って、該インバータは、E/D(enhancement/depletion)モードでありうる。

(もっと読む)

薄膜トランジスタ

【課題】薄膜トランジスタのオン電流及びオフ電流に係る問題点を解決することを課題の一とする。高速動作が可能な薄膜トランジスタを提供することを課題の一とする。

【解決手段】薄膜トランジスタにおいて、ゲート絶縁層と、ソース領域及びドレイン領域との間であって、且つ少なくともソース領域及びドレイン領域側に、窒素、NH基、またはNH2基を有する非晶質半導体層をバッファ層として有する。非晶質半導体をチャネル形成領域に有する薄膜トランジスタと比較して、薄膜トランジスタのオン電流を高めると共に、微結晶半導体をチャネル形成領域に有する薄膜トランジスタと比較して、薄膜トランジスタのオフ電流を低減することができる。

(もっと読む)

ディスプレイ用薄膜トランジスタ基板及びその製造方法

【課題】ソース−ドレイン領域の半導体膜と走査線の下にある半導体膜とが接続されていることに起因して生じる不具合をなくすことができる、アクティブマトリクス方式のディスプレイ用薄膜トランジスタ基板を提供する。

【解決手段】基板10側から、少なくとも、半導体膜13、ゲート絶縁膜14g、ゲート電極15gの順で設けられたTFT20を有するアクティブマトリクス方式のディスプレイ用薄膜トランジスタ基板1において、ゲート電極15gをその一部として含む走査線31が所定の隙間Gを隔てて分断された導電性パターン32と、その導電性パターン32の下に設けられた半導体膜13と、分断された導電性パターン32を接続する配線膜33とを有するように構成した。

(もっと読む)

表示装置

【課題】

良好な特性を有するスタガ型の多結晶Si−TFT構造と、ディスプレイの大型化に有利な低抵抗配線構造を両立でき、低コストで高画質の表示装置を提供する。

【解決手段】

マトリックス状に配置された複数の画素を駆動するTFTをスタガ型の多結晶Si−TFTで構成し、該TFTのチャネルを形成する多結晶Si層4より下層に位置する電極配線2を、希土類元素を添加元素として含むAl合金からなる第一の合金層2aと、希土類元素と高融点金属とAlとの合金からなり、前記第一の層の上層に位置する第二の合金層2bとの積層構造とすることで、多結晶Si形成時の高温に耐え得る低抵抗配線構成とした。

(もっと読む)

薄膜トランジスタ

【課題】逆スタガ薄膜トランジスタの電気特性を高めることを目的とする。

【解決手段】基板上に、ゲート電極層と、半導体層と、ゲート電極層及び半導体層の間に設けられるゲート絶縁層と、半導体層に接するソース領域及びドレイン領域と、ソース領域に接するソース電極と、ドレイン領域に接するドレイン電極とを有する。さらに、ソース領域及びドレイン領域は、一導電型を付与する不純物が添加された微結晶半導体層で形成され、半導体層において、ソース領域及びドレイン領域と接する領域は結晶領域で形成されている。さらに、半導体層における結晶領域は、バックチャネル領域に形成されておらず分離されているため、対をなす。さらに、半導体層において、非晶質半導体を含む。

(もっと読む)

横方向成長半導体ナノワイヤの製造方法とその方法により得られたトランジスタ

【課題】

【解決手段】 発明は、金属酸化物層(2)を有する基板(1)上に半導体ナノワイヤ(5)を製造する方法であって、

a)前記層(2)を還元して前記金属酸化物層(2)の表面上に半径(Rm)の金属ナノドロップ(3)を形成するのに適した時間tの間出力Pの水素プラズマ(11)を前記金属酸化物層(2)に照射するステップと、

b)前記金属ナノドロップ(3)を含む前記金属酸化物層(2)上への、前記金属ナノドロップ(3)を被覆するのに適した厚さ(Ha)を有する半導体材料の薄層(4)の低温プラズマ助長蒸着ステップと、

c)前記金属ナノドロップ(3)から薄層(4)として堆積された前記材料の触媒作用によりナノワイヤ(5)の横方向成長を促進するのに十分な温度Tにおいて熱アニールするステップと

を含む半導体ナノワイヤ(5)を製造する方法を提供する。発明はまた、発明の方法により得られたナノワイヤ(5)と、半導体ナノワイヤ(5)、例えばソース(16)、ドレイン(17)、及びゲート(18)間に半導体接続部を形成するシリコンナノワイヤ(SiNW)を含むナノメータトランジスタとを提供する。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、および電子機器

【課題】基板やゲート絶縁膜の露出表面と、ソース電極およびドレイン電極の露出表面とに、良好で均一な膜質の半導体薄膜を設けることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ1aは、有機材料または酸化物材料またはシリコン系材料からなるゲート絶縁膜(絶縁層)15上に、導電性酸化物材料からなる酸化物材料層17-aとこの上部の金属材料層17-bとからなるソース電極およびドレイン電極が設けられたものである。そしてゲート絶縁膜(絶縁層)15とソース電極17sおよびドレイン電極17dとにおける酸化物材料層17-aとの露出面が、自己組織化膜19で覆われており、この自己組織化膜19で覆われた上部のソース電極17s−ドレイン電極17d間にわたって半導体薄膜21が設けられている。

(もっと読む)

アモルファス酸化物半導体及び該アモルファス酸化物半導体を用いた薄膜トランジスタ

【課題】 トランジスタ特性に優れたアモルファス酸化物薄膜トランジスタを提供する。

【解決手段】 In又はZnの少なくとも一方の元素と水素とを含むアモルファス酸化物半導体であって、前記アモルファス酸化物半導体が1×1020cm−3以上1×1022cm−3以下の水素原子又は重水素原子を含有しており、かつ、前記アモルファス酸化物半導体中で、過剰な酸素(OEX)(ここで、該過剰な酸素とは、前記アモルファス酸化物半導体の一部分の数原子サイズを単位として見た際のミクロな領域において過剰な状態にある酸素である)と水素の結合(OEX−H結合及びH−OEX−H結合)を除く、酸素と水素の結合(O−H結合)の密度が1×1018cm−3以下であることを特徴とするアモルファス酸化物半導体。

(もっと読む)

絶縁膜及び当該絶縁膜を備えた半導体デバイス

【課題】シロキサンポリマーと下地との密着を高めることができる絶縁膜及び当該絶縁膜を備えた半導体デバイスを提供すること。

【解決手段】この薄膜トランジスタ10は、基板12を備え、その基板12の上面には、ソース電極15及びドレイン電極16が、所定のチャネル長の離間幅をもって各々設けられている。また、ソース電極15及びドレイン電極16の間を埋めるように、半導体層17が形成され、当該半導体層17上には、ゲート絶縁膜13が設けられている。ゲート絶縁膜13上には、ゲート電極11が設けられている。また、基板12、ソース電極15、ドレイン電極16、ゲート絶縁膜13及びゲート電極11を覆うようにポリシラザン層19が形成されている。そして、ポリシラザン層19の上側には、シロキサンポリマーからなる層間絶縁膜14が形成されている。

(もっと読む)

半導体装置、電子書籍、電子機器、及び半導体装置の作製方法

【課題】半導体膜に混入する不純物濃度を制御した活性層を有する半導体回路を備えた半導体装置を提供するものである。

【解決手段】上記目的を解決するため、ガラス基板上に200nm〜500nmの膜厚の第1の窒化珪素膜と、前記第1の窒化珪素膜上に第2の窒化珪素膜と、前記第2の窒化珪素膜上にチャネル形成領域となる領域を含む非晶質半導体膜と、を有する構成において、前記第1の絶縁膜と前記第2の絶縁膜との界面において、ボロンを有する。

(もっと読む)

半導体素子

【課題】界面準位を意図的に形成−消滅させることにより素子特性を制御した構成の、高性能なスイッチング素子やメモリ素子を提供する。

【解決手段】半導体素子1は、界面準位制御層5と、半導体層4と、ソース電極2と、ドレイン電極3と、ゲート電極7と、ゲート絶縁膜6と、基板8とを層状に積層してなり、界面準位制御層5の1側面にゲート絶縁膜6を設けて構成する。微小な外部からの入力信号(外場)をこの界面準位制御層5で受け、界面準位の形成−消滅を切り替えることにより増幅された出力信号として高感度に取り出す。

(もっと読む)

半導体装置の作製方法

【課題】ソース電極層及びドレイン電極層表面に酸化物や汚染物の皮膜が生じたまま、その上に酸化物半導体層を形成すると、ソース電極層またはドレイン電極層と酸化物半導体膜との接触面に電気的に高抵抗な界面が形成され、半導体素子のオン電流が抑制されてしまう。

【解決手段】ソース電極層及びドレイン電極層の表面をプラズマでスパッタリング処理し、当該ソース電極層及びドレイン電極層を大気にさらすことなく、当該ソース電極層及びドレイン電極層上に連続してIn、Ga、及びZnを含む酸化物半導体層を形成する。

(もっと読む)

電界効果型トランジスタ及びその製造方法並びに画像表示装置

【課題】電界効果型トランジスタにおいて、半導体形成が簡便であり、かつ半導体形成によって前記上部画素電極への電圧の印加に問題が生じないようにバンク層を用いた構造を提供すること。

【解決手段】ゲート電極と、前記ゲート電極を覆うゲート絶縁層と、ソース電極と、下部画素電極と、前記下部画素電極に接続されたドレイン電極と、前記ソース電極及び前記ドレイン電極の間に形成された半導体と、前記半導体を囲み、前記下部電極を覆うように形成されたバンク層と、少なくとも前記下部画素電極上に開口部を有する層間絶縁層と、前記バンク層を介して前記下部画素電極に静電接続された上部画素電極とを備えることを特徴とする電界効果型トランジスタとする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体層を有する薄膜トランジスタにおいて、水分などの不純物を混入させずに良好な界面特性を提供することを課題の一つとする。電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産高く作製する方法を提案することを課題とする。

【解決手段】ゲート絶縁層表面に酸素ラジカル処理を行うことを要旨とする。よってゲート絶縁層と半導体層との界面に酸素濃度のピークを有し、かつゲート絶縁層の酸素濃度は濃度勾配を有し、その酸素濃度はゲート絶縁層と半導体層との界面に近づくにつれて増加する。

(もっと読む)

2,001 - 2,020 / 3,651

[ Back to top ]