Fターム[5F110GG01]の内容

Fターム[5F110GG01]の下位に属するFターム

Fターム[5F110GG01]に分類される特許

3,641 - 3,651 / 3,651

半導体基板におけるドーパントの拡散を低速化する方法およびこれにより製造されたデバイス

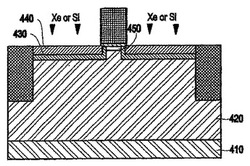

【課題】 ひずみSi/Si1-XGeXデバイス基板において、極めて浅い接合を形成する方法およびそれによって得られる半導体構造を提供する。

【解決手段】 半導体デバイスを形成する方法(およびその結果として得られる構造)は、基板上に、ドーパントおよび少なくとも1つの種を注入するステップと、基板をアニールするステップであって、少なくとも1つの種が、基板のアニールの間のトーパントの拡散を遅らせるステップと、を含む。

(もっと読む)

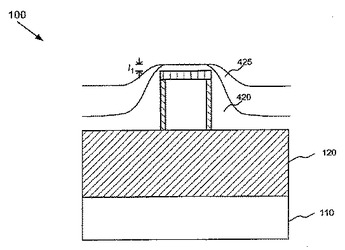

化学機械研磨プレーナ化のためのデュアルシリコンゲート層を有するFINFET

FinFETタイプの半導体デバイスは、フィン構造(210)を含んでいる。この上には、比較的薄いアモルファスシリコン層(420)を形成し、それから非ドープポリシリコン層(425)を形成する。この半導体デバイスは、アモルファスシリコン層(420)がフィン構造の損傷を防ぐ停止層として働く化学機械研磨(CMP)を使用してプレーナ化することができる。  (もっと読む)

(もっと読む)

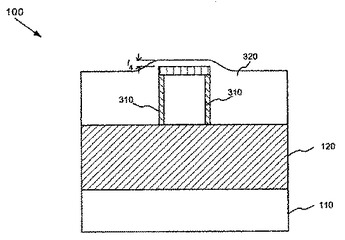

FINFET中のゲート領域のマルチステップ化学機械研磨

チャネル上にたい積されるゲート材料層(320)をプレーナ化するステップを含む、MOSFET型の半導体デバイスを製造する方法である。このプレーナ化は、第1の”荒い”プレーナ化と、その後の”緻密な”プレーナ化を含んだ複数のステッププロセスで実行される。より緻密なプレーナ化で使用されるスラリーは、ゲート材料の低い領域に付着し易い付加材料を含んでいてもよい。  (もっと読む)

(もっと読む)

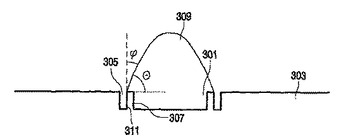

半導体構成用の構造およびその製造方法

本発明は、半導体構成用の構造に関する。半導体を含む溶液の堆積を補助するレジスト構造は、直接、あるいは介在層を介して基板に結合される。このレジスト構造は、半導体を含む溶液(309)を堆積するくぼみ(301)と、くぼみ(309)の縁部の少なくとも一部に整列し、突出部(307)によってくぼみ(309)から分離した溝(305)とを備える。好ましくは、溝(305)は、くぼみ(309)を取り囲む。この溝により、半導体を含む溶液を固定する作用が得られ、それによって濡れ性が改善し、それにしたがって、より大きな体積の半導体を所与の区域に付着させることができる。  (もっと読む)

(もっと読む)

絶縁ゲート型電界効果トランジスタを含む半導体装置及びその製造方法

【課題】シリコン基板上のSi1−xGex層を用いた素子構造において、電流駆動能力の高いMISFETを含む半導体装置及びその製造方法を提供することにある。

【解決手段】シリコン基板101上に、Si1−xGex層103を形成し、このSi1−xGex層103にMISFETを形成する。ソース層及びドレイン領域106,107の接合深さを、前記Si1−xGex層103とシリコン層とが接する面を越えないようにする。

(もっと読む)

発光装置およびその作製方法

【課題】アクティブマトリクス型の発光装置における光の取り出し効率を向上させる手段を提供する。

【解決手段】アクティブマトリクス型の発光装置において、第1の凹部101a〜第3の凹部101cを有する第1の基板100に金属膜102a〜第3の金属膜102cを形成することや、画素電極145、有機層148、凸部149aの表面を有する陰極149からなる発光素子150を形成することにより、光の損失や隣の画素への光漏れを防ぐことができる。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】 電気特性の優れた多結晶TFTを提供する。

【解決手段】多結晶膜3を堆積させる工程、堆積した多結晶膜のうち所望の位置4のみを残すようにエッチングする工程、残された部分的な多結晶膜の中で所望の結晶方位の結晶粒5だけを、しかも所望の結晶面(ファセット)6を出した状態になるように異方性エッチングする工程、さらに、こうして得られた結晶核の上に膜を堆積し結晶化させる工程を用いる。

(もっと読む)

薄膜トランジスタアレイ及びその製造方法、液晶表示装置及びその製造方法とエレクトロルミネッセンス表示装置及びその製造方法

【課題】 本発明は薄膜トランジスタアレイ及びその製造方法と液晶表示装置及びその製造方法とエレクトロルミネッセンス表示装置及びその製造方法に関するものであり、均一性と性能に優れた薄膜トランジスタ及びその製造方法を生産性が高く低コストで提供することを目的とする。

【解決手段】 ゲート電極側面に側壁を形成することによって、自己整合的にLDDまたはオフセット領域を形成し、また、層間絶縁膜を複数の層で形成し、これら複数の層間絶縁膜上にソース・ドレイン電極とソースバス配線と画素電極を一括して形成する。

(もっと読む)

MOS型センサおよびその駆動方法

【課題】 最適な蓄積時間を素早く見つける駆動方法を提供する。

【解決手段】 複数の画素を有するMOS型センサにおいて、複数の画素の全ての画素を同時にリセットした後、前記複数の画素から信号を順に出力し、前記リセットをした時から、前記複数の画素が、飽和した信号を出力する直前までの期間を、蓄積時間とすることを特徴とするMOS型センサの駆動方法が提供される。

(もっと読む)

液晶表示装置およびその作製方法

【課題】 IPS方式の液晶表示装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現する。

【解決手段】 本発明では、チャネル・エッチ型のボトムゲートTFT構造を採用し、ソース領域119及びドレイン領域120のパターニングとソース配線121及び画素電極122のパターニングを同じフォトマスクで行うことを特徴とする。

(もっと読む)

半導体膜形成方法及び薄膜半導体装置の製造方法

【課題】 本発明の目的は、基板上に高品質な半導体膜を形成するための半導体膜形成方法を提供することにある。

【解決手段】 本発明は、バイアス触媒CVD,高密度バイアス触媒CVD,バイアス減圧CVD,バイアス常圧CVDを利用して、基板に半導体膜を形成する半導体膜形成方法である。真空容器1に原料ガスを供給し、真空容器1中に配置された基板10と電極3aとの間にグロー放電開始電圧以下の電界を印加して、基板10上に、少なくとも錫、ゲルマニウム、鉛のいずれか一つ以上を含有する半導体膜と、絶縁膜と、を形成することを含む工程と、この半導体膜および絶縁膜にレーザーを照射してアニールする工程と、このアニールする工程の後工程であって、水蒸気でアニールを行う工程と、を備える。

(もっと読む)

3,641 - 3,651 / 3,651

[ Back to top ]