Fターム[5F110HJ18]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物領域の製法 (6,364) | 不純物の導入方法 (4,201) | 拡散 (325) | 気相拡散(雰囲気中) (184) | プラズマ雰囲気中 (150)

Fターム[5F110HJ18]に分類される特許

81 - 100 / 150

半導体装置及び半導体装置の製造方法

【課題】配線層に新たな機能を有する素子を設けた半導体装置を提供する。

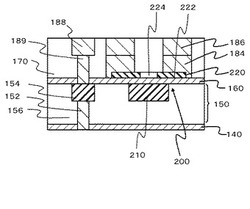

【解決手段】半導体基板上に形成された第1配線層150、及び半導体素子200を備える。第1配線層150は、絶縁層156と、絶縁層156の表面に埋め込まれた第1配線154とを備える。半導体素子200は、半導体層220、ゲート絶縁膜160、及びゲート電極210を備える。半導体層220は、第1配線層150上に位置する。ゲート絶縁膜160は、半導体層220の上又は下に位置する。ゲート電極210は、ゲート絶縁膜160を介して半導体層220の反対側に位置する。

(もっと読む)

半導体装置及びその製造方法

【課題】所望の特性が得られるフィン型CMISFETを実現する。

【解決手段】ゲート絶縁膜14bの外側に位置するn型のフィン型半導体領域13bにおける上部コーナーの曲率半径r1’は、ゲート絶縁膜14bの下側に位置するn型のフィン型半導体領域13bにおける上部コーナーの曲率半径r1よりも大きく且つ2×r1以下である。ゲート絶縁膜914cの外側に位置するp型のフィン型半導体領域913cにおける上部コーナーの曲率半径r2’は、ゲート絶縁膜914cの下側に位置するp型のフィン型半導体領域913cにおける上部コーナーの曲率半径r2よりも大きく且つ2×r2以下である。

(もっと読む)

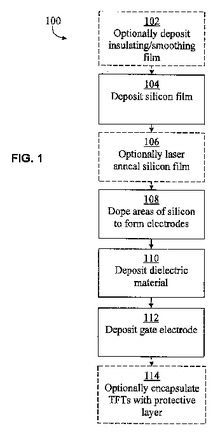

シリコン薄膜トランジスタ、並びにその製造システム及び方法

可撓性基板上に、自己整合シリコン薄膜トランジスタを製造するシステム及び方法。前記システム及び方法は、高いパフォーマンスのトランジスタを製造するために、精密さ、レゾリューション、レジストレーションが達成されるよう、レーザアニール、エッチング技術、レーザドーピングを全て低温度で行いつつ、化学気相堆積、プラズマエンハンスト気相堆積、プリント、コーティング、及び他の堆積処理といった堆積処理を組み込むとともに組み合わせている。そのようなTFTはディスプレイ、パッケージング、ラベリング等に使用できる。  (もっと読む)

(もっと読む)

半導体素子及びその製造方法並びに表示装置

【課題】駆動力向上、サブスレッショルド係数低減、オフ電流低減、駆動電圧の低減等トランジスタ特性の高性能化、低消費電力化を実現する半導体素子を提供する。

【解決手段】基板101上に設けられた導電性電極103と、導電性電極103上に設けられた絶縁膜104と、絶縁膜104を介して導電性電極103上部に設けられた半導体105と、半導体105の両側に、絶縁膜104に接して設けられた導電性領域109とを備える。

(もっと読む)

薄膜トランジスタおよびその製造方法、並びにそれらを用いた液晶表示装置

【課題】安定した素子特性および良好な信頼性を実現する薄膜トランジスタおよびその製造方法、並びにそれらを用いた液晶表示装置を提供する。

【解決手段】薄膜トランジスタ14は、透光性基板1上において、多結晶シリコンの半導体層3上に積層するゲート絶縁膜4およびゲート電極6、及び、上記半導体層3のソース領域8、ドレイン領域9およびチャネル領域10を有する。そして、前記ゲート絶縁膜4は酸化シリコン膜4aからなり、ゲート電極6の底面と接する上記酸化シリコン膜4aの少なくとも表面は酸窒化シリコン層4bから成っている。ここで、ゲート電極6は、例えば500℃程度の比較的に低温で酸化シリコン膜と化学反応する高融点金属材料を含んで構成されている。

(もっと読む)

半導体装置

【課題】動作性能及び信頼性の高い半導体装置を提供する。

【解決手段】スイッチング用TFT4802及び消去用TFT4807のLDD領域は、ゲート電極に重ならないように形成されており、オフ電流値の低減に重点を置いた構造となっている。電流制御用TFT4804のLDD領域は、その一部又は全部がゲート電極に重なるように形成されており、オン電流値の確保と、ホットキャリア注入の防止に重点を置いた構造となっている。各部に求められる機能に応じて、同一基板上に異なる構造のTFTを、共通の工程にて形成することで、半導体装置の動作性能及び信頼性を向上する。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】同一の基板上にスイッチング素子と光センサ素子を形成する場合に、光センサ素子の感度が上げるために、活性層の膜厚を厚くすると、スイッチング素子(TFT)の特性に悪影響を及ぼしてしまう。

【解決手段】複数の画素がマトリクス状に配置されるガラス基板5上に、画素のスイッチング素子となる薄膜トランジスタを構成するチャネル層25と、光センサ素子を構成する光電変換層35とを有する表示装置の構成として、外光が入射する側と反対側で光電変換層35に最も近接して対向配置される電極33の表面に光反射膜34を形成した。

(もっと読む)

半導体装置の作製方法

【課題】ソース領域及びドレイン領域よりチャネル形成領域の膜厚が薄いS値の向上されたボトムゲート型薄膜トランジスタを簡単な工程で作製可能な半導体装置の作製方法を提供する。

【解決手段】絶縁性基板の表面のチャネル形成領域に対応する箇所に島状導電膜を形成し該島状導電膜を絶縁膜で覆って凸部を形成する。形成された凸部を覆うアモルファス半導体膜を成膜した後、レーザ光を照射して半導体膜を溶融状態にして結晶化する。凸部上の溶融した半導体は凸部の両側に隣接する領域へと流れ、それによって凸部上に位置する半導体膜(チャネル形成領域)が薄膜化される。

(もっと読む)

半導体装置及び半導体装置の作製方法、並びに電子機器

【課題】簡単な工程でソース領域及びドレイン領域に悪影響を与えることなくチャネル形成領域の薄膜化が可能な半導体装置及びその作製方法を提供する。

【解決手段】半導体装置の作製方法において、凸部を有する絶縁性基板の表面に凸部の高さより小さい厚さを有する半導体膜を形成し、この半導体膜をレジストをマスクにして島状にエッチングした後、レジストをエッチングして凸部上面を覆う半導体膜の部分を露出し、この露出された半導体膜の部分をエッチングにより薄膜化する際、凸部の両側に隣接する部分を覆う半導体膜がレジストに覆われたままとする。

(もっと読む)

半導体記憶装置とその製造方法

【課題】動作速度および信号差を維持したまま、セルサイズを縮小しかつ電極間の短絡を防止することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1の方向に延在する半導体層31と、半導体層内に設けられたソース層S、ドレイン層D、および、ボディBと、第1の方向に延在するビット線BLと、ボディの第1の側面SF1に第1のゲート絶縁膜GD1を介して設けられた第1のゲート電極GE1と、第1の方向へ延在し、第1のゲート電極の底部に接続され、第1のゲート電極と同一材料で一体形成された第1のゲート線GL1と、第1の側面の反対側にあるボディの第2の側面SF2に設けられ第2のゲート絶縁膜GD2を介して設けられた第2のゲート電極GE2と、第1の方向に対して交差する第2の方向へ延在し、第2のゲート電極の上部に接続され、第2のゲート電極と同一材料で一体形成された第2のゲート線WLとを備える。

(もっと読む)

半導体装置

【課題】素子特性のばらつきが抑制されたMOS型素子を含む半導体装置を提供すること。

【解決手段】基板の半導体領域に埋め込まれた素子分離絶縁膜と、前記素子分離絶縁膜によって素子分離され、上部が前記素子分離絶縁膜の表面よりも上に突出し、前記半導体領域の半導体層と、この半導体層にソース・ドレイン領域、ゲート絶縁膜およびゲート電極が形成され、かつ、前記ゲート電極がチャネル幅方向に平行な面の断面において前記素子分離絶縁膜上に形成されてなるMOS型素子とを具備してなり、前記ゲート電極下の前記半導体層の上面位置が、前記ゲート電極下の前記素子分離絶縁膜の上面位置よりも、20nm以上高いことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】性能の低下を抑えつつ微細化に対応可能な半導体装置及びその製造方法を提供する。

【解決手段】共通の支持体上に設けられたトランジスタとキャパシタとを備え、トランジスタは、表層部に選択的に設けられたソース領域とドレイン領域とを有する第1の半導体フィンと、第1の半導体フィンにおけるソース領域とドレイン領域との間の部分の少なくとも側面に対向して設けられたゲート電極と、ゲート電極と第1の半導体フィンとの間に介在された絶縁膜とを有し、キャパシタは、隣り合うものどうしが互いに側面を対向させている複数の第2の半導体フィンと、第2の半導体フィン間に埋め込まれた誘電体膜とを有する。

(もっと読む)

半導体装置の作製方法

【課題】活性層、特にチャネル形成領域を構成する領域とゲート絶縁膜との界面を良好なものとすることにより、TFTの特性を向上させるとともに均一な特性を有する半導体装置およびその作製方法を提供するものである。

【解決手段】絶縁表面上にゲート配線を形成し、ゲート配線上にゲート絶縁膜と、半導体膜とを順次大気にふれることなく積層形成し、赤外光または紫外光を照射することにより半導体膜を結晶化して結晶性半導体膜を形成すると同時に保護膜として機能する酸化膜を形成し、結晶性半導体膜のチャネル形成領域となるべき領域に、光感光性有機材料でなるマスクを形成し、酸化膜を介して結晶性半導体膜のソース領域またはドレイン領域となるべき領域に不純物元素の添加を行う半導体装置の作製方法である。

(もっと読む)

薄膜トランジスタアレイ、その製造方法及び液晶表示装置

【課題】 酸化物半導体膜を用いた従来の薄膜トランジスタアレイでは、外部駆動回路と薄膜トランジスタアレイの信号線端子との良好な接続を確保できるアレイ構造は実現されていなかった。

【解決手段】 薄膜トランジスタのチャネル部14、ソース部15、ドレイン部16と、画素電極13と、ゲート信号線11及びソース信号線12の端部の接続用端子部18、17も同一の酸化物半導体で形成する。薄膜トランジスタアレイにおける全ての層構造を形成後、最上層の保護絶縁膜19の所望の位置に開口部を設ける。そして、開口部を介して酸化物半導体膜26を還元性プラズマあるいはドーピング元素を含むプラズマに曝すことにより、接続用端子部18、17、ソース・ドレイン部15、16、画素電極13を同時に低抵抗化する。

(もっと読む)

半導体装置

【課題】 本発明は、同一基板上に同時に異なるLDD構造を有する生産性の高いTFTの作製方法およびその構造を提供することを目的としている。即ち、本発明はTFTの新規な構造と生産性の高い製造工程を提供するものである。

【解決手段】 耐熱性の高いTa膜またはTaを主成分とする膜を配線材料に用い、さらに保護層で覆うことで、高温(400〜700℃)での加熱処理を施すことが可能となり、且つ保護層をエッチングストッパーとして用いることで周辺駆動回路部においては、サイドウォール126を用いた自己整合プロセス(セルフアライン)によるLDD構造を備えたTFTを配置する一方、画素マトリクス部においては、絶縁物125を用いた非自己整合プロセス(ノンセルフアライン)によるLDD構造を備えたTFTを配置する

(もっと読む)

半導体装置及び当該半導体装置を具備する電子機器

【課題】無線通信によりデータの交信が可能な半導体装置において、復調信号を基に生成したクロックを利用するために引き起こされる誤動作するまたは応答しない等の動作不良を防止することを課題とする。

【解決手段】無線信号を受信するためのアンテナ回路と、アンテナ回路で受信した前記無線信号により電源を生成する電源回路と、電源が供給されるクロック発生回路と、を有し、クロック発生回路には、自己発振するリングオシレータと、リングオシレータの出力信号を適切な範囲の周波数に調整する分周器を設け、周波数の精度が高いクロックをもってディジタル回路部を駆動することで、誤動作するまたは応答しない等の動作不良を防止する。

(もっと読む)

半導体薄膜改質装置

【課題】ステージと基板との位置ずれを抑制することにより、所望の領域のみにレーザを照射することができるようにする。

【解決手段】半導体材料の付着した基板を所定の基板載置部に収納可能とする密閉容器と、半導体材料に照射されて半導体材料を所定の熱処理温度まで加熱するための光を照射する光源と、密閉容器に設けられて光源からの光を透過して密閉容器内に導入するための光透過窓と、基板載置部に設けられて基板を基板載置部に固定保持するための保持手段と、光の照射時における密閉容器内の雰囲気圧力を、光照射によって溶融加熱された半導体材料の温度によって規定される蒸気圧を下まわらないように制御する圧力制御手段とを備える。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、同一基板上に同時に異なるLDD構造を有する生産性の高いTFTの作製方法およびその構造を提供することを目的としている。即ち、本発明はTFTの新規な構造と生産性の高い製造工程を提供するものである。

【解決手段】 耐熱性の高いTa膜またはTaを主成分とする膜を配線材料に用い、さらに保護層で覆うことで、高温(400〜700℃)での加熱処理を施すことが可能となり、且つ保護層をエッチングストッパーとして用いることで周辺駆動回路部においては、サイドウォール126を用いた自己整合プロセス(セルフアライン)によるLDD構造を備えたTFTを配置する一方、画素マトリクス部においては、絶縁物125を用いた非自己整合プロセス(ノンセルフアライン)によるLDD構造を備えたTFTを配置する

(もっと読む)

半導体装置

【課題】金属元素を用いて結晶化させた珪素膜を活性層として用いた半導体装置において、金属元素による半導体装置の特性への悪影響を排除する。

【解決手段】 珪素の結晶性を助長する金属元素を用いて結晶化させた結晶性珪素膜を活性層とする半導体装置において、ソース領域またはドレイン領域が形成される領域114、116に燐をドーピングし、加熱処理を施す。その際、領域115に存在する金属元素が、120、121で示されるように、燐がドーピングされた領域にゲッタリングされる。その結果、チャネル領域または低濃度不純物領域が形成される領域117乃至119における金属元素の濃度を低くすることができる。

(もっと読む)

半導体装置

【課題】多数の画素のそれぞれにスイッチング用の薄膜トランジスタを配置し、各画素電極に出入りする電荷をこの薄膜トランジスタで制御する液晶表示装置、EL表示装置等の半導体装置において、良好な表示特性を有し、長期の信頼性を有する半導体装置を提供する。

【解決手段】基板上方にゲイト電極、ゲイト電極上方のゲイト絶縁膜、及びゲイト絶縁膜上方の活性層を有する薄膜トランジスタと、薄膜トランジスタ上方の窒化珪素でなる絶縁膜と、絶縁膜上方の樹脂膜と、樹脂膜上方に薄膜トランジスタに接続する画素電極とを有することにより、良好な表示特性を有し、長期の信頼性を有する半導体装置を提供する。

(もっと読む)

81 - 100 / 150

[ Back to top ]