Fターム[5F110HK03]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 金属 (18,241) | Al (3,898)

Fターム[5F110HK03]に分類される特許

2,001 - 2,020 / 3,898

半導体ポリマーを備える電子デバイス

【課題】空気中で安定な高い移動度を有するn型半導体材料あるいはn型およびp型両方の半導体材料である半導体ポリマーを含む電子デバイスを提供する。

【解決手段】半導体層を備え、該半導体層が下記式(I)の半導体ポリマーを含む電子デバイスである。

式(I)

(上記式(I)中、Xは、独立に、S、Se、OおよびNRから選択され、Rは、独立に、水素、アルキル、置換アルキル、アリール、置換アリール、ヘテロアリールおよび−CNから選択され、Arは、独立に、共役二価部分であり、aは、1〜約10の整数であり、nは、2〜約5,000の整数である。)

(もっと読む)

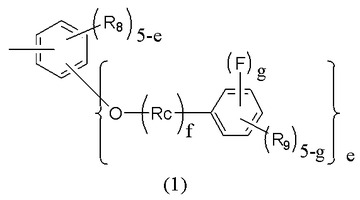

π共役系高分子及びその製造方法、並びに電荷輸送材料及び有機電子デバイス

【課題】分子量および分子量分布は制御が可能な連鎖重合をπ共役系高分子の合成に適用し、これまで困難であったπ共役高分子のブロック共重合体を得ること。該電荷輸送材料を用いた有機デバイスを提供すること。

【解決手段】下記式(1)で表わされるモノマーを、ニッケル触媒の存在下重合し、さらに下記式(2)で表わされるモノマーを重合する。

(上記式(1)中、X1〜X2は各々独立してハロゲン原子を表わし、Rはマグネシウム又は亜鉛を表わし、Aは置換されてもよい二価の共役五員複素環基表わす。)

(上記式(2)中、X3〜X4は各々独立してハロゲン原子を表わし、Rはマグネシウム又は亜鉛を表わし、Arは上記式(1)のAとは異なる二価の芳香族基を表わす。)

(もっと読む)

電子デバイス

【課題】既知の薄膜トランジスタの性能を改良する。

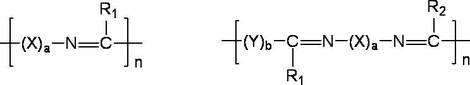

【解決手段】半導体層を含む電子デバイスであって、該半導体層が、式(I)および(II):

式(I) 式(II)

(式中、R1およびR2は、独立して、水素、アルキル、置換アルキル、アリール、置換アリール、およびヘテロアリールから選択され、XおよびYは、独立して、共役二価部分であり、aおよびbは、独立して、0から10までの整数であり、nは、2から5,000までの整数である)からなる群から選択される半導体ポリマを含む電子デバイスである。

(もっと読む)

薄膜電界効果型トランジスタ及びその製造方法

【課題】活性層にアモルファス酸化物半導体を用いたTFTで、閾値電圧の変動のない安定性に優れたTFT、及びその製造方法の提供。

【解決手段】基板1上に、ゲート電極2、ゲート絶縁膜3、アモルファス酸化物半導体層4と、ソース電極5−1及びドレイン電極5−2を有する薄膜電界効果型トランジスタであって、ソース電極5−1及びドレイン電極5−2がアモルファス酸化物半導体層4の厚みの3倍以上の厚みを有し、ソース電極5−1及びドレイン電極5−2が互いに対向する各々の側端部に該厚みが傾斜したテーパー部を有す。

(もっと読む)

薄膜電界効果型トランジスタ及びその製造方法

【課題】活性層にアモルファス酸化物半導体を用いたTFTで、連続駆動しても閾値電圧の変動のない駆動安定性に優れたTFT及びその製造方法の提供。

【解決手段】基板1上に、ゲート電極2、ゲート絶縁膜3、アモルファス酸化物半導体層4と、ソース電極5−1及びドレイン電極5−2を有する薄膜電界効果型トランジスタであって、ゲート電極2とソース電極5−1及びドレイン電極5−2の少なくとも一方とが平面上重なりを有せず、ゲート電極2側端部とソース電極5−1及びドレイン電極5−2の少なくとも一方の側端部との隙間が、0.2μm以上5μm以下とする。

(もっと読む)

ピンホールアンダーカット部を含む装置と工程

【課題】ピンホールの悪影響の軽減された新たな電子デバイスと新たな電子デバイス製造方法を提供する。

【解決手段】入口92Aと出口94Aのある複数のピンホール90Aを有する誘電領域14と、下側導電領域18とを備え、ピンホール90Aの少なくともいくつかは出口94A周辺において出口94Aより広い下側導電領域18のアンダーカット部96Aに面する誘電領域14の張り出し面98Aを持たせる

(もっと読む)

半導体ポリマおよび半導体ポリマを調製する方法

【課題】既知の薄膜トランジスタの性能を改良する。

【解決手段】式(I)および(II):

式(I) 式(II)

(式中、R1およびR2は、独立して、水素、アルキル、置換アルキル、アリール、置換アリール、およびヘテロアリールから選択され、XおよびYは、独立して、共役二価部分であり、aおよびbは、独立して、0から10までの整数であり、nは、2から5,000までの整数である)からなる群から選択される半導体ポリマである。

(もっと読む)

半導体ポリマー

【課題】空気中で安定な高い移動度を有するn型半導体材料あるいはn型およびp型両方の半導体材料である半導体ポリマーを提供する。

【解決手段】下記式(I)の半導体ポリマーである。

式(I)

(上記式(I)中、Xは、独立に、S、Se、OおよびNRから選択され、Rは、独立に、水素、アルキル、置換アルキル、アリール、置換アリール、ヘテロアリールおよび−CNから選択され、Arは、独立に、共役二価部分であり、aは、1〜約10の整数であり、nは、2〜約5,000の整数である。)

(もっと読む)

ラダー型化合物及び有機半導体材料

【課題】ラダー型化合物を提供すること。

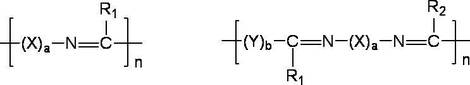

【解決手段】式(1)

(式中、環構造A及びBは、同一又は相異なり、置換されていてもよいアリール基、又は置換されていてもよいヘテロアリール基を表し、それぞれ単環もしくは複数環が縮環していてもよい;X及びYは、同一又は相異なり、硫黄、酸素、セレン、テルル原子、SO2、(R1)−C−(R2)、(R3)−Si−(R4)、又はN−(R5)で表される基を表し、Zは、N−(R6)で表される基を表す。但し、下記の式(2)

で表される化合物は除く。)で表されるラダー型化合物。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】良好なトランジスタ特性を示し、酸素分圧等の周囲の雰囲気の影響を防止でき、安定した半導体特性を示す電界効果型トランジスタを提供する。

【解決手段】ソース電極及びドレイン電極と、ソース電極及びドレイン電極に接しており、層厚方向で比抵抗が異なり、結晶酸化物を含む酸化物半導体膜と、ゲート電極と、ゲート電極と酸化物半導体膜の間にゲート絶縁膜を有し、酸化物半導体膜のゲート絶縁膜側の比抵抗が、ソース電極及びドレイン電極側の比抵抗に比べて低い薄膜トランジスタ。

(もっと読む)

有機半導体デバイス及びその製造方法並びに有機ELディスプレイ

【課題】スイッチングトランジスタと駆動用トランジスタとの電気的接続を確実にするとともに、ビアホール形成とバンク(又はセパレータ)形成とによるゲート絶縁膜の劣化を防ぐ。

【解決手段】トップゲート型のスイッチングトランジスタ11とボトムゲート型の駆動用トランジスタ12とを備える有機半導体デバイス10であって、スイッチングトランジスタ11のソース電極103と、駆動用トランジスタ12のゲート電極202とは同一の構造物を兼用し、スイッチングトランジスタ11のバンク層105と駆動用トランジスタ12のゲート絶縁膜203とは、同一の構造物を兼用し、駆動用トランジスタ12のバンク層205とスイッチングトランジスタ11のゲート絶縁膜107とは、同一の構造物を兼用する。

(もっと読む)

発光デバイス及び物品

【課題】所望の色出力を得る有機電子デバイスを提供。

【解決手段】1以上の光透過性素子8、12、光透過性素子に固定された複数の光透過性有機電子デバイス6、14、及び光透過性素子に固定された1以上の光透過性制御器4を含むデバイス2。光透過性制御器は2以上の光透過性有機電子デバイスに接続されている。物品は2つ以上の前記デバイスを含んでいる。

(もっと読む)

有機薄膜トランジスタ、有機薄膜トランジスタの製造方法、および電子機器

【課題】有機材料からなる下地の絶縁性層に対してダメージを与えることなく、かつ上部に設けられる有機半導体層に対して良好なオーミックコンタクトが得られるソース電極およびドレイン電極を低コストで得ることを可能にする。

【解決手段】有機絶縁層からなる基板11と、基板11上にめっき成膜された層からなるソース電極13sおよびドレイン電極13dの第1層13-1と、第1層13-1よりも有機半導体材料に対して低オーミック接合を形成する金属材料からなり第1層13-1を覆う状態でめっき成膜されたソース電極13sおよびドレイン電極13dの第2層13-2と、第1層13-1および第2層13-2で構成されたソース電極13sおよびドレイン電極13d間にわたって設けられた有機半導体層15とを備えた有機薄膜トランジスタ1aである。

(もっと読む)

縦型電界効果トランジスタ及び画像表示装置

【課題】 基体上で素子が占める素子面積を小型化することができ、かつ、オフ電流の小さい縦型電界効果トランジスタ、及びそれを用いた画像表示装置を提供すること。

【解決手段】 絶縁性基板1の上に、ドレイン電極7に比べてわずかに厚いソース電極3と、ドレイン電極7に比べてわずかに薄い絶縁層5と、ドレイン電極7とを積層する。この積層体の一方の側方に、間隙部を挟んで、ドレイン電極7と同じ厚さの下部絶縁層2と、ソース電極3と同じ厚さのゲート電極4と、絶縁層5と同じ厚さの上部絶縁層6とを積層する。間隙部には、積層体の側面に接する半導体層8と、ゲート絶縁膜6gとを配置して、縦型電界効果トランジスタを形成する。半導体層8の材料として、成膜方向にc軸が配向し、c軸方向に優れた移動度を示す酸化亜鉛を用いる。電極材料に不純物をドープした酸化亜鉛を用いれば、可視光に対して透明なトランジスタを形成することができる。

(もっと読む)

薄膜電界効果型トランジスタの製造方法及び該製造方法によって製造された薄膜電界効果型トランジスタ

【課題】本発明の目的は、高ON/OFF比を有し、且つ動作安定性に優れた酸化物半導体を用いた薄膜電界効果型トランジスタの製造方法を提供することにある

【解決手段】ゲート電極2を形成する工程、ゲート絶縁膜3を形成する工程、酸化物半導体よりなる活性層を形成する工程、該活性層に接して該活性層より電気伝導度の低い酸化物半導体よりなる抵抗層6を形成する工程、該抵抗層の一部を低抵抗化処理することにより所定の間隔を離して少なくとも2つの低抵抗領域を形成する低抵抗化処理工程であって、該2つの低抵抗領域に挟まれた低抵抗化処理が施されなかった領域(未低抵抗化領域)が、平面上、前記ゲート電極の内側に形成され、及び前記2つの低抵抗領域のそれぞれと接してソース電極及びドレイン電極を形成する工程を有する薄膜電界効果型トランジスタの製造方法。

(もっと読む)

薄膜トランジスタ基板とその製造方法

【課題】工程効率が向上し、かつ、信頼性が向上した酸化物半導体薄膜トランジスタ基板とその製造方法を提供する。

【解決手段】酸化物半導体薄膜トランジスタは、絶縁基板上に形成され、ゲート電極を含むゲート線と、ゲート線と交差しドレイン電極接続部を含むデータ線と、ゲート電極の周辺に形成される酸化物半導体活性層パターンと、データ線と酸化物半導体活性層パターンの上に形成されドレイン電極接続部を露出する第1開口部、及び酸化物半導体活性層パターンを露出する第2開口部を有するパシベーション層と、第1開口部及び第2開口部によって酸化物半導体活性層パターンとドレイン電極接続部とを電気的に接続するドレイン電極とを含む。

(もっと読む)

パターニング方法、有機電気素子、有機電界発光素子、及び有機半導体トランジスタ

【課題】パターン形成対象層へのパターン形成において、形成された凹部または孔部内にパターン形成工程における残渣が残ることが抑制されるパターニング方法を提供する。

【解決手段】有機半導体トランジスタ素子40においては、製造工程において、図8に示すように、ソース電極44及びドレイン電極45の形成された基板42上に、隔壁49を構成する上記絶縁性材料を一様に塗布して絶縁層47を形成し、この絶縁層47に、形成対象のパターンに応じた凸部60Aを有すると共に該凸部60Aに絶縁層を溶解する溶解液62の塗布された鋳型60を接触させることで、絶縁層47を溶解して該凸部60Aに応じた孔部49Aを形成した後に該鋳型60を基板42から剥離することで孔部49Aをパターニングする。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】オン電流とオフ電流の適正化を図った薄膜トランジスタを備えた表示装置及びその製造方法を提案することを目的とする。

【解決手段】ゲート電極GTと、チャネル領域と、チャネル領域を挟む領域に形成される2つの不純物領域とを含んで、ソース電極ST及びドレイン電極DT間の電流を制御する半導体膜Sと、ソース電極ST等と2つの不純物領域との間に介在する2つのオーミックコンタクト層DSと、半導体膜Sの略中心となる位置を中心とする一部の領域に積層される絶縁膜ESと、を含み、半導体膜Sは、微結晶シリコン又は多結晶シリコンを含んで形成され、2つの不純物領域は、絶縁膜ESが形成されない領域に形成され、2つのオーミックコンタクト層DSは、2つの不純物領域を覆うように形成され、ソース電極ST等は、オーミックコンタクト層DSを覆うように形成される、ことを特徴とする表示装置。

(もっと読む)

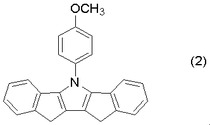

ゲート絶縁層用樹脂組成物

【課題】ゲート絶縁層を形成する材料を改良することにより有機電界効果トランジスタのヒステリシスを小さくする有機薄膜トランジスタゲート絶縁層用樹脂組成物を提供する。

【解決手段】(A)下記一般式(1)で表される基を含有する高分子化合物と、(B)架橋剤とを含有することを特徴とする有機薄膜トランジスタゲート絶縁層用樹脂組成物。 (もっと読む)

(もっと読む)

液晶表示装置

【課題】poly−Si層およびa−Si層が積層されたボトムゲートのTFTにおいて、リーク電流の増大を防止する。

【解決手段】最下層には、ゲート電極103が縦方向に細長く形成されている。このゲート電極103の上に、図示しないゲート絶縁膜104を挟んでpoly−Si層107およびa−Si層108からなる半導体層が形成されている。半導体層の上に、ソース電極110あるいはドレイン電極111が形成されている。ソース電極110あるいはドレイン電極111と半導体層の間にはn+Si層が形成されている。ソース電極110あるいはドレイン電極111の端部EDは、半導体層の端部ESよりも内側に形成されているので、半導体層の端部ESにおけるリーク電流を無くすことが出来る。

(もっと読む)

2,001 - 2,020 / 3,898

[ Back to top ]