Fターム[5F110HK18]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 複数種の構成材料の分布 (136)

Fターム[5F110HK18]に分類される特許

1 - 20 / 136

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備えた表示装置、スパッタリングターゲット材

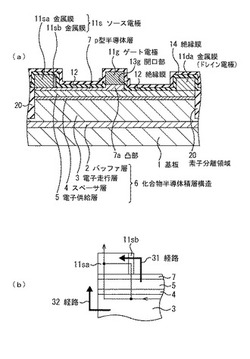

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11daと、電子供給層5とゲート電極11gとの間に形成された第1のp型半導体層7aと、ソース電極11sと電子供給層5との間に形成されたp型半導体層7と、が設けられている。第2のp型半導体層7上のソース電極11sには、第1の金属膜11saと、第1の金属膜11saにゲート電極11g側で接し、第1の金属膜11saよりも抵抗が大きい第2の金属膜11sbと、が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

配線膜およびそれを用いたアクティブマトリクス基板、並びに配線膜の製造方法

【課題】テーパー形状のAl配線膜を容易かつ安定的に得る。

【解決手段】Al配線膜101は、AlもしくはAl合金から成る第1のAl合金層101aと、その上に配設され、Ni、PdおよびPtのいずれか1以上の元素を含み第1のAl合金層101aとは異なる組成のAl合金から成る第2のAl合金層101bとから成る二層構造を有する。フォトレジスト102の現像処理に用いるアルカリ性薬液により、第2のAl合金層101bはエッチングされ、その端部はフォトレジスト102の端部よりも後退する。その後、フォトレジスト102をマスクとするウェットエッチングを行うことにより、Al配線膜101の断面はテーパー形状となる。

(もっと読む)

半導体装置およびその作製方法

【課題】ソース電極およびドレイン電極間におけるオフリーク電流の低減を課題とする。

【解決手段】本発明の一態様は、ゲート電極101と、前記ゲート電極を覆うように形成されたゲート絶縁膜102,103と、前記ゲート絶縁膜上に形成され、前記ゲート電極の上方に位置する活性層104と、前記活性層の側面及び前記ゲート絶縁膜の上に形成されたシリコン層105,106と、前記シリコン層上に形成されたソース電極107aおよびドレイン電極107bと、を具備し、前記活性層は、前記ソース電極および前記ドレイン電極それぞれと接しないことを特徴とする半導体装置である。

(もっと読む)

薄膜トランジスタ基板およびその製造方法

【課題】高い表示品位を有する表示装置用の薄膜トランジスタ基板およびこれらを生産効率よく実現することができる製造方法を提供する。

【解決手段】基板1上の複数の部分に配設された半導体膜2と、半導体膜2上に、該半導体膜2と接し互いに離間して配設されたソース電極およびドレイン電極4と、半導体膜2、ソース電極3およびドレイン電極4を覆うゲート絶縁膜6と、ゲート絶縁膜6を介して、ソース電極3およびドレイン電極4の間に跨るように配設された、ゲート電極7とを有した薄膜トランジスタ201と、半導体膜2上に、該半導体膜と接して配設された補助容量電極10と、下層に半導体膜2を有してソース電極から延在するソース配線31と、ゲート電極7から延在するゲート配線71と、ドレイン電極4に電気的に接続された画素電極9と、隣り合う画素の補助容量電極10どうしを電気的に接続する、補助容量電極接続配線12とを備えている。

(もっと読む)

Cu合金膜、及びそれを備えた表示装置または電子装置

【課題】基板及び/又は絶縁膜との高い密着性を有し、且つ、液晶表示装置などの製造過程で施される熱処理の後も低い電気抵抗率を有する新規なCu合金膜を提供すること。

【解決手段】表示装置用Cu合金膜であって、前記Cu合金膜は、Cu−Mn−B合金で構成されており、前記Cu合金膜の基板側の界面(I)から、前記Cu合金膜の最表面に向って50nm(II)までの深さ方向のMn量およびB量をそれぞれ、Mn量(MnI−II)およびB量(BI−II)とすると共に、前記Cu合金膜の深さ50nm(II)から、前記Cu合金膜最表面(III)までの深さ方向のMn量およびB量をそれぞれ、Mn量(MnII−III)およびB量(BII−III)とし、前記Mn量のMnI−IIとMnII−IIIとの関係が、2.0≦(MnI−II/MnII−III)であると共に、前記B量のBI−IIとBII−IIIとの関係が、1.5≦(BI−II/BII−III)であること。

(もっと読む)

酸化物半導体用電極、その形成方法、及びその電極を備えた酸化物半導体装置

【課題】薄膜トランジスタなどの素子動作層をなす導電性インジウム含有酸化物半導体層に電気的接触抵抗が小さい金属電極を形成できるようにする。

【解決手段】インジウム含有酸化物半導体層とその層の上方に設けた素子動作電流を流通させる金属電極層との間に、酸化物半導体層をなすインジウム酸化物などを化学的に還元でき、且つ易酸化性の金属からなる金属膜を素材とした金属酸化物層と金属層とを設け、更に、金属酸化物層と金属層との境界には還元されたインジウムを蓄積したインジウム濃化層を設ける構成とする。

(もっと読む)

表示装置および半導体装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Geを0.01〜2.0原子%と、Ta、Ti、Zr、Hf、W、Cr、Nb、Mo、Ir、Pt、Re、およびOsよりなる群(X群)から選択される少なくとも一種の元素とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置もしくは半導体装置用Al合金膜である。

(1)Alと、前記X群から選択される少なくとも一種の元素と、Geとを含む第1の析出物について、円相当直径50nm以上の析出物が200,000個/mm2以上の密度で存在する。

(もっと読む)

パルス列アニーリング方法および装置

【課題】基板の所望の領域上でアニーリングプロセスを実行するために使用される装置および方法を開示する。

【解決手段】1つの実施形態では、電磁エネルギのパルスはフラッシュランプまたはレーザ装置を使用して基板に送出される。パルスは約1nsecから約10msecの長さであってもよく、各パルスは基板材料を融解するのに必要なエネルギより少ないエネルギを有する。パルスの間隔は一般的に、各パルスにより与えられるエネルギを完全に放散させるのに十分な長である。このようにして、各パルスはマイクロアニーリング周期を終了する。パルスは1回で基板全体にまたは同時に基板の一部に送出されてもよい。

(もっと読む)

スパッタリングターゲット、半導体装置および半導体装置の製造方法

【課題】Cu配線層に含まれるCuの周囲への拡散を抑制すると共に密着性および動作特性に優れた半導体装置およびその製造方法、並びに、その半導体装置の製造に用いるスパッタリングターゲットを提供する。

【解決手段】実施の形態に係るスパッタリングターゲットは、1.5原子%以上5.0原子%以下のMnと、(Mgの原子%)/(Mnの原子%)で示される比率が0.3以上2.1以下となるMgと、10wtppm以下のCと、2wtppm以下のO2と、を含むCu合金を用いて形成される。

(もっと読む)

アクティブマトリックス基板、及び液晶装置

【課題】TFTの光リーク電流が低減され、かつ、従来よりも少ないフォトリソフォグラフィ工程で製造することが可能なアクティブマトリックス基板を提供する。

【解決手段】アクティブマトリックス基板201は、絶縁性基板1上に、基板1側から、ゲート電極2と、ゲート電極2を覆うゲート絶縁膜6と、互いに離間形成されたドレイン電極9及びソース電極11と、チャネル層を含む少なくとも1層の半導体膜21とが順次形成された薄膜トランジスタ101と、画素電極10とが複数対アレイ状に形成されたものである。ドレイン電極9及びソース電極11は、基板1側から透光性導電膜EM2と非透光性導電膜EM3とが順次積層された積層構造を有し、かつ、ドレイン電極9の透光性導電膜EM2及び/又は非透光性導電膜EM3が延設され、この延設部分により画素電極10が形成されたものである。

(もっと読む)

配線構造

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、エッチストッパー層を設けなくてもウェットエッチング時の加工性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、薄膜トランジスタの半導体層と、金属配線膜とを有しており、前記半導体層と前記金属配線膜との間にバリア層を有する配線構造であって、半導体層は酸化物半導体からなり、バリア層は、高融点金属系薄膜とSi薄膜の積層構造を有し、Si薄膜は半導体層と直接接続している。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】バックチャネル部の表面のアルミニウム汚染に起因する漏れ電流を抑制を防止でき、高い信頼性と、高い歩留を実現できる構造の薄膜トランジスタを提供することを目的とする。

【解決手段】この発明に係る薄膜トランジスタは、シリコンを半導体層とするバックチャネル部を有するボトムゲート構造の薄膜トランジスタであって、アルミニウムを含むソース電極またはドレイン電極と、バックチャネル部の一部であって半導体層の表層を覆うサイアロン化合物の層とを有するものである。

(もっと読む)

電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造

【課題】酸化物反応層の寄生抵抗の低減を図り、動作特性の向上を図った電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造を提供する。

【解決手段】TFT素子1は、a−Si膜5上に形成されたPドープn+a−Si膜6と、Pドープn+a−Si膜6上に形成された1nm以下のSi酸化膜7を有している。電極配線膜となるCu合金膜8が、Si酸化膜7上にスパッタリングにより形成されている。Cu合金膜8は、0.3〜2.0原子%のSn、In、Gaの金属のうち1種以上を含有する。

(もっと読む)

シリコンデバイス構造、及びその形成に用いるスパッタリングターゲット材

【課題】シリコンデバイスの飽和移動度特性を向上する。

【解決手段】シリコン半導体膜上に、Pドープn+型アモルファスシリコン膜と、該Pドープn+型アモルファスシリコン膜上に形成された配線とを有するシリコンデバイス構造において、前記配線が、前記Pドープn+型アモルファスシリコン膜の表面に形成されたシリコン酸化膜と、銅合金膜とからなり、前記銅合金膜は、1原子%以上5原子%以下のMn及び0.05原子%以上1.0原子%以下のPを含む銅合金をスパッタリングにより形成した膜である。

(もっと読む)

半導体装置、光学装置及びセンサ装置

【課題】ソース電極及びドレイン電極と有機半導体材料層との間の接触抵抗を低下させることができ、これを簡便な製造プロセスで実現できる半導体装置、光学装置及びセンサ装置を提供すること。

【解決手段】ソース電極5と、ドレイン電極6と、少なくともこれらの電極間に設けられた有機半導体材料層7とを有し、有機半導体材料層7を介してソース電極5とドレイン電極6との間で電荷を移動させるように構成された有機電界効果トランジスタにおいて、ソース電極5及びドレイン電極6が、導電性高分子材料と電荷移動錯体との混合物からなる、有機電界効果トランジスタ1a。

(もっと読む)

表示装置用Al合金膜

【課題】シリコン半導体層および/または透明導電膜との間のバリアメタル層を省略しても、AlとSiの相互拡散を抑制でき、低抵抗のオーミック特性を有する電気的接触が得られると共に、十分な耐熱性を有する表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜および/または薄膜トランジスタの半導体層と直接接続されるAl合金膜であって、Al合金膜は、30原子%以上のMoを含有するAl−Mo合金、またはMoと、Mn、Nd、Ni、Mg、およびFeよりなるX群から選択される少なくとも1種とを含有するAl−Mo−X合金の単層から構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造の縦型のMISFETの提供

【解決手段】Si基板1上に、一部に空孔4を有する絶縁膜2が設けられ、空孔4上及び絶縁膜2の一部上に横方向半導体層6が設けられ、半導体層6の側面の一部に導電膜3が接して設けられ、絶縁膜2により素子分離されている。半導体層6上の、空孔4直上部に縦方向半導体層7が設けられ、半導体層7の上部にドレイン領域(10,9)が設けられ、離間し、相対して下部にソース領域8が設けられ、ソース領域8は延在して、半導体層6全体に設けられている。半導体層7の全側面には、ゲート酸化膜11を介してゲート電極12が設けられ、ドレイン領域10、ゲート電極11及び導電膜3を介したソース領域8には、バリアメタル18を有する導電プラグ19を介してバリアメタル21を有する配線22が接続されている縦型のMISFET。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

1 - 20 / 136

[ Back to top ]