Fターム[5F110HK28]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層に含まれる不純物 (1,114) | 不純物の分布 (33)

Fターム[5F110HK28]に分類される特許

1 - 20 / 33

半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減させ、オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。

【解決手段】絶縁表面上の一対の電極と、一対の電極と接して設けられる酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳するゲート電極と、を有し、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含む半導体装置とする。さらに、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含ませる方法として、フッ素を含む雰囲気におけるプラズマ処理を用いることができる。

(もっと読む)

薄膜形成基板、薄膜形成方法、及び表示装置の製造方法

【課題】基板に生じるクラックの発生を防止した薄膜形成方法を提供する。

【解決手段】薄膜形成方法は、基板を準備する基板準備工程と、基板上に第1薄膜を形成する第1薄膜形成工程と、第1薄膜に対して光線を相対走査して照射することにより、第1薄膜を結晶化する結晶化工程と、結晶化工程において第1薄膜に生じる熱の基板への伝導量を低下させる緩和層を、結晶化工程の前に、基板の端部領域及び基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に形成する緩和層形成工程とを含む。

(もっと読む)

半導体装置およびその作製方法

【課題】ソース電極およびドレイン電極間におけるオフリーク電流の低減を課題とする。

【解決手段】本発明の一態様は、ゲート電極101と、前記ゲート電極を覆うように形成されたゲート絶縁膜102,103と、前記ゲート絶縁膜上に形成され、前記ゲート電極の上方に位置する活性層104と、前記活性層の側面及び前記ゲート絶縁膜の上に形成されたシリコン層105,106と、前記シリコン層上に形成されたソース電極107aおよびドレイン電極107bと、を具備し、前記活性層は、前記ソース電極および前記ドレイン電極それぞれと接しないことを特徴とする半導体装置である。

(もっと読む)

表示装置

【課題】光電変換素子を含む表示装置において、生産性および利便性に優れた表示装置を提供する。

【解決手段】複数の画素がマトリクス状に配列された表示部と、表示部に画像情報を伝送する駆動部と表示部に設けられ、且つレーザ光を検出する受光部と、受光部で検出するレーザ光の位置を解析し、位置に基づいて画像情報を操作し、操作に基づいた画像情報とは異なる画像情報を駆動部に伝送する情報処理部を有し、表示部の複数の画素はそれぞれ薄膜トランジスタを有し、受光部は複数の光電変換素子、走査回路、リセット回路および読み出し回路を有し、薄膜トランジスタおよび複数の光電変換素子は、同一の基板に設けられている表示装置である。

(もっと読む)

成膜方法及び薄膜トランジスタの作製方法

【課題】3層以上の膜を成膜するに際して、第1の膜の成分が第3の膜に含まれることを防ぐ成膜方法を提供する。

【解決手段】上部電極104と下部電極102が設けられた成膜装置100により3層以上の膜を成膜する多層膜の成膜に際して、下部電極102上に基板110を配して第1の膜112を成膜し、前記第1の膜112の形成時よりも上部電極104と前記基板110の間の距離を長くし、前記第1の膜112上に第2の膜114を成膜し、前記第2の膜114の形成時よりも前記上部電極104と前記基板110の間の前記距離を短くし、前記第2の膜114上に第3の膜116を成膜する。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】酸化物半導体膜を有するボトムゲート構造のトランジスタの作製工程において、熱処理による脱水化または脱水素化処理、及び酸素ドープ処理を行う。熱処理による脱水化または脱水素化処理及び酸素ドープ処理された酸化物半導体膜を有するトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジスタのしきい値電圧の変化量が低減できており、信頼性の高いトランジスタとすることができる。

(もっと読む)

表示装置およびその製造方法

【課題】 ボトムゲート構造のTFTを有する表示装置の生産性の低下を抑えるとともに、表示特性の劣化を抑える。

【解決手段】 複数の薄膜トランジスタが形成された基板を有する表示パネルを備え、前記薄膜トランジスタは、前記基板の上にゲート電極、ゲート絶縁膜、半導体膜の順に積層され、かつ、前記半導体膜の上にはソース電極の一部または全部およびドレイン電極の一部または全部がコンタクト膜を介して積層されており、前記コンタクト膜は、前記半導体膜と前記ソース電極との間に介在する部分および前記半導体膜と前記ドレイン電極との間に介在する部分を除いた部分が酸化されている表示装置であって、それぞれの前記コンタクト膜は、前記半導体膜と接している面の反対側が凹凸を有する曲面であり、かつ、最小膜厚が3nm以下、最大膜厚が4nm以上である表示装置。

(もっと読む)

表示装置および表示装置の製造方法

【課題】Cu合金をソース・ドレイン電極に用いたTFTにおいて、コンタクト膜に対して酸化処理を施す場合であっても、良好なオン特性を維持する表示装置を提供することを目的とする。

【解決手段】半導体層4と、銅と1種類の添加元素とを含む銅合金層を有するソース電極10およびドレイン電極9と、ソース電極10及びドレイン電極9のそれぞれの電極と半導体層4との間に形成されるコンタクト膜5と、それぞれの電極とコンタクト膜5との間に形成される酸化物膜8と、を含む薄膜トランジスタ基板を有する表示装置であって、コンタクト膜5は、不純物とシリコンとを含み、酸化物膜8は、シリコン、不純物および酸素を含むとともに、酸化物膜8における不純物濃度がコンタクト膜5における不純物濃度よりも低い、ことを特徴とする表示装置。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、表示装置、および電子機器

【課題】有機半導体層とソース電極/ドレイン電極との間のコンタクト抵抗を図りながらも微細化プロセスの適用が可能でかつ良好な特性を有する薄膜トランジスタを提供する。

【解決手段】トップコンタクト・ボトムゲート構造の薄膜トランジスタにおいて、有機半導体層17とソース電極21s/ドレイン電極21dとの間に、有機半導体材料と共にアクセプタ性材料またはドナー性材料を含有するコンタクト層19を設けた。有機半導体層17の導電型がp型である場合には、コンタクト層19にはアクセプタ性材料が含有されている。コンタクト層19は、有機半導体層17と同一のパターン形状を有している。

(もっと読む)

埋め込みストレッサを有する高性能FETを形成するための方法および構造

【課題】 高性能の半導体構造およびかかる構造を製造する方法を提供する。

【解決手段】 半導体構造は、半導体基板12の上面14上に位置する、例えばFETのような少なくとも1つのゲート・スタック18を含む。構造は更に、少なくとも1つのゲート・スタックのチャネル40上にひずみを誘発する第1のエピタキシ半導体材料34を含む。第1のエピタキシ半導体材料は、少なくとも1つのゲート・スタックの対向側に存在する基板内の1対のくぼみ領域28の実質的に内部で少なくとも1つのゲート・スタックの設置場所に位置する。くぼみ領域の各々において第1のエピタキシ半導体材料の上面内に拡散拡張領域38が位置する。構造は更に、拡散拡張領域の上面上に位置する第2のエピタキシ半導体材料36を含む。第2のエピタキシ半導体材料は、第1のエピタキシ半導体材料よりも高いドーパント濃度を有する。

(もっと読む)

表示装置

【課題】 移動度特性及び生産性を向上した薄膜トランジスタを提供する。さらに、それを用いた高性能の表示装置を提供する。

【解決手段】 基板上に、ゲート電極と、ゲート絶縁膜と、半導体膜と、コンタクト膜と、ソース電極及びドレイン電極として機能する一対の電極とを具備し、前記半導体膜と前記ソース電極あるいはドレイン電極の間に前記コンタクト膜がある薄膜トランジスタを有する表示装置であって、前記コンタクト膜はSiを主成分とした膜であり、前記コンタクト膜中のIII族あるいはV族の不純物濃度のピークが前記コンタクト膜と前記ソース電極及び前記ドレイン電極との界面から3nm以上離れている、あるいは不純物濃度が前記半導体膜側で高くなっている。

(もっと読む)

シリコン薄膜の成膜方法および半導体装置の製造方法

【課題】塗布法を適用したより簡便な方法で導電性の高いコンタクト層とイントリンシックなシリコン層とを積層させた構成のシリコン薄膜を得る方法を提供する。

【解決手段】鎖状の高次シラン化合物Bと、金属Mを含有する化合物と、高次シラン化合物Bよりも沸点が低く金属Mと相互作用する化合物からなる溶媒Cとを混合した塗布液を調整する。塗布液を用いて基板1上に塗布膜3を形成する。塗布膜3中から溶媒Cを除去して乾燥させる。この際塗布膜3を加熱する。これにより、表面側において金属Mの含有量が多いシリコン薄膜5を形成する。

(もっと読む)

薄膜半導体デバイス及びその製造方法

【課題】活性層と半導体層との接触面をホモ接合、あるいはホモ接合に限りなく近づけて、界面のバンド障壁を防止して大きなオン/オフ比を得ることができ、かつ製造コスト及び作業工数を低減できる。

【解決手段】薄膜半導体デバイスが、基板1と、基板1上に積層されたソース及びドレイン電極層3と、ソース及びドレイン電極層3上に積層された結晶性シリコンからなる不純物含有半導体層4と、不純物含有半導体層4上に積層された結晶性シリコンからなる活性層5と、活性層5上に積層されたゲート絶縁膜6と、ゲート絶縁膜6の上に積層されたゲート電極7と、を備え、不純物含有半導体層4と活性層5の接合面において、これらの結晶性を連続にする。

(もっと読む)

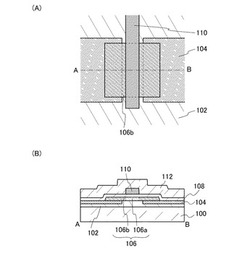

薄膜トランジスタ及び表示装置の作製方法

【課題】マスク数の少ない薄膜トランジスタの作製方法を提供する。

【解決手段】第1の導電膜102と、絶縁膜104と、半導体膜106と、不純物半導体膜108と、第2の導電膜110とを積層し、この上に多階調マスクを用いて凹部を有するレジストマスク112を形成し、第1のエッチングを行って薄膜積層体を形成し、第1の導電膜102がエッチングされた膜113に対してサイドエッチングを伴う第2のエッチングを行ってゲート電極層116Aを形成し、その後ソース電極及びドレイン電極等を形成することで、薄膜トランジスタを作製する。半導体膜としては結晶性半導体膜106を用いる。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】微結晶シリコンをチャンネル領域として用い、良好にリーク電流を抑制することが可能な薄膜トランジスタ及びその製造方法を提供する。

【解決手段】薄膜トランジスタ100は、基板11と、ゲート電極112と、ゲート絶縁膜113と、微結晶シリコンから形成された半導体層(チャンネル領域)114と、第1のオーミックコンタクト層116,117と、第2のオーミックコンタクト層118,119と、ドレイン電極120と、ソース電極121と、を備える。半導体層114と、ドレイン電極120及びソース電極121との間に、第2のオーミックコンタクト層118,119の不純物濃度より低い第1のオーミックコンタクト層116,117を形成することにより、第1のオーミックコンタクト層116,117内に空乏層が良好に広がり、薄膜トランジスタ100のリーク電流を良好に抑制することができる。

(もっと読む)

薄膜トランジスタ、その製造方法、表示装置、及び半導体装置

【課題】良好なトランジスタ特性を有する薄膜トランジスタ、その製造方法、表示装置、及び半導体装置を提供すること

【解決手段】本発明にかかる薄膜トランジスタは、基板上に形成されたゲート電極2と、ゲート電極を覆うゲート絶縁膜3と、ゲート絶縁膜3上に形成され、ゲート電極2の対面に配置された半導体層4と、半導体層4上に、n型不純物を含むn型オーミックコンタクト層6を介して形成された、ソース電極7及びドレイン電極8と、ソース電極7の下のn型オーミックコンタクト層6と半導体層4との間、ドレイン電極8の下のn型オーミックコンタクト層6と半導体層4との間にそれぞれ形成されたp型半導体層5と、を備えるものである。

(もっと読む)

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタアレイ基板、及び表示装置

【課題】優れたオン電流特性と、優れたオフ電流特性を兼ね備え、かつ歩留まりの向上が可能な薄膜トランジスタを提供する。

【解決手段】本発明に係る薄膜トランジスタは、下層半導体層11と、上層半導体層12の間には、ソース領域10S/ドレイン領域10Dに開口部を有する絶縁膜4が形成され、開口部H1,H2を介して、下層半導体層11と上層半導体層12が接続される。下層半導体層11のうち、少なくともソース領域10S/ドレイン領域10Dの間に配置されるチャネル領域10C、及び開口部H1,H2と対向する領域のうちの前記チャネル領域から延設される少なくとも一部の領域は、多結晶半導体層であり、上層半導体層は、非晶質半導体層である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体層とソース電極層及びドレイン電極層との間にバッファ層が設けられた順スタガ型(トップゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン電極層と半導体層との間に、半導体層よりもキャリア濃度の高いバッファ層を意図的に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられた逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体層のチャネル形成領域と重なる領域にチャネル保護層を設け、半導体層とソース電極層及びドレイン電極層との間にバッファ層が設けられた逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極及びドレイン電極と半導体層との間に、半導体層よりもキャリア濃度の高いバッファ層を意図的に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

1 - 20 / 33

[ Back to top ]