Fターム[5F110HK32]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層の製法 (10,751) | 堆積 (8,750)

Fターム[5F110HK32]の下位に属するFターム

Fターム[5F110HK32]に分類される特許

161 - 180 / 3,497

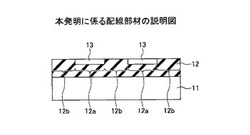

配線部材、および、電子素子の製造方法と、それを用いた配線部材、積層配線、電子素子、電子素子アレイ及び表示装置。

【課題】印刷法による少ない工程数のメリットを生かしつつ、より微細であり、絶縁性の低下がなく、導電部寸法精度の高い、配線部材および電子素子の製造方法を提供することを目的とする。また、配線部材、積層配線、電子素子、電子素子アレイ及び表示装置を提供することを目的とする

【解決手段】基板上にエネルギーの付与により臨界表面張力が変化する材料を含有する濡れ性変化層を形成する工程、紫外領域のレーザーを用いたレーザーアブレーション法により、濡れ性変化層に凹部を形成する工程、凹部に導電性インクを塗布して導電部を形成する工程、を含み、前記濡れ性変化層の凹部のパターン形成と同時に、前記臨界表面張力を変化させて高表面エネルギー領域のパターン形成が行われることを特徴とする配線部材の製造方法、電子素子の製造方法、及び、それにより得られた配線部材、電子素子を提供する。また、電子素子アレイ及び表示装置を提供する。

(もっと読む)

半導体装置

【課題】半導体膜と電極又は配線との接触抵抗を低減し、かつ半導体膜と電極又は配線と

の被覆率を改善し、特性を向上させた半導体装置を得ることを課題とする。

【解決手段】基板上にゲート電極と、前記ゲート電極上にゲート絶縁膜と、前記ゲート絶

縁膜上に第1のソース電極又はドレイン電極と、前記第1のソース電極又はドレイン電極

上に島状半導体膜と、前記島状半導体膜及び前記第1のソース電極又はドレイン電極上に

第2のソース電極又はドレイン電極とを有し、前記第2のソース電極又はドレイン電極は

前記第1のソース電極又はドレイン電極と接触しており、前記第1のソース電極又はドレ

イン電極及び第2のソース電極又はドレイン電極が前記島状半導体膜を挟みこんでいる半

導体装置及びその作製方法に関するものである。

(もっと読む)

電子デバイス及び半導体装置の製造方法

【課題】簡素な装置で、短時間にて形成することができ、しかも、電極と能動層との間のコンタクト抵抗の低減を確実に図ることができる電荷注入層を備えた電子デバイスを提供する。

【解決手段】電子デバイスは、第1電極15、第1電極と離間して設けられた第2電極15、及び、第1電極15の上から第2電極15の上に亙り設けられた、有機半導体材料から成る能動層14を少なくとも備えており、第1電極15と能動層14との間、及び、第2電極15と能動層14との間には、電荷注入層16が形成されており、電荷注入層16は、酸化されることで電気伝導度の値が増加した有機材料から成る。

(もっと読む)

半導体記憶装置

【課題】コストを増大させずとも、書き込みに高電圧を必要とせず、不良が発生しにくく

、書き込み時間が短く、データの書換えができない半導体記憶装置を提供する。

【解決手段】ダイオード接続した第1のトランジスタと、ダイオード接続した第1のトラ

ンジスタのソース電極及びドレイン電極の一方の端子にゲートが接続する第2のトランジ

スタと、ダイオード接続した第1のトランジスタのソース電極及びドレイン電極の一方の

端子及び第2のトランジスタのゲートに接続する容量素子を有するメモリ素子を含む半導

体記憶装置である。

(もっと読む)

半導体装置及びその製造方法、並びに、画像表示装置の製造方法

【課題】本開示の目的は、ソース/ドレイン電極の段切れ、ソース/ドレイン電極の損傷といった問題の発生を確実に回避することができ、しかも、島状の平面形状を有するチャネル形成領域を確実に形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基材11上にゲート電極12を形成した後、(b)基材11及びゲート電極12上に、チャネル形成領域14を形成すべき領域に凹部20が設けられたゲート絶縁層13を形成し、その後、(c)塗布法に基づき凹部20内に有機半導体材料から成るチャネル形成領域14を形成した後、(d)ゲート絶縁層13の上からチャネル形成領域14の一部の上に亙りソース/ドレイン電極15を形成する各工程から成る。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気特性を持つ、酸化物半導体を用いた薄膜トランジスタを有する、信

頼性の高い半導体装置の作製方法の提供を目的の一とする。

【解決手段】絶縁表面上において、ゲート絶縁膜を間に挟んでゲート電極上に酸化物半導

体膜を形成し、酸化物半導体膜上に、チタン、モリブデンまたはタングステンを含む第1

の導電膜を形成し、第1の導電膜上に、電気陰性度が水素より低い金属を含む第2の導電

膜を形成し、第1の導電膜及び第2の導電膜をエッチングすることでソース電極及びドレ

イン電極を形成し、酸化物半導体膜、ソース電極及びドレイン電極上に、酸化物半導体膜

と接する絶縁膜を形成する半導体装置の作製方法。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】本発明は、低温かつ簡便で安価な製造工程により作製可能であり、トランジスタ特性に優れる、ダブルゲート構造を有する薄膜トランジスタおよびその製造方法を提供することを主目的とする。

【解決手段】本発明は、基板と、上記基板上に形成された第1ゲート電極と、上記第1ゲート電極を覆うように形成された第1ゲート絶縁層と、上記第1ゲート絶縁層上に形成され、低抵抗領域であるソースコンタクト領域およびドレインコンタクト領域ならびに高抵抗領域であるチャネル領域を有する酸化物半導体層と、上記ソースコンタクト領域に接して形成されたソース電極と、上記ドレインコンタクト領域に接して形成されたドレイン電極と、上記酸化物半導体層上に形成され、絶縁性有機材料を含む第2ゲート絶縁層と、上記第2ゲート絶縁層上に形成された第2ゲート電極とを有することを特徴とする薄膜トランジスタを提供する。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電圧の供給を停止しても論理回路の結線状態を保持可能なプログラマブルロジックデバイスにおける処理速度の向上及び低消費電力化を図ることを目的の一とする。

【解決手段】論理状態を切り替え可能な複数の演算回路と、演算回路の論理状態を切り替えるコンフィグレーション状態切り替え回路と、演算回路の電源電圧の供給または停止を切り替える電源制御回路と、複数の演算回路の論理状態及び電源電圧の状態を記憶する状態記憶回路と、状態記憶回路の記憶情報に応じて、コンフィグレーション状態切り替え回路及び電源制御回路の制御を行う演算状態制御回路と、を有し、演算回路とコンフィグレーション状態切り替え回路との間に、酸化物半導体層にチャネル形成領域が形成されるトランジスタが設け、電源制御回路からの電源電圧の停止時に該トランジスタの導通状態を保持する。

(もっと読む)

半導体装置

【課題】電力供給がない状況で記憶保持が可能で、書き込み回数に制限が無い、新たな半導体装置を提供する。

【解決手段】チャネル領域と第1のゲート絶縁層と第1のゲート電極と第1のソース及びドレイン電極とを有する第1のトランジスタと、酸化物半導体層140と第2のソース電極142a及び第2のドレイン電極142bと第2のゲート絶縁層146と第2のゲート電極148aとを有する第2のトランジスタ162と、第2のソース電極142aまたは第2のドレイン電極142bの一方と第2のゲート絶縁層146と第2のゲート絶縁層146上に第2のソース電極142a又は第2のドレイン電極142bの一方と重なるように設けられた第3の電極148bとを有する容量素子164と、を有し、第1のゲート電極と第2のソース電極142a又は第2のドレイン電極142bの一方とは接続され、第3の電極148bは酸化物半導体層140と重なる領域を有する。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用チャネル保護型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。半導体装置に設けられる該薄膜トランジスタは多階調マスクによって形成されたレジストマスクを用いて作製する。

(もっと読む)

有機電子デバイス用組成物、有機電子デバイスの作製方法、有機電子デバイス及び電界効果トランジスタ

【課題】電荷輸送性や移動度が高く、安定性に優れた有機半導体層、及びOn/Off比が高い有機電子デバイスを得る。また、この有機電子デバイスを低コストに製造する。

【解決手段】特定構造の有機半導体化合物と特定の有機化合物とを含有する有機電子デバイス用組成物を用いる。具体的には、有機半導体化合物として、アヌレン構造を有する有機化合物を用い、特定の有機化合物として、下記一般式(1)若しくは(2)で表わされる部分構造を有する有機化合物、又は、ウレア結合、チオウレア結合、ホスフィンオキシド結合、ホスフィンスルフィド結合、スルフォキシド結合若しくはスルホン結合を有する有機化合物を用いる。

(式(1)〜(2)中、Xは、酸素原子又は硫黄原子を示し、Zは硫黄原子又はリン原子を示す。nは、1又は2を示し、nが2である場合の2つのXは酸素原子を示す。X及びZがどちらも硫黄原子であることはない。)

(もっと読む)

半導体装置

【課題】所望のタイミングでデータの評価、書き換えを行うことができる半導体装置を提供する。

【解決手段】フリップフロップ回路と、選択回路と、選択回路を介して前記フリップフロップ回路と電気的に接続する不揮発性記憶回路と、を含むレジスタ回路と、ビット線と、データ線と、を有し、データ線はフリップフロップ回路と電気的に接続し、ビット線は、選択回路を介して不揮発性記憶回路と電気的に接続し、選択回路は、データ線の電位またはビット線の電位に応じたデータを選択的に不揮発性記憶回路に格納する半導体装置。

(もっと読む)

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のトランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電位を保持させることで行う。メモリセルの読み出しは、ビット線にプリチャージ電位を供給した後ビット線への電位の供給を止め、ビット線の電位がプリチャージ電位に保たれるか、または電位が下がるか、により行う。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

液晶表示装置

【課題】液晶表示装置の消費電力を低減すること及び表示の劣化を抑制すること。また、温度などの外部因子による表示の劣化を抑制すること。

【解決手段】各画素に設けられるトランジスタとして、チャネル形成領域が酸化物半導体層によって構成されるトランジスタを適用する。なお、酸化物半導体層を高純度化することで、トランジスタの室温におけるオフ電流値を10aA/μm以下且つ85℃におけるオフ電流値を100aA/μm以下とすることが可能である。そのため、液晶表示装置の消費電力を低減すること及び表示の劣化を抑制することが可能になる。また、上述したようにトランジスタは、85℃という高温においてもオフ電流値を100aA/μm以下とすることが可能である。そのため、温度などの外部因子による液晶表示装置の表示の劣化を抑制することができる。

(もっと読む)

半導体装置

【課題】高性能な半導体装置を提供する。

【解決手段】絶縁表面上に設けられるゲート電極層421と、ゲート電極層上に設けられるゲート絶縁層402と、ゲート絶縁層上に設けられる第1の酸化物半導体層442と、第1の酸化物半導体層上に接して設けられる第2の酸化物半導体層443と、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域と重なり、且つ第2の酸化物半導体層に接して設けられる酸化物絶縁層と、酸化物絶縁層上、第1の酸化物半導体層の第2の領域上、及び第2の酸化物半導体層の第2の領域と重なり、且つ第2の酸化物半導体層に接して設けられるソース電極層及びドレイン電極層と、を有し、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域は、ゲート電極層と重なる領域、並びに第1の酸化物半導体層及び第2の酸化物半導体層の周縁及び側面、に設けられる領域である。

(もっと読む)

光及び熱エネルギー架橋性有機薄膜トランジスタ絶縁層材料

【課題】閾値電圧の絶対値及びヒステリシスが小さい有機薄膜トランジスタを製造しうる有機薄膜トランジスタ絶縁層材料を提供すること。

【解決手段】(A)分子内にビニルオキシ基を含有する低分子化合物及び/又は分子内にビニルオキシ基及び活性水素と反応しうる第2の官能基を電磁波の照射もしくは熱の作用により生成しうる第1の官能基を含有する高分子化合物と、(B)分子内にN−マレオイルアミノ基を含含有する低分子化合物及び/又は分子内にN−マレオイルアミノ基及び活性水素と反応しうる第2の官能基を電磁波の照射もしくは熱の作用により生成しうる第1の官能基を含有する高分子化合物とを、含有し、前記2種類の高分子化合物のうちの少なくとも一方の高分子化合物を含有する有機薄膜トランジスタ絶縁層材料。

(もっと読む)

位相同期回路および位相同期回路を用いた半導体装置

【課題】スタンバイ状態からの復帰後、電圧制御発振器に入力される電圧信号が短時間で一定となる、消費電力の低減された位相同期回路を提供することを課題とする。

【解決手段】電圧制御発振器の入力端子とループフィルタを構成する容量素子の間に、酸化物半導体材料を用いて半導体層を形成したトランジスタを設け、通常動作状態の時には当該トランジスタをオン状態に、スタンバイ状態の時には当該トランジスタをオフ状態とする。

(もっと読む)

化合物半導体装置の製造方法

【課題】 短チャンネル効果が抑制され、メタルS/Dを有するInGaAs−MOSFETの低消費電力化をはかり得る化合物半導体装置を製造する。

【解決手段】 InGaAsをチャネルに用いた化合物半導体装置の製造方法であって、基板上のInGaAs層10上に、ゲート絶縁膜11を介してゲート電極12を形成した後、ゲート電極12の両側に露出するInGaAs層10上に、厚さ5.5nm以下のNi膜14を形成する。次いで、250℃以下の温度で熱処理を施すことにより、Ni膜14とInGaAs層10とを反応させて、ショットキー・ソース/ドレインとなるNi−InGaAs合金層15を形成する。

(もっと読む)

161 - 180 / 3,497

[ Back to top ]