Fターム[5F110HK32]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層の製法 (10,751) | 堆積 (8,750)

Fターム[5F110HK32]の下位に属するFターム

Fターム[5F110HK32]に分類される特許

3,481 - 3,497 / 3,497

フロントゲート型SOI−MOSFETの製造方法

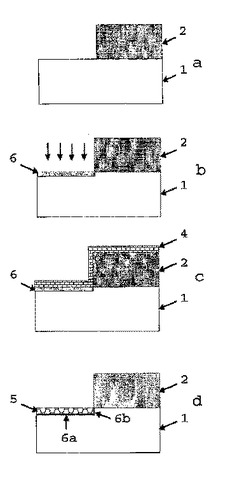

【課題】ソース/ドレイン拡張とフロントゲート(front gate)に自己整合させたバックゲートを含む、FD型SOI−CMOSデバイスの製造方法に関する。

【解決手段】

SOI−CMOS技術は、ポリシリコン、即ちポリSiバックゲートは、フロントゲート・デバイスの閾値電圧を制御するために使用され、nMOS及びpMOSバックゲートは、互いに独立に、及びフロントゲートと独立に、スイッチされる。

特に、バックゲートが、デバイスのフロントゲート及びソース/ドレイン拡張に自己整合されたバックゲートFD型CMOSデバイスの製造方法を提供する。バックゲートFD型CMOSデバイスは、SIMOX又は結合SOI−ウエハ、ウエハボンディングと薄膜化、ポリSiエッチング、LP−CVD、機械化学研磨(CMP)を用いて製造される。

(もっと読む)

線状素子

柔軟性、可撓性があり任意の形状に集積回路を作成できるという特徴を持つ線状MISFETでは、ソース領域とドレイン領域を並列配置する構造が使用されていた。しかし、MISFETの電気特性を決めるチャネル長が円筒形のゲート絶縁領域に沿ったソース領域とドレイン領域の距離できまるため、チャネル長の微細化や再現性向上が困難だった。 MISFETの構造を、ソース領域とドレイン領域でチャネル領域となる半導体領域を挟む構造とした。半導体領域にゲート絶縁領域を介して制御電圧を加え、ソース領域とドレイン領域間で流れる電流を制御する。チャネル長が、半導体領域の膜厚で決まるため、チャネル長の微細化や再現性向上が可能になった。 (もっと読む)

接点の製作方法とその接点を持つ電子部品

この発明は、ケイ化物(5)などの第一の層とそれに隣接する層との間に、不活性化した境界面(6a,6b)を製作する方法に関する。この方法の間には、S、Se、Teなどの不活性化元素を、この層構造の中に組み入れるとともに、温度処理の間に、少なくとも第一の層の隣接層との境界面において濃縮させる。こうすることによって、ショットキー障壁を低下させるとともに、遷移域の仕事関数を調節すことに成功した。例えば、ソース接点とドレイン接点の両方又は一方のショットキー障壁が低い又はそれどころか負であるショットキー障壁MOSFETとスピントランジスターの素子を開示している。  (もっと読む)

(もっと読む)

半導体部品およびその製造方法

本発明は、有機半導体、特に有機電界効果トランジスタ、との静電的相互作用を制御するための層(10)を備える半導体部品に関するものである。上記半導体部品は、上記化合物が、a)基板と結合するために、少なくとも1つのアンカー基(1)を有する化合物を含み、b)当該化合物は、少なくとも1対の自由電子対および/または双極子モーメントを有する少なくとも1つの基(2)をすることを特徴とする。さらに、本発明は、そのような化合物を含む層を形成させるための方法に関するものであり、当該方法によれば、特に、論理関数を付加的に補正(レベルシフト)しなくてもよいOFETを製造することができる。  (もっと読む)

(もっと読む)

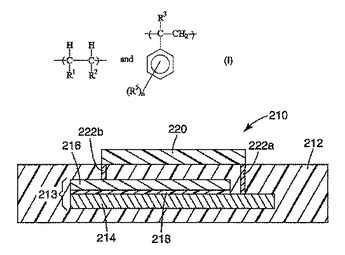

金属電極を備えているトランジスタデバイスおよびそのようなデバイスを形成する際に用いるための方法

金属ソース電極と、金属ドレイン電極と、金属ゲート電極と、堆積させた半導体材料内のチャネルとを有するトランジスタデバイスであって、金属ゲート電極、金属ソース電極の第1の金属部分、および金属ドレイン電極の第1の金属部分を含む第1の層と、金属ソース電極の第2の金属部分、金属ドレイン電極の第2の金属部分、堆積させた半導体材料、および半導体材料と金属ゲート電極との間にある誘電体材料を含む第2の層と、基板を含む第3の層とを含み、第1の層、第2の層および第3の層は、第2の層が第1の層と第3の層との間に配置されるような順序で構成されているトランジスタデバイス。  (もっと読む)

(もっと読む)

基材上に充填誘電体材料のパターンを形成するための方法

基材と、誘電体材料の転写層とを含んでなる熱的に画像形成可能なドナー素子を熱に曝す工程を含んでなる、熱転写プロセスによって充填誘電体材料のパターンを基材上に形成する方法を開示する。照射パターンは、誘電体材料層の部分が、電子デバイスが形成されている基材上に転写されるように、基材上に形成すべき所望のパターンの画像である。充填誘電体材料は、薄膜トランジスタのゲート電極上にパターン化することができる。パターン誘電体材料は、また、相互接続のための絶縁層を形成してもよい。このプロセスでの使用のためのドナー素子も開示する。熱転写プロセスでの使用のための薄膜トランジスタおよびドナー素子を形成するための方法も開示する。  (もっと読む)

(もっと読む)

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

欠陥解析を実行するための方法及びそのシステム

回路欠陥解析及びプロセス問題識別を実行するための方法は、テスト信号を回路に印加するステップと、テスト信号に応答して生成された応答信号を得るステップと、応答信号を参照情報と比較するステップと、比較するステップの結果に基づいて回路内の欠陥を分類するステップと、欠陥分類に基づいて、欠陥を引き起こした製造プロセスにおける問題を識別するステップとを有している。参照情報は、製造プロセス中に発生する可能性がある予め定義されたタイプの欠陥に対応する1つ又は複数の信号プロフィルを含むことができる。欠陥の分類は、応答信号が、信号プロフィルのうちの1つ又は複数内に入るかどうか判定することによって実行されることが好ましい。応答信号が2つ以上の信号プロフィル内に入る場合には、各プロフィルについて確率を決定することができる。次いで、欠陥は、その信号プロフィルがより高い確率を有する欠陥タイプに対応するものとして分類することができる。処理システムは、同様の方法を使用して、欠陥の分類及びプロセス問題識別を実行する。 (もっと読む)

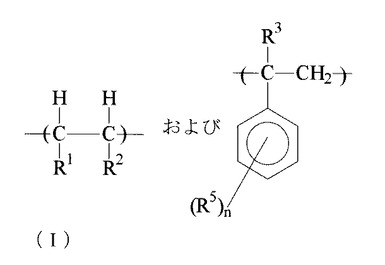

有機ポリマー、ラミネート、およびコンデンサー

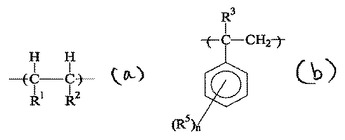

コンデンサーなどのラミネートに使用するための有機ポリマー。このポリマーは、式:

【化1】

で示される反復単位を含む。上記式中、各R1は、独立して、H、アリール基、Cl、Br、I、または架橋性基を含む有機基であり;各R2は、独立して、H、アリール基、またはR4であり;各R3は、独立して、Hまたはメチルであり;各R5は、独立して、アルキル基、ハロゲン、またはR4であり;各R4は、独立して、少なくとも1つのCN基を含みかつCN基1つあたり約30〜約200の分子量を有する有機基であり;そしてnは0〜3に等しく;ただし、ポリマー中の少なくとも1つの反復単位は、R4を含む。

(もっと読む)

(もっと読む)

線パターン形成方法、デバイスとその製造方法及び電気光学装置並びに電子機器

【課題】複数の線パターンの形成領域から一時的に溢れ出した機能液同士が接触しないように機能液を吐出することによって短絡を防止すると共に、線パターンと線パターンとをより近接させる。

【解決手段】線パターンの形成方法であって、隣合うバンク間34から一時的に溢れ出した上記機能液X同士が接触しないように各上記バンク間34の幅方向の中央Aに対し当該幅方向に変位した位置を各々のバンク間34の吐出位置として上記機能液Xを吐出することによって複数の上記バンク間34に同時に機能液を配置する。

(もっと読む)

有機高分子、電子デバイス、および方法

電子デバイスに使用する有機高分子であって、この高分子は、式(a)および(b)の反復単位を含む。式中、高分子内の少なくとも1個の反復単位がR4を含むことを条件として、各R1が、独立してH、アリール基、Cl、Br、I、または架橋可能な基を含む有機基であり、各R2が、独立してH、アリール基、またはR4であり、各R3が、独立してHまたはメチルであり、各R5が、独立してアルキル基、ハロゲン、またはR4であり、各R4が、独立して、少なくとも1個のCN基を含み、CN基あたり約30〜約200の分子量を有する有機基であり、n=0〜3である。これらの高分子は、有機薄膜トランジスタなどの電子デバイスに有用である。

(もっと読む)

(もっと読む)

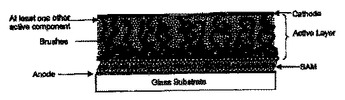

半導体ポリマーブラシを組み込んだ有機電子素子

少なくとも2つの電極と半導体層を含み、その半導体層は少なくとも一の正孔輸送半導体材料と少なくとも一の電子輸送半導体材料の混合物を含むものであって、少なくとも一の前記半導体材料が、少なくとも一の前記電極表面に付着していて且つ少なくとも一の前記の他の半導体性材料と接触している、半導体ポリマーブラシの形状を有する有機電子素子。また、少なくとも2つの電極と半導体層を含み、その半導体層は少なくとも一の正孔輸送半導体材料または少なくとも一の電子輸送半導体材料を含むものであって、前記少なくとも一の半導体材料が、少なくとも一の前記電極表面に付着している、半導体ポリマーブラシの形状を有する有機電子素子。前記素子の製造方法も提供されている。  (もっと読む)

(もっと読む)

自己組織化単分子層を含む電子デバイスおよびこれを製造する方法

【課題】 電子特性が向上した分子層を有する電子デバイスを提供すること。

【解決手段】 電子デバイスは、ソース領域およびドレイン領域と、ソース領域およびドレイン領域に隣接して配置され、少なくとも1つの共役分子を含む自己組織化単分子層と、自己組織化単分子層に隣接した導電性基板と、を含む。

(もっと読む)

有機薄膜トランジスタ

【課題】特殊な技術を要せず、簡単な製造方法でキャリア移動度が高い有機薄膜トランジスタを提供すること。

【解決手段】有機半導体層に重量平均分子量2000以上のπ共役系ポリマー及び分子量2000以下のπ共役系オリゴマーを含有することを特徴とする有機薄膜トランジスタ。

(もっと読む)

配線構造、表示装置および能動素子基板

【課題】 パターニングフリーの能動素子基板の提供。

【解決手段】 能動素子基板は、基板上に形成された能動素子1と、能動素子1上に形成された導電膜2とを有する。導電膜2は、能動素子1から出力された電気信号を有限範囲内に伝達する。

(もっと読む)

液晶表示装置の製造方法

【課題】 画素電極近傍の光り抜けを防止できるアクティブマトリックス型液晶表示装置の製造方法を提供すること。

【解決手段】 アレイ基板に対して略平行な電界を発生させることにより、液晶分子の配列を変化させる、アクティブマトリックス型液晶表示装置において、アレイ基板10上に、配線を形成した後透明な絶縁膜20を成膜する工程と、該配線側面に、該配線の膜厚に対する比が0.5以上1.0以下の膜厚の前記絶縁膜を残すように、該絶縁膜をドライエッチングする工程と、前記配線の膜厚に対する比が0.2以下の膜厚の前記配線のみ、ウェットエッチングする工程とを含むようにした。

(もっと読む)

液晶表示装置およびその作製方法

【課題】 IPS方式の液晶表示装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現する。

【解決手段】 本発明では、チャネル・エッチ型のボトムゲートTFT構造を採用し、ソース領域119及びドレイン領域120のパターニングとソース配線121及び画素電極122のパターニングを同じフォトマスクで行うことを特徴とする。

(もっと読む)

3,481 - 3,497 / 3,497

[ Back to top ]