Fターム[5F110HK50]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | その他 (65)

Fターム[5F110HK50]に分類される特許

1 - 20 / 65

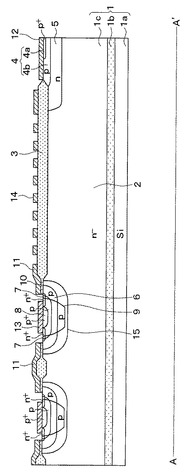

横型の絶縁ゲート型バイポーラトランジスタを備えた半導体装置

【課題】オン電圧の低減と、破壊耐量確保、高速スイッチングを同時に実現できる横型IGBTを提供する。

【解決手段】エミッタ側にn型バリア層15を形成することで、ホールのバリアとして機能させ、コレクタ側から注入されたホールがエミッタ側のチャネルpウェル層6に流れ出てホール濃度が低下することを防止する。これにより、エミッタ近傍のn-型ドリフト層2内のキャリア濃度を上げることが可能となり、オン電圧の低減が可能となる。また、コレクタ側において、コレクタ電極12のうちp+型層4aと接触している部分をオーミック接触、p型層4bと接触している部分をショットキー接触とする。このショットキー接触とされた部分において、コレクタ側からのホールの注入が抑制され、蓄積キャリアを低減して、寄生バイポーラトランジスタがオンし難くなるようにできる。よって、低オン電圧を維持しながらスイッチング耐圧を確保することが可能となる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成し、ドレイン電極と該ソース電極との間にフローティングガードリングを設けることによって、ノーマリ−オフで動作する半導体素子を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間で窒化物半導体層30にショットキー接合されたフローティングガードリング75と、ドレイン電極50とソース電極60との間及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、誘電層40上に形成され、一部が、誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

電界効果トランジスタ、製造用基板、およびその製造方法

【課題】電流量の減少や断線などの問題を抑制した状態で、電界効果トランジスタをより微細化できるようにする。

【解決手段】基板101の上に形成されたグラフェンからなるフィン状のチャンネル領域102と、ゲート電極104およびゲート電極104を挟んでチャンネル領域102に接続されたソース電極105およびドレイン電極106とを備える。例えば、チャンネル領域102は、グラフェンが1層から4層程度積層されたものである。図1に示す例では、ゲート電極104は、チャンネル領域102にゲート絶縁層103を介して形成されている。

(もっと読む)

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

半導体素子及び半導体素子形成方法

【課題】ゲルマニウムをチャネル材料とする金属/ゲルマニウムからなるソース/ドレイン構造を有する半導体素子を提供する。

【解決手段】半導体と金属とが接合してソース/ドレイン構造を形成する半導体素子において、ゲルマニウム(Ge)を3価元素(又は5価元素)でドーピングしたp型ゲルマニウム(又はn型ゲルマニウム)をチャネル2の材料とし、当該p型ゲルマニウム(又はn型ゲルマニウム)の任意の結晶面における原子配置と同一の原子配置である結晶面を有する金属3を、前記同一の原子配置である結晶面で接合して界面を形成し、当該形成された界面を用いたソース/ドレイン構造を有する。

(もっと読む)

表示装置及びその作製方法

【課題】ドレイン電極(またはソース電極)と画素電極との間の接触抵抗が生じない表示装置を提供する。

【解決手段】ゲート電極と、前記ゲート電極を覆って設けられたゲート絶縁層と、前記ゲート絶縁層上に設けられた半導体層と、前記半導体層上の一部に接して離間して設けられたソース電極及びドレイン電極と、を有し、前記ソース電極及びドレイン電極の一方は画素電極を兼ねる表示装置とする。前記ソース電極及びドレイン電極の他方は信号線を兼ねる電極であり、該信号線を兼ねる電極上には低抵抗な導電層が設けられていることが好ましい。低抵抗な導電層は、電気メッキ法などにより形成することができる。

(もっと読む)

微結晶シリコン膜の作製方法、半導体装置の作製方法

【課題】高い膜密度を保ちつつ結晶性を高くした微結晶シリコン膜の作製方法を提供する。

【解決手段】本発明の微結晶シリコン膜の作製方法は、絶縁膜55上に、第1の条件により混相粒57aを有する第1の微結晶シリコン膜57をプラズマCVD法で形成し、その上に、第2の条件により第2の微結晶シリコン膜59をプラズマCVD法で形成する。第1の条件は、処理室内に供給する原料ガスとしてシリコンを含む堆積性気体と水素が含まれたガスを用い、処理室内の圧力を67Pa以上1333Pa以下とする条件であり、第1の条件における原料ガスの供給は、堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈したガスの供給と、当該ガスの堆積性気体の流量より低く、且つ絶縁膜上へのシリコンの堆積より絶縁膜上に堆積したシリコンのエッチングが優位となる堆積性気体の流量にしたガスの供給を交互に行うものである。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させ、かつ、チップサイズの増加を抑制した、窒化物系半導体装置を提供することができる、窒化物系半導体装置を提供することを目的とする。

【解決手段】ショットキー電極30が、ソース電極24とドレイン電極26とが対向する領域の、ソース電極24とドレイン電極26とが対向する方向と略直交する方向にゲート電極28と並んで形成されている。ショットキー電極30は、AlGaN層20とショットキー接合されており、ソース電極24に電気的に接続されている。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

垂直TFETの製造方法

【課題】ヘテロ構造ナノワイアを有するトンネル電界効果トランジスタと集積されたナノワイアを有する相補型トンネル電界効果トランジスタの製造方法を提供する。

【解決手段】犠牲材料21の層を有するチャネル材料34の層を含むスタック24を形成する工程と、チャネル材料34の層と犠牲材料21の層から、少なくとも1つのナノワイヤ30を形成するために、スタック24から材料を除去する工程と、第1ドーパント型の少なくとも1つのナノワイヤ30中の犠牲材料21を第1ドーパント型のヘテロ接合材料41で置き換えて、その後に、第2ドーパント型の少なくとも1つのナノワイア中の犠牲材料を、第2ドーパント材料のヘテロ接合材料52で置き換える工程を含み、相補型TFETの容易な製造が可能となる。

(もっと読む)

半導体装置

【課題】電気特性が良好な半導体装置を提供する。または、電気特性が良好な半導体装置を生産性高く作製する方法を提供する。

【解決手段】逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜と、ソース配線及びドレイン配線として機能する配線との間に、微結晶シリコン膜及び一対のシリコンカーバイド膜を有し、微結晶シリコン膜はゲート絶縁膜側に形成され、一対のシリコンカーバイド膜は配線側に形成される。電気特性が良好な半導体装置を、生産性高く作製することができる。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極及びドレイン電極は、第1の導電層と、第1の導電層の端部よりチャネル長方向に伸長した領域を有する第2の導電層と、を含む半導体装置である。

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

半導体装置およびその作製方法

【課題】良好な特性を備えた、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびドレイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、ソース電極およびドレイン電極は、その側面が酸化された酸化領域を有する半導体装置である。なお、ソース電極およびドレイン電極の酸化領域は、300MHz以上300GHz以下の高周波電力、および、酸素とアルゴンの混合ガスを用いたプラズマ処理により形成されたものであることが望ましい。

(もっと読む)

有機発光表示装置及びその製造方法

【課題】酸化物半導体層と多結晶シリコン半導体層を共に用い得る有機発光表示装置及びその製造方法を提供する。

【解決手段】基板本体と、基板本体上に形成された第1ゲート電極及び第2半導体層と、第1ゲート電極及び第2半導体層の上に形成されたゲート絶縁膜と、ゲート絶縁膜を介在して第1ゲート電極及び第2半導体層上にそれぞれ形成された第1半導体層及び第2ゲート電極と、第1半導体層と少なくとも一部が相接して重畳した複数のエッチングストッパ層と、複数のエッチングストッパ層をそれぞれ露出する複数のコンタクトホールを有し、第1半導体層及び第2ゲート電極上に形成された層間絶縁膜と、層間絶縁膜上に形成され、複数のエッチングストッパ層を通じて第1半導体層とそれぞれ直接的/間接的に接続された第1ソース電極及び第1ドレイン電極と、層間絶縁膜上に形成され、第2半導体層と接続された第2ソース電極及び第2ドレイン電極とを含む。

(もっと読む)

アレイ基板及びこれの製造方法

【課題】アクティブ層が乾式エッチングに露出されないことでその表面に損傷が発生しない薄膜トランジスタの製造方法を提供する。

【解決手段】酸化物半導体層上に形成された補助パターンと;補助パターンの中央部を露出させて互いに離隔して形成されたソース及びドレイン電極と;ドレインコンタクトホールを具備して形成された保護層と補助パターンはソース及びドレイン電極と接触する第1領域と、ソース及びドレイン電極間に露出される中央部の第2領域に分けられて、第1領域はチタンまたはチタン合金で構成されてオーミックコンタクト層を形成して、第2領域はチタンまたはチタン合金が完全酸化されて絶縁特性を有するチタン酸化膜を形成することが特徴であるアレイ基板を提供する。

(もっと読む)

薄膜半導体デバイス及びその製造方法

【課題】活性層と半導体層との接触面をホモ接合、あるいはホモ接合に限りなく近づけて、界面のバンド障壁を防止して大きなオン/オフ比を得ることができ、かつ製造コスト及び作業工数を低減できる。

【解決手段】薄膜半導体デバイスが、基板1と、基板1上に積層されたソース及びドレイン電極層3と、ソース及びドレイン電極層3上に積層された結晶性シリコンからなる不純物含有半導体層4と、不純物含有半導体層4上に積層された結晶性シリコンからなる活性層5と、活性層5上に積層されたゲート絶縁膜6と、ゲート絶縁膜6の上に積層されたゲート電極7と、を備え、不純物含有半導体層4と活性層5の接合面において、これらの結晶性を連続にする。

(もっと読む)

絶縁ゲート型電界効果トランジスタ回路

【課題】温度変化による動作特性の低下を抑制する電界効果トランジスタ回路を提案する。

【解決手段】本発明の例に係る絶縁ゲート型電界効果トランジスタ回路は、拡散層をそれぞれ備える第1のソース/ドレイン4S,4Dと、チャネル領域上に設けられる第1のゲート絶縁膜2と、前記第1のゲート絶縁膜2上に設けられる第1のゲート電極3とを有する第1の電界効果トランジスタTrと、半導体基板1とショットキー接合を形成する金属層をそれぞれ備える第2のソース/ドレイン14S,14Dと、チャネル領域上に設けられる第2のゲート絶縁膜12と、第2のゲート絶縁膜12上に設けられる第2のゲート電極13と、を具備し、第1のドレイン4Dと第2のドレイン14Dとが並列に接続される。

(もっと読む)

薄膜トランジスタ

【課題】しきい値電圧の制御が可能であり、且つオン電流が高く、オフ電流の低い薄膜トランジスタを提供する。

【解決手段】ゲート電極と、ゲート電極上に形成される第1のゲート絶縁層と、第1のゲート絶縁層上に形成される微結晶半導体層と、微結晶半導体層上に形成される一対のバッファ層と、一対のバッファ層上に形成される不純物半導体層と、一対の不純物半導体層上に形成される配線と、微結晶半導体層及び配線上に形成される第2のゲート絶縁層と、第2のゲート絶縁層上に形成されるバックゲート電極を有する薄膜トランジスタであり、微結晶半導体層の一対のバッファ層と接する側の面が凹凸状である。

(もっと読む)

1 - 20 / 65

[ Back to top ]