Fターム[5F110HM04]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 形状 (2,461) | 平面形状 (975)

Fターム[5F110HM04]に分類される特許

961 - 975 / 975

シリコン・オン・インシュレータ・ラッチアップ・パルス放射線検出器

【課題】シリコン・オン・インシュレータ技術を使用して形成した放射線検出器を提供すること。

【解決手段】この放射線検出器は、絶縁基板上に形成され、PNPN構造を有するシリコン層と、このPNPN構造上に形成され、PNゲートを有するゲート層とを備える。放射線検出器内の入射放射線に応答してのみ、ラッチアップが生じる。第2の態様は、シリコン・オン・インシュレータPNPNダイオード構造を備えており、放射線検出器内で入射放射線に応答してのみラッチアップが生じる、放射線検出器である。第3の態様は、絶縁基板上に形成されたシリコン層を備えており、このシリコン層が、PNPN構造とPNPN構造の上に形成されたゲート層とを備え、このゲート層がPNゲートを備えており、放射線検出器内で入射放射線に応答してのみラッチアップが生じる、シリコン・オン・インシュレータ放射線検出器である。

(もっと読む)

低ソース・ドレイン容量用高周波トランジスタ・レイアウト

ゲート電極と櫛形ドレイン及びソース電極を有し、櫛形ドレイン電極の複数の指が櫛形ソース電極の複数の指と互い違いに配置されており、ソース及びドレイン電極が多層(110,120,130,149)を有するRF電界効果型トランジスタ。互い違いの量が各層で異なることにより、多層によりもたらされる低電流密度の効果のすべては失うことなく、最適化、特に、低寄生容量が可能となる。指を短くすることにより、ゲート電極から離間した層において互い違いが低減される。互い違いの低減は、最小容量のために急激な互い違いの低減、最小横方向電流密度のためにより緩やかな互い違いの低減により、最適化される。これが、より高温度又はより高入力バイアス電流においても動作を可能にし、一方、依然として、エレクトロマイグレーションの条件を満たす。  (もっと読む)

(もっと読む)

2つの制御領域を有する集積された電界効果トランジスタ、その使用、およびその製造方法

本発明は、特に、SOI技術およびサリサイド技術により、ダブルゲート・トランジスタ(10)として生成される、電界効果トランジスタ(10)に関する。トランジスタ(10)は、5ボルトよりも高いまたは9ボルトよりもさらに高いターンオン電圧に適し、非常に小さなチップ表面のみを必要とする。トランジスタ(10)は基板領域(14)を有する。基板領域(14)は、2つの電極領域(16、18)と、2つの電気的に絶縁性の絶縁層(100、102)であって、基板領域(14)の対向する面に配置され、制御領域(20、22)に隣接する、絶縁層と、少なくとも1つの電気的に絶縁性の領域(12、110)と、導電性の接続領域(28)、または、1つの電極領域(16)と該基板領域(14)との間の導電性の接続領域の部分(230)とに囲まれる。  (もっと読む)

(もっと読む)

複数誘電体のFINFET構造および方法

【課題】基板(110)から伸長するフィン(112、113、114)を覆う異なる厚さのゲート誘電体(502、504)を有するフィン型電界効果トランジスタ(FinFET)構造のための方法および構造を提供すること。

【解決手段】これらのフィンは、中央チャネル領域と、このチャネル領域の両側にソース領域(60)およびドレイン領域(62)とを有する。厚い方のゲート誘電体(504)は、複数層の誘電体(200、500)を含むことができ、薄い方のゲート誘電体(502)は、それよりも少ない層の誘電体(200)を含むことができる。ゲート誘電体とは異なる材料を含むキャップ(116)を、フィンを覆うように配置することができる。

(もっと読む)

垂直型FIN−FETMOSデバイス

【課題】 トランジスタ本体として働く垂直方向のシリコン「フィン」を用いて、低い接触抵抗を持つ高密度の垂直型Fin−FETデバイスを生成すること。

【解決手段】 低い接触抵抗を示す新しいクラスの高密度の垂直型Fin−FETデバイスが説明される。これらの垂直型Fin−FETデバイスは、トランジスタ本体として働く垂直方向のシリコン「フィン」(12A)を有する。ドープされたソース領域及びドレイン領域(26A、28A)が、それぞれフィン(12A)の下部及び上部内に形成される。ゲート(24A、24B)が、フィンの側壁に沿って形成される。適切なバイアスがゲート(24A、24B)に印加されると、電流は、ソース領域(26A)とドレイン領域(28A)との間で、フィン(12A)を通して垂直方向に流れる。pFET、nFET、マルチ・フィン、シングル・フィン、マルチ・ゲート、及びダブルゲートの垂直型Fin−FETを同時に形成するための統合プロセスが説明される。

(もっと読む)

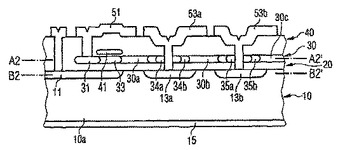

マルチゲート構造の半導体素子及びその製造方法

本発明は、複数のスラブを含むメサ型活性領域を有する半導体素子及びその製造方法を提供する。相互連結されている第1活性領域及び第2活性領域を備え、第1活性領域は基板上にライン・アンド・スペースパターン状に形成され、相互逆方向である第1側面、第2側面及び上面をそれぞれ有する複数のスラブから構成され、第2活性領域は第1活性領域とは同じであるか、または異なる物質からなり、複数のスラブを相互連結させるように、基板上でスラブの少なくとも一端部に接して延びている半導体素子である。該半導体素子を製造するために、まず、ライン・アンド・スペースパターン状の第1活性領域を基板上に形成した後、第2活性領域を形成する。  (もっと読む)

(もっと読む)

絶縁耐力の高いSOI半導体素子

本発明は、第1半導体域と第2半導体域との間に配置されたフィールド電極および/またはフィールド領域を備えた、SOI半導体素子に関するものである。電気的結合を、フィールド電極とフィールド領域との間で行うことができる。  (もっと読む)

(もっと読む)

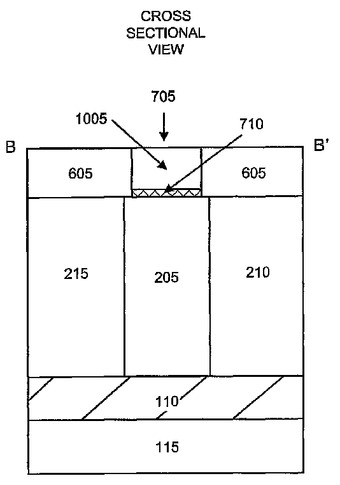

細型化されたボディを有する、狭いボディのダマシン・トライゲートFinFET

フィン(205)を形成するステップと、このフィン(205)の一端上にソース領域(210)、このフィン(205)の他端上にドレイン領域(215)を形成するステップとを含む、フィン電界効果トランジスタを形成する方法である。この方法は、フィン(205)上に、第1パターンで、第1半導体材料のダミーゲート(505)を形成するステップと、このダミーゲート(505)の周りに絶縁層(605)を形成するステップをさらに含んでいる。この方法はまた、第1パターンに対応する絶縁層(605)中にトレンチ(705)を残すように、第1半導体材料を除去するステップと、トレンチ(705)内に露出したフィン(205)の部分を細型化するするステップと、トレンチ(705)内に金属ゲート(1005)を形成するステップと、を含んでいる。  (もっと読む)

(もっと読む)

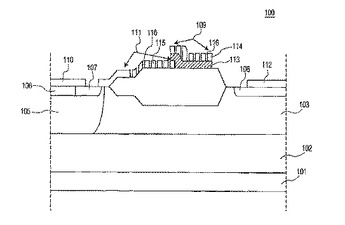

歪みFINFETチャネルの製造方法

例示的実施形態はFinFETチャネル構造の形成法に関する。当該方法において、絶縁層(130)上に化合物半導体層(140)を提供し、化合物半導体層(140)上にトレンチ(142)を提供し、かつ、化合物半導体層(140)上およびトレンチ(142)内に歪み半導体層(144)を提供する。該方法において、さらに、化合物半導体層(140)上から歪み半導体層(144)を除去し、その結果、トレンチ(142)内に歪み半導体層(144)を残し、化合物半導体層(140)を除去して、歪み半導体層(144)を残し、かつ、フィン形のチャネル領域(152)を形成する。  (もっと読む)

(もっと読む)

電界効果トランジスタ及びそれを用いた表示装置

有機物を含有する半導体層(15)と、少なくとも互いに電気的に非接触である第一電極(16)、第二電極(12)及び第三電極(14)を含む電界効果トランジスタであって、半導体層(15)の上方に第一電極(16)が配置され、半導体層(15)の下方に第二電極(12)が配置され、半導体層(15)の側方に第三電極(14)が配置され、半導体層(15)は第一電極(16)、第二電極(12)及び第三電極(14)から選ばれるいずれか2つの電極と電気的に接合され、各電極(12,14,16)間には電気的絶縁体層(13,17)を介在させ、第一電極(16)は半導体層(15)の上方を半導体層(15)の外周部より外側にはみ出して覆っている。これにより、有機半導体を用いた電界効果トランジスタであっても、空気や水に強く、かつ長寿命な電界効果トランジスタ及びそれを用いた表示装置を提供する。 (もっと読む)

1つ以上のトランジスタチャンネルを形成可能な電界効果マイクロエレクトロニクスデバイス

本発明は、電界効果マイクロエレクトロニクスデバイスと、さらにその製造方法に関わる。このデバイスは、基板(700)と、さらに1つ以上のトランジスタチャンネル(transistor channel)を形成することができる少なくとも1つの改善された構造(702)を含む。この構造は、基板上にスタックされた複数のバーによって形成され、電界効果トランジスタの集積化においてスペースを節約することを可能にし、さらにその性能を改善することを可能にする。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

電界効果型半導体装置における容量素子の動的制御

電界効果型装置はキャパシタのプレートをそれぞれ形成する複数のセグメントを有する少なくとも1つのセグメント化されたフィールド・プレートを含んでおり、選択されたセグメントを動的に接続してゲート−ドレイン間容量及びドレイン−ソース間容量を選択的に設定する電子素子に電界効果型装置が接続されている。トランスデューサを送信モードスイッチング装置と、受信モードスイッチング装置との間でスイッチングするスイッチング装置に結合されたトランスデューサを超音波装置が含んでおり、このスイッチング装置は電界効果型装置を含んでいる。  (もっと読む)

(もっと読む)

欠陥解析を実行するための方法及びそのシステム

回路欠陥解析及びプロセス問題識別を実行するための方法は、テスト信号を回路に印加するステップと、テスト信号に応答して生成された応答信号を得るステップと、応答信号を参照情報と比較するステップと、比較するステップの結果に基づいて回路内の欠陥を分類するステップと、欠陥分類に基づいて、欠陥を引き起こした製造プロセスにおける問題を識別するステップとを有している。参照情報は、製造プロセス中に発生する可能性がある予め定義されたタイプの欠陥に対応する1つ又は複数の信号プロフィルを含むことができる。欠陥の分類は、応答信号が、信号プロフィルのうちの1つ又は複数内に入るかどうか判定することによって実行されることが好ましい。応答信号が2つ以上の信号プロフィル内に入る場合には、各プロフィルについて確率を決定することができる。次いで、欠陥は、その信号プロフィルがより高い確率を有する欠陥タイプに対応するものとして分類することができる。処理システムは、同様の方法を使用して、欠陥の分類及びプロセス問題識別を実行する。 (もっと読む)

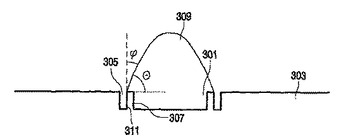

半導体構成用の構造およびその製造方法

本発明は、半導体構成用の構造に関する。半導体を含む溶液の堆積を補助するレジスト構造は、直接、あるいは介在層を介して基板に結合される。このレジスト構造は、半導体を含む溶液(309)を堆積するくぼみ(301)と、くぼみ(309)の縁部の少なくとも一部に整列し、突出部(307)によってくぼみ(309)から分離した溝(305)とを備える。好ましくは、溝(305)は、くぼみ(309)を取り囲む。この溝により、半導体を含む溶液を固定する作用が得られ、それによって濡れ性が改善し、それにしたがって、より大きな体積の半導体を所与の区域に付着させることができる。  (もっと読む)

(もっと読む)

961 - 975 / 975

[ Back to top ]