Fターム[5F110HM13]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 配置 (4,297) | ゲートに対する配置 (3,125)

Fターム[5F110HM13]の下位に属するFターム

オフセット (2,875)

Fターム[5F110HM13]に分類される特許

201 - 220 / 250

半導体装置の作製方法及び半導体装置

【課題】低コストで信頼性が高く、薄膜化された半導体装置の作製方法、及びその方法によって作製された半導体装置を提供する。

【解決手段】基板上に剥離層を形成し、剥離層上にトランジスタを形成し、トランジスタ上に絶縁層を形成した後、剥離層の一部を露出させる開口部を形成し、基板からトランジスタを物理的手段により剥離する。ここで、剥離層の形成は、基板上に金属膜を形成し、溶液を用いる方法でその金属膜上に接して金属酸化膜を形成することによって行われる。

(もっと読む)

半導体装置の作製方法

【課題】耐熱性の低い基板にも低抵抗のTiシリサイド層を形成することを課題とする。

【解決手段】Tiシリサイド層の加熱処理工程にレーザー光を用いることで、耐熱性の低い基板上にも低抵抗のTiシリサイド層を形成することができる。シリコンを含む半導体膜に接してTi膜を成膜し、第一の加熱処理により高抵抗のTiシリサイド層を形成し、レーザー照射を用いた第二の加熱処理により、高抵抗のTiシリサイド層を低抵抗のTiシリサイド層にする。本発明によりTiシリサイド層を形成するために高温で加熱処理する必要がないため、基板を制限なく用いることができる。

(もっと読む)

薄膜トランジスタ

【課題】 トランジスタ特性の優れた薄膜トランジスタを提供する。

【解決手段】 薄膜トランジスタは、基体の表面に配置された絶縁層とを備える。絶縁層の表面に配置され、P型のチャンネル部13、N型のソース部12およびN型のドレイン部14を含む半導体層1と、絶縁層を介して配置されたゲート電極11とを備える。半導体層1は、ソース部12からチャンネル部13を通ってドレイン部14まで到達するように形成された引抜き部21を有する。引抜き部21は、P型に形成され、チャンネル部13よりも不純物濃度が高くなるように形成されている。引抜き部21は、線状に形成されている。

(もっと読む)

記憶装置および半導体装置

【課題】製造時以外にデータの書き込み及び消去が可能である不揮発性の記憶装置及びそれを有する半導体装置を提供することを目的とする。また、小型で安価な不揮発性の記憶装置及びそれを有する半導体装置の提供を課題とする。

【解決手段】少なくとも一方が透光性を有する第1の導電層及び第2の導電層と、第1の導電層又は第2の導電層に接する有機化合物層とを有し、有機化合物層は、層内に分散された導電性粒子を有すると共に光異性化しうる部位を有する有機化合物で形成される記憶素子を有する記憶装置である。

(もっと読む)

半導体ウェハ、半導体装置および半導体装置の製造方法

【課題】 デジタル回路およびアナログ回路または高耐圧MOSトランジスタのそれぞれに適切な膜厚のSOI層およびBOX層を備えた半導体基板、半導体装置およびそのような半導体装置の製造方法を提供する。

【解決手段】 半導体ウェハ100は、半導体バルク10と、半導体バルク上に設けられた第1の埋込み絶縁層20と、第1の埋込み絶縁層上に設けられた第1の半導体層30と、第1の半導体層上に設けられた第2の埋込み絶縁層40と、第2の埋め込み絶縁層上に設けられた第2の半導体層50とを備えている。半導体装置は、第1の半導体層のうち第1の領域に形成された第1のトランジスタと、第2の半導体層に形成された第2のトランジスタとを備えている。

(もっと読む)

薄膜半導体装置、電子機器、および薄膜半導体装置の製造方法

【課題】 オン電流特性、オフリーク電流特性およびドレイン耐圧のいずれにも優れたTFTを備えた薄膜半導体装置、この薄膜半導体装置を用いた電子機器、および薄膜半導体装置の製造方法を提供すること。

【解決手段】 薄膜半導体装置1において、TFT10のゲート電極5は、チャネル領域30および境界領域33、38に対向している。ゲート絶縁膜4は、チャネル領域30に重なる第1の絶縁膜部分46と、境界領域33、38と重なる第2の絶縁膜部分47と、ドレイン領域32およびソース領域37と重なる第3の絶縁膜部分48とを備え、第2の絶縁膜部分47は、第1の絶縁膜部分46と隣接する部分では第1の絶縁膜部分46よりも厚く、かつ、第1の絶縁膜部分46から遠ざかるに伴って薄くなっている。境界領域33、38は、チャネル領域30の側から離れるに伴って不純物濃度が漸増している。

(もっと読む)

レーザ照射装置及び半導体装置の作製方法

【課題】それぞれのレーザ発振器から射出したレーザ光のビームスポットの位置及び隣り合うビームスポットの間隔を正確に制御することを可能とするレーザ照射装置の提供。

【解決手段】被照射体が設置された移動可能な第1のステージと、少なくとも2台以上のレーザ光を射出するレーザ発振器と、前記レーザ発振器と光学系が設置された移動可能な複数の第2のステージと、レーザ光の照射位置を検出する手段とを有する。第1のステージ及び第2のステージは、一方向だけでなく複数方向に移動可能なものであってもよい。また、前記光学系は、レーザ発振器から射出したレーザビームを被照射面において線状ビームになるように形成するものである。

(もっと読む)

半導体装置及びその作製方法、並びに半導体装置の測定方法

【課題】特性を劣化させることなく、簡便に物理試験を行うことが可能な半導体装置を提供する。

【解決手段】端子部を有する検査素子が設けられた素子層が、可撓性を有する第1及び第2のフィルムにより封止されている半導体装置の測定方法であって、前記端子部上に形成された前記第1のフィルムを除去して、前記端子部に達するコンタクトホールを形成し、前記コンタクトホールに導電性材料を含有する樹脂を充填し、前記充填された樹脂上に可撓性を有する配線基板を配置させた後に加熱することにより、前記導電性材料を含有する樹脂を介して前記端子部と前記可撓性を有する配線基板とを電気的に接続した後に測定を行う。

(もっと読む)

有機薄膜トランジスタおよびその製造方法

【課題】 印刷方法を用いてソース電極及びドレイン電極を形成した微細なゲート長、ソース電極幅、ドレイン電極幅を有する有機薄膜トランジスタを提供する。

【解決手段】 基板、ゲート電極、ゲート絶縁膜、有機半導体膜、ソース電極、ドレイン電極を有する有機薄膜トランジスタにおいて、少なくとも1つ以上の長方形のソース電極108、109およびドレイン電極110、111が間隔を設けて長手方向が平行で、両端部がずれて交互に配列し、前記ソース電極およびドレイン電極の一方の端部は電極連結部102、113を介して電極配線部102、104に接続されており、かつ前記ソース電極およびドレイン電極が設けられている領域はゲート電極103が設けられている領域内に配置されている有機薄膜トランジスタ。

(もっと読む)

半導体装置及びその作製方法

【課題】LDD領域を有する微細TFTを、工程数の少ないプロセスで作製し、各回路に応じた構造のTFTを作り分けることを課題とする。また、LDD領域を有する微細TFTであってもオン電流を確保することを課題とする。

【解決手段】ゲート電極を2層とし、下層のゲート電極のゲート長を上層のゲート電極のゲート長よりも長くし、ハットシェイプ型のゲート電極を形成する。この際に、レジストの後退幅を利用して上層のゲート電極のみをエッチングし、ハットシェイプ型のゲート電極を形成する。また、配線と半導体膜のコンタクト部をシリサイド化し、コンタクト抵抗を下げる。

(もっと読む)

半導体装置

【課題】高耐圧と低オン抵抗を維持しつつ出力容量をも低減することを可能にした半導体装置を提供する。

【解決手段】p−型活性層3は、厚さの大きい肉厚部分と厚さの小さい肉薄部分とを有する。肉厚部分において選択的に、表面からSOI絶縁層2に到達する深さに亘って、p型ベース層4が形成されている。このp型ベース層4の表面部分には、n+型ソース層5が選択的に形成されている。肉薄部分において、p型ベース層4と所定間隔を空けて選択的に、その表面からSOI絶縁層2に到達する深さに亘って、n型ドレイン層6が形成されている。このn型ドレイン層6は、更にこれよりも高い不純物濃度を有するように形成されたコンタクト層11が接合される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 SOI構造を有する半導体装置において、イオン注入時にイオンが分離酸化膜を突き抜けて、分離酸化膜下層に混入するのを抑えることができるようにする。

【解決手段】 SOI基板のシリコン層を複数の活性領域に分離する分離絶縁膜を形成して、ゲート絶縁膜を介して、ゲート電極を形成する。そして、分離絶縁膜の表面が露呈する部分を、所定の膜厚分エッチングする。その後、少なくともゲート電極の膜厚よりも厚く、かつ、ゲート電極の膜厚と分離絶縁膜のエッチング膜厚とを合計した膜厚よりも薄いシリコン酸化膜を形成し、このシリコン酸化膜上に、エッチングストッパ膜を形成する。その後、ゲート電極表面が露呈するまで平坦化を行う。平坦化後、シリコン酸化膜上に残ったエッチングストッパ膜をマスクとして、シリコン酸化膜のエッチングを行い、このシリコン酸化膜、及び、ゲート電極をマスクとして、シリコン層にイオン注入を行う。

(もっと読む)

薄膜トランジスタアレイ基板及びその製造方法、並びに液晶ディスプレイパネル

【課題】 接合容量(Cgd)を減少し、フィードスルー効果、又は接合容量(Cgd)が大き過ぎることで生じる問題を改善できる薄膜トランジスタ構造を提供する。

【解決手段】 薄膜トランジスタアレイ基板は、基板300、前記基板300の上に形成されるゲート電極302、前記基板300と前記ゲート電極302を覆うゲート誘電体層308、前記ゲート誘電体層308の上に形成され、チャネル712を含む半導体層314、前記半導体層314における前記チャネル712の一方の側の部分と電気的に接続されたソース電極322、及び前記半導体層314における前記チャネル712の他方の側の部分と電気的に接続され、前記ゲート電極302に重ならないようにして配置されたドレイン電極324を備える。

(もっと読む)

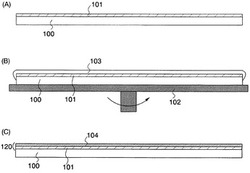

剥離方法

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って剥離することを可能とする。また、被剥離層の形成において、熱処理温度、基板の種類等の限定を受けない剥離方法を提供する。

【解決手段】基板上に金属層を形成し、前記金属層上に酸化物層を形成し、前記酸化物層上に被剥離層を形成し、前記被剥離層を前記金属層が設けられた基板から前記酸化物層の層内または界面において物理的手段により剥離する。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程でNiシリサイドを形成する。

【解決手段】基板上に半導体膜を形成し、前記基板を加熱しながら前記半導体膜上にNi膜を成膜することにより、前記半導体膜にNiシリサイドを形成することを特徴とする。また基板上に半導体膜を形成し、前記基板を450℃以上に加熱しながら前記半導体膜上にNi膜を成膜することにより、前記半導体膜にNiシリサイドを形成することを特徴とする。また基板上に半導体膜を形成し、前記基板を450℃以上に加熱しながら前記半導体膜上にNi膜を10nm以上成膜することにより、前記半導体膜にNiシリサイドを形成することを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】ゲート電極や配線を低抵抗な金属膜を用いて形成することにより、大面積なデバイスにも対応できる半導体装置の作製方法を提供する。

【解決手段】基板上にアルミニウムを主成分とする第1の導電層を形成し、前記第1の導電層上に当該第1の導電層と異なる材料からなる第2の導電層を形成し、前記第1の導電層及び前記第2の導電層をパターニングしてゲート電極を形成することを特徴とする。また、前記第1の導電層は、炭素と、クロム、タンタル、タングステン、モリブデン、チタン、シリコン、ニッケルのいずれか一又は複数を含有していることを特徴とする。前記第2の導電層は、クロム、タンタル、タングステン、モリブデン、チタン、ニッケルまたはこれらの窒化物のいずれか一又は複数からなることを特徴とする。

(もっと読む)

半導体装置およびその作製方法、並びに電子機器

【課題】アクティブマトリクス型の半導体装置のゲート電極とゲート配線の配置を工夫することにより、画面の大面積化を可能とする。

【解決手段】表示領域に設けられた画素TFTが含むゲート電極は、第1の導電層により形成されている。また、表示領域に設けられたゲート配線は、第2の導電層で形成されている。ゲート電極はゲート配線と接続部で電気的に接触している。接続部は、画素TFTが含む半導体層の外側に設けられている。

(もっと読む)

表示装置及びその駆動方法

【課題】 画面の縦横表示の切替が可能な表示装置を提供する。

【解決手段】 第1のゲート信号線駆動回路の走査方向は、ソース信号線駆動回路の走査方向と垂直をなし、第2のゲート信号線駆動回路の走査方向は、第1のゲート信号線駆動回路の走査方向と垂直をなす。通常表示の際は、画面の垂直走査は第1のゲート信号線駆動回路によって行う。一方、縦横表示を切り替える際には、画面の垂直走査は第2のゲート信号線駆動回路によって行う。画素はフィールドシーケンシャルで駆動され、画素内がRGBに分割されないため、縦横切換が容易になる。

(もっと読む)

表示装置の作製方法

【課題】本発明は、しきい値のずれが生じにくく、高速動作が可能な逆スタガ型TFTを有する表示装置の作製方法を提供する。また、スイッチング特性が高く、コントラストがすぐれた表示が可能な表示装置の作製方法を提供する。更には、少ない原料でコスト削減が可能であり、且つ歩留まりが高い表示装置の作製方法を提供する。

【解決手段】 本発明は、耐熱性の高い材料でゲート電極を形成した後、非晶質半導体膜の結晶化を促進する触媒元素を有する層、非晶質半導体膜、及びドナー型元素又は希ガス元素を有する層を形成し加熱して、非晶質半導体膜を結晶化すると共に触媒元素を結晶性半導体膜から除いた後、該結晶性半導体膜の一部を用いて半導体領域を形成し、該半導体領域に電気的に接するソース電極及びドレイン電極を形成し、ゲート電極に接続するゲート配線を形成して、逆スタガ型TFTを形成する。

(もっと読む)

表示装置の作製方法

【課題】本発明は、しきい値のずれが生じにくく、高速動作が可能な逆スタガ型TFTを有する表示装置の作製方法を提供する。また、スイッチング特性が高く、コントラストがすぐれた表示が可能な表示装置の作製方法を提供する。

【解決手段】 本発明は、耐熱性の高い材料でゲート電極を形成した後、非晶質半導体膜の結晶化を促進する触媒元素を有する層、非晶質半導体膜、及びドナー型元素又は希ガス元素を有する層を形成し加熱して、非晶質半導体膜を結晶化すると共に触媒元素を結晶性半導体膜から除いた後、該結晶性半導体膜の一部を用いて半導体領域を形成し、該半導体領域に電気的に接するソース電極及びドレイン電極を形成し、ゲート電極に接続するゲート配線を形成して、逆スタガ型TFTを形成する。

(もっと読む)

201 - 220 / 250

[ Back to top ]