Fターム[5F110HM13]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 配置 (4,297) | ゲートに対する配置 (3,125)

Fターム[5F110HM13]の下位に属するFターム

オフセット (2,875)

Fターム[5F110HM13]に分類される特許

101 - 120 / 250

トランジスタ基板及びトランジスタ基板の製造方法

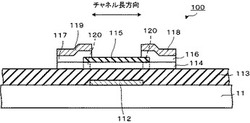

【課題】微結晶シリコンをチャネル領域として用い、良好にリーク電流を抑制することが可能なトランジスタを備えるトランジスタ基板及びトランジスタ基板の製造方法を提供する。

【解決手段】トランジスタ基板におけるトランジスタ100は、基板11と、ゲート電極112と、ゲート絶縁膜113と、半導体層(チャネル領域)114と、ドレイン領域116、ソース領域117と、ドレイン電極118と、ソース電極119と、を備える。ドレイン領域116と半導体層114が接触する箇所及びソース領域117と半導体層114が接触する箇所のうち少なくとも一方は、ゲート電極112と比較し、薄膜トランジスタ100のチャネル長方向に外側に位置するように形成されている。このようにストッパ膜115を形成することにより、電界の急激な変化を抑制することができ、良好にリーク電流を抑制することができる。

(もっと読む)

画像表示パネル及び画像表示装置

【課題】製造コストを上昇させることなくマイグレーション耐性の向上及び有機半導体の劣化の抑制を実現可能な画像表示パネル及び画像表示装置を提供する。

【解決手段】第一の基板上にゲート電極、ゲート絶縁膜が積層形成され、ゲート絶縁膜上に空隙を隔ててソース電極及びドレイン電極並びに第二の接着剤が形成され、ソース電極及びドレイン電極の空隙を含む領域に有機半導体層が形成され、ゲート絶縁膜、ソース電極、ドレイン電極の一部、及び有機半導体層を覆うように層間絶縁膜が形成され、層間絶縁膜及びドレイン電極と接合されている導電層上に第一の接着剤、第一の接着剤上に形成された画像表示媒体及び第二の接着剤上に無機膜および第二の基板を有する画像表示パネルであって、第二の接着剤は、画像表示媒体と導電層との間に配置された第一の接着層よりも外側に配置され、無機膜及び親水化処理されたゲート絶縁膜と接合形成する。

(もっと読む)

発光装置の作製方法

【課題】基板に対する剥離・転写の工程を簡略化した方法を提供する。

【解決手段】基板上に金属膜を形成し、加熱処理を行うことで、金属膜上に形成された酸化金属膜と、半導体膜の結晶化を同時に行うことができ、工程が簡略化された剥離・転写の方法である。金属膜にはタングステン膜などを用い、均一な剥離・転写を行うことができる。半導体膜に電気的に接続される電極上に発光層を形成することで発光装置の作製方法を提供することができる。

(もっと読む)

トランジスターの製造方法

【課題】アルミニウムやマグネシウムを用いた金属層を形成し400℃程度で熱処理することで、ゲート絶縁層中の不純物を不活性化できるが、当該金属層はヒロックが発生しやすい等、ゲート電極としては適当なものではなく、一旦、当該金属層を除去して、新たにゲート電極を形成する必要がある。この工程では、エッチング雰囲気中にゲート絶縁層を露出させる必要が生じ、ゲート絶縁層の劣化が懸念される。

【解決手段】TiNをスパッタ法にて堆積し、エッチングを行うことで第1ゲート電極106を形成する。そしてアルミニウムを主成分とする触媒金属層108をスパッタリング法等を用いて堆積する。そして、触媒金属層108が堆積された状態で、400℃で1時間熱処理を行う。この熱処理を行うことにより、ゲート絶縁層15と半導体層13との界面の欠陥準位密度を低減させることができた。

(もっと読む)

半導体装置の作製方法

【課題】TFTを用いた半導体装置において、TFT中の汚染不純物を低減し、信頼性のあるTFTを得ることを課題とする。

【解決手段】ガラス基板上のTFTの被膜に存在する汚染不純物を、フッ素を含有する酸性溶液を被膜表面に接触させ、酸性溶液を一定方向に流すことにより、被膜表面の汚染不純物を除去することにより、信頼性のあるTFTを得ることができる。なお、酸性溶液は、フッ酸とフッ化アンモニウムの混合比が体積比で1:50のバッファードフッ酸を用いる。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

半導体装置及び製造方法

【課題】 オフリーク電流が低減され、電流の立ち上がり特性も良好な結晶性シリコン薄膜半導体装置を提供する。

【解決手段】 非晶質シリコン層及び結晶性シリコン層を半導体層とする薄膜トランジスタにおいて、ドレイン電極が、半導体層の結晶性シリコン層と直接接することにより、電流の立ち上がり特性を向上させることを特徴とする薄膜トランジスタ。

(もっと読む)

MOSトランジスタおよび該MOSトランジスタを内蔵した半導体装置ならびに該半導体装置を用いた電子機器

【課題】低閾値電圧で、オン抵抗が小さくできる低電力消費で高耐圧のMOSトランジスタに関する技術の提供。

【解決手段】半導体基板10上に設けられた埋め込み酸化膜11,不純物濃度が第1濃度のシリコン層12,不純物濃度が第1濃度より低い第2濃度のエピタキシャル層13と、エピタキシャル層の表面から埋め込み酸化膜11に達する低濃度の第1導電型のドレイン領域15、埋め込み酸化膜に達する第2導電型のチャネル領域14、高濃度の第1導電型のソース領域16と、チャネル領域14とドレイン領域15の一部を覆うゲート電極21と、ゲート電極とエピタキシャル層の間のゲート酸化膜20と、ドレイン領域内のゲート電極から離れた高濃度の第1導電型で形成されたドレインオーミック領域15cと、高濃度の第2導電型のチャネルオーミック領域14dを備え、ゲート電極直下に第2濃度よりさらに低濃度のチャネルドープ領域14cを形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】GIDL電流が発生することを抑制する。

【解決手段】第2導電型高濃度不純物層170は、素子形成領域110に形成されており、ソース及びドレインとして機能する。第2導電型低濃度不純物層160は、第2導電型高濃度不純物層170それぞれの周囲に設けられている。第2導電型低濃度不純物層160は、第2導電型高濃度不純物層170を深さ方向及びチャネル長方向に拡張し、第2導電型高濃度不純物層170より不純物濃度が低濃度である。第2導電型低濃度不純物層160は、少なくとも一部がゲート電極140及びゲート絶縁膜180の下に位置している。そしてゲート絶縁膜180は、第2導電型低濃度不純物層160上に位置する部分に傾斜部182を有している。傾斜部182は、ゲート電極140の中央部側から側面に向かうにつれて、変局点がないように膜厚が連続的に厚くなっている。

(もっと読む)

半導体装置の製造方法、半導体装置、電気光学装置および電子機器

【課題】ボトムゲート構造およびトップゲート構造の双方の特長を兼ね備えた半導体装置の製造方法、半導体装置、電気光学装置、および電子機器を提供すること。

【解決手段】素子基板10上の薄膜トランジスター30は、ボトムゲート構造を備え、かつ、ポリシリコン膜からなる島状半導体膜1aにチャネル領域1g、低濃度ソース領域1b、低濃度ドレイン領域1c、高濃度ソース領域1d、高濃度ドレイン領域1eを備えたGOLD構造を備えている。素子基板10を製造する際、諧調露光により形成したレジストマスクと、かかるレジストマスクに対するエッチバックを利用して、高濃度不純物の導入、半導体膜のパターニングと、ゲート絶縁膜2aと同層の層間絶縁膜のコンタクトホールを形成すべき領域からの半導体膜の除去、および低濃度不純物の導入とを行なう。

(もっと読む)

半導体装置

【課題】半導体膜の厚みを適当な範囲に制御することによって、大きいドレイン電流を有するとともに、所望の電気的特性を備える半導体装置を提供する。

【解決手段】半導体装置は、主表面1aを有するガラス基板1と、主表面1a上に設けられ、チャネル領域11と、チャネル領域11の両側に位置するソース領域9およびドレイン領域13とが形成されたポリシリコン膜7と、ポリシリコン膜7に接触するように設けられたゲート絶縁膜17と、ゲート絶縁膜17を介してチャネル領域11に向い合う位置に設けられたゲート電極21とを備える。ポリシリコン膜7は、50nmを超え150nm以下の厚みを有する。ソース領域9およびドレイン領域13は、ポリシリコン膜7の頂面7aからポリシリコン膜7の底面7cにまで達して形成されている。

(もっと読む)

透過型液晶表示装置、プロジェクター及びデジタルカメラ

【課題】シフトレジスタ、バッファ回路など駆動回路を同一基板上に組込んだアクティブマトリクス型液晶表示装置において、画素部の開口率を向上させると共に最適なTFTの構成を提供する。

【解決手段】バッファ回路にはゲート電極とオーバーラップするLDDを設けたnチャネル型TFTを形成し、画素部のnチャネル型TFTにはゲート電極とオーバーラップしないLDDを設けた構造とする。画素部に設ける保持容量は、遮光膜と遮光膜上に形成される誘電体膜と画素電極で形成し、特に遮光膜にAlを用い、誘電体膜を陽極酸化法で形成し、酸化Al膜を用いる。

(もっと読む)

薄膜トランジスタ、その製造方法および表示装置

【課題】大きなオン電流を維持したままオフ電流を低減するとともに、製造が容易なLDD領域を備える薄膜トランジスタを提供する。

【解決手段】平面視において、ドレイン電極171をゲート電極121から所定の距離だけ離して形成することによって、LDD領域165となるオーミックコンタクト層161を水平方向に形成する。この場合、LDD領域165は、ゲート電極121の電位に基づく電界の影響を受けにくくなり、実質的にドレイン電極171の電位に基づく電界による電界集中のみを緩和する。したがって、TFT100は、結晶性シリコン膜からなるチャネル領域141cを形成することにより、大きなオン電流を維持することができると同時に、オフ電流を十分低減することができる。

(もっと読む)

半導体装置および電子機器

【課題】GOLD構造を持つTFTを形成した場合、中間濃度層とゲート電極とが重なる領域の長さ(以下、「GOLD長」と呼ぶ)が長くなるにつれて、トランジスターを構成するチャネル領域を挟む、ソース−ドレイン間の漏れ電流が増加し、消費電力の増加が生じる。また、液晶装置や有機EL装置に適用した場合に顕著となる、映像信号の保持を可能とする時間の低下による映像品質の低下が生じるという課題がある。

【解決手段】TFTのGOLD長をTFT幅方向の両端での長さを中央部の長さと比べて短くした。島状のシリコン層の幅方向の端部には、キャリアを発生させる欠陥準位が幅方向の中央部と比べ多く存在する。この領域でのGOLD長を中央部と比べ短縮することで、この欠陥準位からのキャリア発生を抑制し、漏れ電流を減らした。

(もっと読む)

半導体装置及びその作製方法

【課題】チャネルが形成される第1半導体層とソース電極層及びドレイン電極層が接する界面のコンタクト抵抗が高くなる一因は、ソース電極層及びドレイン電極層となる金属材料の表面がゴミや不純物によって汚染され、電気抵抗が高い皮膜が形成される現象である。そこで、皮膜の形成から表面が保護されたソース電極層及びドレイン電極層と第1半導体層が接する半導体装置及びその作成方法を提供する。

【解決手段】成膜後の導電膜を大気にさらすことなく、導電膜上に連続して第1半導体層以下の導電率を有する第2半導体膜を含む保護膜を積層し、当該積層膜をソース電極層及びドレイン電極層に形成し、ソース電極層及びドレイン電極層が第2半導体膜を介して第1半導体層に接する。

(もっと読む)

ワイヤソース及びドレインを備えたトランジスタ

【課題】従来とは異なる構造を有し、かつ複雑ではなく安価な製造方法で実現され得る電界効果トランジスタを提供する。

【解決手段】少なくともゲート(1)と、絶縁体層(2)と、ドレイン(3)と、ソース(4)と、ソース(4)をドレイン(3)に接続する半導体材料(50)とを含み、ゲート(1)及び絶縁体層(2)は各々ソース(4)、ドレイン(3)、及び半導体材料によって構成されるアセンブリを囲み、絶縁体層(2)がゲート(1)と前記アセンブリとの間に配置される電界効果トランジスタ

ドレイン(3)及びソース(4)は各々第1及び第2の導電体によって構成され、平行に配置され、かつ互いに非接続であり、第1及び第2の導電体はそれらの外周全体にわたって、及び少なくともそれらの長さの一部にわたって半導体材料(50)の層によって囲まれる。

(もっと読む)

有機トランジスタアレイ、表示パネル及び表示装置

【課題】オフ電流を低減することが可能な有機トランジスタアレイ、表示パネル及び表示装置を提供する。

【解決手段】マトリクス状に設けられている走査線11及び信号線12と、走査線11と接続するゲート電極21と、ゲート電極21及び走査線11を覆うように形成されている第1のゲート絶縁膜と、信号線12と接続するソース電極23と、チャネル領域Cを挟んでソース電極23と対向して形成されているドレイン電極24と、チャネル領域Cに形成されている有機半導体層25とを備え、走査線11及び信号線12が交差して形成されている画素領域A1、A2に設けられる有機トランジスタ20とを有する有機トランジスタアレイ10において、ゲート電極21は、更に平面視でドレイン電極24と信号線12とに挟まれる領域Sに形成され、有機半導体層25は、更に平面視でドレイン電極24と信号線12に挟まれる領域S1に形成されている。

(もっと読む)

発光装置の作製方法及び液晶表示装置の作製方法

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って剥離することを可能とする。

【解決手段】基板上に金属層を形成する工程と、前記金属層上に酸化物層を形成する工程と、前記酸化物層上に絶縁層を形成する工程と、前記絶縁層上に薄膜トランジスタを形成する工程と、前記薄膜トランジスタ上に発光素子を形成する工程と、人間の手又は前記薄膜トランジスタを引き剥がす装置を用いることにより、前記酸化物層の層内または界面において前記基板から前記薄膜トランジスタを剥離する工程とを有する。

(もっと読む)

半導体装置

【課題】 小型であり、順方向と逆方向の双方で導通可能(スイッチング可能)な半導体装置を提供する。

【解決手段】 第1導電型の第1領域30と、第2導電型であり、第1領域30に接している第2領域32と、第1導電型であり、第2領域32によって第1領域から分離されている第3領域36と、第2導電型であり、第3領域36によって第2領域32から分離されている第4領域22と、第1導電型であり、第4領域22によって第3領域36から分離されている第5領域20と、第1領域30及び第2領域34と導通している第1電極56と、第4領域22及び第5領域20と導通している第2電極54と、第2領域32に対して絶縁膜42を介して対向している第1ゲート電極44と、第4領域22に対して絶縁膜50を介して対向している第2ゲート電極52を備えていることを特徴とする半導体装置。

(もっと読む)

表示装置

【課題】狭額縁化が可能であり、表示特性に優れた表示装置を提供する。

【解決手段】スイッチ部またはバッファ部と、論理回路部と、画素部と、を有する表示装置において、画素部は、第1の逆スタガ型薄膜トランジスタと、第1の逆スタガ型薄膜トランジスタの配線に接続する画素電極と、を有し、スイッチ部またはバッファ部は、第1の絶縁層、半導体層、及び第2の絶縁層を挟む第1のゲート電極及び第2のゲート電極を有する第2の逆スタガ型薄膜トランジスタを有し、論理回路部は、第3の逆スタガ型薄膜トランジスタ及び第4の逆スタガ型薄膜トランジスタにより構成されるインバータ回路を有し、第1の逆スタガ型薄膜トランジスタ乃至第4の逆スタガ型薄膜トランジスタは、同じ極性とする。インバータ回路はEDMOS回路である。

(もっと読む)

101 - 120 / 250

[ Back to top ]