Fターム[5F110HM13]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 配置 (4,297) | ゲートに対する配置 (3,125)

Fターム[5F110HM13]の下位に属するFターム

オフセット (2,875)

Fターム[5F110HM13]に分類される特許

81 - 100 / 250

半導体装置の製造方法

【課題】半導体膜の厚みを適当な範囲に制御することによって、大きいドレイン電流を有するとともに、所望の電気的特性を備える半導体装置の製造方法、を提供する。

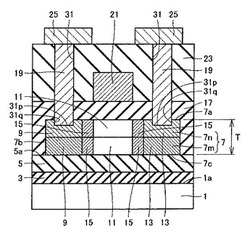

【解決手段】半導体装置の製造方法は、50nmを超え150nm以下の厚みを有し、第1の層7mと第2の層7nとを有する半導体膜7を形成する工程を備える。半導体膜7を形成する工程時、第1の層7mに含まれる水素の割合は、第2の層7nに含まれる水素の割合よりも小さい。半導体装置の製造方法は、半導体膜7を熱処理することによって、半導体膜7に含まれる水素を低減する工程と、ゲート絶縁膜17およびゲート電極21を形成する工程と、半導体膜7にソース領域9およびドレイン領域13を形成する工程と、半導体膜7を水素雰囲気中で熱処理することによって、半導体膜7に含まれる水素を0.5原子%以上10原子%以下に設定する工程とを備える。

(もっと読む)

発光装置の作製方法

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って歩留まりよく剥離することを可能とすることを目的する。また、様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。

【解決手段】基板上に金属層11を設け、さらに前記金属層11に接して酸化物層12を設け、さらに被剥離層13を形成し、前記金属層11をレーザー光で照射することで酸化を行い、金属酸化物層16を形成させれば、物理的手段で金属酸化物層12の層内または金属酸化物層16と酸化物層12との界面において、きれいに分離することができる。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】絶縁表面上に第1配線と、前記第1配線を覆う第1層間絶縁膜と、前記第1層間絶縁膜上の一部に接して第2層間絶縁膜と、前記第1層間絶縁膜及び前記第2層間絶縁膜上に第2配線とを有し、前記第1配線と前記第2配線とが重なっている領域には、前記第1層間絶縁膜と前記第2層間絶縁膜とが積層された半導体装置である。第1配線と第2配線間に層間絶縁膜が積層されていることで寄生容量の低減が可能となる。

(もっと読む)

薄膜トランジスタ、有機電界発光表示装置、薄膜トランジスタの製造方法及び有機電界発光表示装置の製造方法

【課題】半導体層における特性が更に向上した薄膜トランジスタ及び当該薄膜トランジスタを備える有機電界発光表示装置とこれらの製造方法を提供すること。

【解決手段】本発明に係る薄膜トランジスタは、基板上に位置するバッファ層と、前記バッファ層上に位置するソース/ドレイン領域及び1又は複数のチャンネル領域を有する半導体層と、前記基板全面にわたって設けられるゲート絶縁膜と、前記ゲート絶縁膜上に設けられるゲート電極と、前記基板全面にわたって設けられる層間絶縁膜と、前記層間絶縁膜上に位置し、前記半導体層と電気的に接触するソース/ドレイン電極とを含み、前記半導体層のチャンネル領域の多結晶シリコン層は、低角結晶粒界のみを含み、高角結晶粒界は、前記半導体層のチャンネル領域以外の領域に位置する。

(もっと読む)

半導体装置及びその作製方法

【課題】信頼性の高いTFT構造を用いた半導体装置を実現する。

【解決手段】TFTに利用する絶縁膜、例えばゲート絶縁膜、保護膜、下地膜、層間絶縁膜等として、ボロンを含む窒化酸化珪素膜(SiNX BY OZ )をスパッタ法で形成する。その結果、この膜の内部応力は、代表的には−5ラ1010dyn/cm2 〜5ラ10

10dyn/cm2 、好ましくは−1010dyn/cm2 〜1010dyn/cm2 となり、高い熱伝導性を有するため、TFTのオン動作時に発生する熱による劣化を防ぐことが可能となった。

(もっと読む)

半導体装置の作製方法

【課題】基板処理の効率を高めることができ、また半導体膜の移動度を高めることができるレーザー結晶化法を用いた半導体製造装置を提供する。

【解決手段】半導体膜を成膜する成膜装置と、レーザー装置とを備えたマルチチャンバー方式の半導体製造装置であり、レーザー装置は、被処理物に対するレーザー光の照射位置を制御する第1の手段と、レーザー光を発振する第2の手段(レーザー発振装置1213)と、前記レーザー光を加工または集光する第3の手段(光学系1214)と、前記第2の手段の発振を制御し、なおかつ第3の手段によって加工されたレーザー光のビームスポットがマスクの形状のデータ(パターン情報)に従って定められる位置を覆うように前記第1の手段を制御する第4の手段とを有する。

(もっと読む)

フレキシブル半導体装置およびその製造方法

【課題】高性能なフレキシブル半導体装置を提供すること。

【解決手段】金属箔から成る支持層、支持層の上に形成された半導体構造部、および半導体構造部の上に形成された樹脂フィルムを有して成るフレキシブル半導体装置。かかるフレキシブル半導体装置では、樹脂フィルムには開口部が形成されており、その開口部に半導体構造部の表面と接触する導電部材が形成されており、半導体構造部が半導体層および半導体層の表面に形成された絶縁層を有して成る。

(もっと読む)

表示装置

【課題】光源側にゲート電極膜を有するTFTを用いた表示装置であって、光リーク電流の発生を抑えつつ、容量増加をも抑制することができる表示装置を提供。

【解決手段】TFTの少なくとも一端において、ソース領域やドレイン領域となる高濃度領域と、チャネル領域との間に、順に、高濃度領域の不純物濃度が低濃度の第1低濃度領域と、第1低濃度領域の不純物濃度よりさらに低濃度の第2低濃度領域とを、設ける。

(もっと読む)

高耐圧半導体装置および駆動回路

【課題】スイッチング応答速度が速い高耐圧トランジスタ、および電力損失および誤動作を抑制した駆動回路を提供すること。

【解決手段】高耐圧半導体装置は、p-型シリコン基板100上に設けられ、かつp-ウエル領域102に囲まれたn-型領域101と、ドレイン電極120と接続されるドレインn+領域103と、ドレインn+領域103と離れて設けられ、かつドレインn+領域103を囲むpベース領域105と、pベース領域105内に形成されたソースn+領域114と、を備える。また、n-型領域101を貫通し、かつシリコン基板100に達するp-領域131が設けられている。n-型領域101は、p-領域131により、n-型領域101aとn-型領域101bに分離されている。n-型領域101aは、ドレインn+領域103を備えている。n-型領域101bは、フローティング電位を有する。

(もっと読む)

半導体装置およびその作製方法

【課題】特性の良い光電変換素子を有する半導体装置を提供することを目的の一とする。または、簡単な工程で、特性の良い光センサ光電変換装置を有する半導体装置を提供することを目的の一とする。

【解決手段】光透過性を有する基板と、光透過性を有する基板上の絶縁層と、絶縁層上の、光電変換を奏する半導体領域、第1の導電型を示す半導体領域、および、第2の導電型を示す半導体領域を有する単結晶半導体層と、第1の導電型を示す半導体領域と電気的に接続された第1の電極と、第2の導電型を示す半導体領域と電気的に接続された第2の電極とを有する光電変換素子とを備える半導体装置を提供する。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】画素、メモリ部、又はCMOS回路等に配置されたトランジスタのチャネル形成領域213、214と重なる第1の配線(ゲート電極)の一部または全部と第2の配線(ソース線またはドレイン線)154、157とを重ねる。また、ゲート電極と第2配線154、157の間には第1の層間絶縁膜149及び第2の層間絶縁膜150cを設け、寄生容量を低減した半導体装置である。

(もっと読む)

集積回路

第1の絶縁層と、半導体層と、この半導体層に近オーミックまたはオーミック接触している第1の導体層と、第1の絶縁層によって半導体層から隔てられた第2の導体層であって、複数のトランジスタを備えた複数の機能ブロックを生成するために第1および第2の導体層はパターン化され、第1の層の導体はソース/ドレイン電極として機能し、第2の層の導体はゲート電極として機能する、第1および第2の導体層と、を備える集積回路であって、各機能ブロックは対応する半導体層の島を備え、この島は第2の絶縁層の複数の部分によって別の機能ブロックの島から隔離され、各機能ブロックは、(i)異なるトランジスタの相互に隣接するソース/ドレイン電極が同じ電位になるように配置され、かつ(ii)上記隣接する電極間に一切の導体が存在しないように配置される、集積回路。 (もっと読む)

半導体装置及びその製造方法

【課題】 ゲートとドレインの間で生じる電界集中を緩和する半導体装置を提供する。

【解決手段】本発明によれば,半導体基板上にゲート絶縁膜を介して形成された第1のゲート電極と、前記半導体基板上に前記ゲート絶縁膜を介して形成され、かつ、第1のゲート電極の側面に絶縁性のスペーサを介して配置された第2のゲート電極と、第1及び第2のゲート電極を挟むように前記半導体基板上に形成されたソース領域及びドレイン領域と、第1のゲート電極下方における前記半導体基板の一部の領域を挟むように形成され、第2のゲート電極及び前記ソース領域及びドレイン領域と重なるように形成された電界緩和領域と、を備える半導体装置が提供される。

(もっと読む)

半導体装置及びその作製方法

【課題】 信頼性の高いTFT構造を用いた半導体装置を実現する。

【解決手段】 TFTに利用する絶縁膜、例えばゲート絶縁膜、保護膜、下地膜、層間絶縁膜等として、ボロンを含む窒化酸化珪素膜(SiNX BY OZ )をスパッタ法で形成する。その結果、この膜の内部応力は、代表的には−5ラ1010dyn/cm2 〜5ラ1010dyn/cm2 、好ましくは−1010dyn/cm2 〜1010dyn/cm2 となり、高い熱伝導性を有するため、TFTのオン動作時に発生する熱による劣化を防ぐことが可能となった。

(もっと読む)

半導体装置及び電子機器

【課題】カラーフィルタに含まれる不純物による汚染の問題を解決する。

【解決手段】薄膜トランジスタと、薄膜トランジスタに電気的に接続されるソース電極及びドレイン電極と、薄膜トランジスタ、ソース電極及びドレイン電極上の第1の絶縁膜と、第1の絶縁膜上のカラーフィルタと、カラーフィルタ上の第2の絶縁膜と、第2の絶縁膜上の画素電極とを有し、第1の絶縁膜は窒化シリコンを有し、カラーフィルタは第1の開口部を有し、第2の絶縁膜は第2の開口部を有し、第2の開口部は第1の開口部の内側に設けられ、画素電極は、第1の開口部及び第2の開口部を介してソース電極及びドレイン電極の一方に電気的に接続され、カラーフィルタは、画素電極、ソース電極及びドレイン電極に接触しない。

(もっと読む)

半導体装置

【課題】SOI基板に形成されたMOSトランジスタの高耐圧化、低消費電流、かつ高速動作を実現する。

【解決手段】シリコン層1cに、埋め込み酸化膜1bに達する深さで、N型の低濃度ドレイン領域3、ソース領域5、ドレインオーミック領域7、及びP型のチャンネル領域9、オーミックチャンネル領域11が形成されている。低濃度ドレイン領域3は表面側に配置されているものほど濃いN型不純物濃度をもつ2層の低濃度ドレイン層3a,3bで形成されている。チャンネル領域9は表面側に配置されているものほど薄いP型不純物濃度をもつ2層のチャンネル層9a,9bで形成されている。ゲート電極15は、チャンネル領域9上と低濃度ドレイン領域3の一部分の上に、上方から見てオーミックドレイン領域7とは間隔をもって配置されている。

(もっと読む)

半導体装置の作製方法

【課題】 信頼性の高いTFT構造を用いた半導体装置を実現する。

【解決手段】 TFTに利用する絶縁膜、例えばゲート絶縁膜、保護膜、下地膜、層間絶縁膜等として、ボロンを含む窒化酸化珪素膜(SiNX BY OZ )をスパッタ法で形成する。その結果、この膜の内部応力は、代表的には−5×1010dyn/cm2 〜5×1010dyn/cm2 、好ましくは−1010dyn/cm2 〜1010dyn/cm2 となり、高い熱伝導性を有するため、TFTのオン動作時に発生する熱による劣化を防ぐことが可能となった。

(もっと読む)

半導体装置

【課題】各種回路に配置される薄膜トランジスタの構造を、回路の機能に応じて適切なものとすることにより、半導体装置の動作特性および信頼性を向上させ、かつ、低消費電力化を図ると共に、工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的とする。

【解決手段】薄膜トランジスタのLDD領域を、テーパー部を有するゲート電極及びテーパー部を有するゲート絶縁膜に対応させて設ける。具体的には、第1のLDD領域はゲート電極のテーパー部の下に設けられ、第2のLDD領域はゲート絶縁膜のテーパー部の下に設けられる。

(もっと読む)

半導体装置および電子機器

【課題】高速動作に適したN型層を用いたN型TFTを液晶容量と、蓄積容量の充電に用いる場合には、リーク電流特性に劣るN型層を蓄積容量に用いることとなり、電荷保持特性が低下するという課題がある。またP型層を用いたP型TFTを液晶容量と、蓄積容量の充電に用いた場合には、P型TFTがN型TFTと比べ移動度が低いことから高速動作が困難となり、TFTによるスイッチング特性が劣化するという課題がある。

【解決手段】N型TFT90をスイッチングに用い、P型電極層41を保持容量として用い、かつP延展部40と、N型ドレイン側延展部1tとを切り離すことなく形成した。P延展部40と、N型ドレイン側延展部1tとの間には段差はなく、コンタクトホール94を形成するためのエッチング工程を均一な層厚を備えた第1層間絶縁層4に対して行うことができ、エッチングむら等による電気抵抗の増加を防止することが可能となる。

(もっと読む)

薄膜トランジスタ及び表示装置

【課題】半導体層をゲート電極によって遮光したボトムゲート型薄膜トランジスタのオフ電流を低減する。

【解決手段】ゲート電極層と、第1の半導体層と、前記第1の半導体層上に接して設けられた前記第1の半導体層よりもキャリア移動度が低い第2の半導体層と、前記ゲート電極層と前記第1の半導体層との間に接して設けられたゲート絶縁層と、前記第2の半導体層に接して設けられた不純物半導体層と、前記不純物半導体層及び前記第1及び第2の半導体層に一部が接して設けられたソース電極及びドレイン電極層と、を有し、前記第1の半導体層のゲート電極層側は全面が前記ゲート電極層によって覆われており、前記第1の半導体層と前記ソース電極及びドレイン電極層が接する部分のポテンシャル障壁は0.5eV以上である薄膜トランジスタを提供する。

(もっと読む)

81 - 100 / 250

[ Back to top ]